## **ESD Protector**

## **Description**

The DESDWC2D50S protects sensitive semiconductor components from damage or upset due to electrostatic discharge (ESD) and other voltage induced transient events. They feature large cross-sectional area junctions for conducting high transient currents, offer desirable electrical characteristics for board level protection, such as fast response time, low operating voltage. It gives designer the flexibility to protect one bi-directional line in applications where arrays are not practical.

#### **Feature**

- 80W peak pulse power per line ( $t_P$  = 8/20 $\mu$ s)

- DFN1006-2L package

- Replacement for MLV(0402)

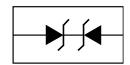

- Bidirectional configurations

- Response time is typically < 1ns

- High ESD protection

- Low clamping voltage

- RoHS compliant

- Transient protection for data lines to IEC61000-4-2(ESD) ±15KV(air), ±8KV(contact)

## **Applications**

- Cellular phones

- Portable devices

- Digital cameras

- Power supplies

#### **Mechanical Characteristics**

- Lead finish:100% matte Sn(Tin)

- Mounting position: Any

- Qualified max reflow temperature:260°C

- Device meets MSL 1 requirements

- Pure tin plating: 7 ~ 17 um

- Pin flatness:≤3mil

#### **Electronics Parameter**

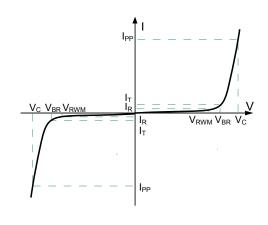

| Symbol          | Parameter                                  |  |  |  |

|-----------------|--------------------------------------------|--|--|--|

| $V_{RWM}$       | Peak Reverse Working Voltage               |  |  |  |

| I <sub>R</sub>  | Reverse Leakage Current @ V <sub>RWM</sub> |  |  |  |

| $V_{BR}$        | Breakdown Voltage @ I <sub>⊺</sub>         |  |  |  |

| I <sub>T</sub>  | Test Current                               |  |  |  |

| I <sub>PP</sub> | Maximum Reverse Peak Pulse Current         |  |  |  |

| V <sub>C</sub>  | Clamping Voltage @ I <sub>PP</sub>         |  |  |  |

| P <sub>PP</sub> | Peak Pulse Power                           |  |  |  |

| CJ              | Junction Capacitance                       |  |  |  |

| I <sub>F</sub>  | Forward Current                            |  |  |  |

| V <sub>F</sub>  | Forward Voltage @ I <sub>F</sub>           |  |  |  |

## **ESD Protector**

## Electrical characteristics per line@25°C (unless otherwise specified)

| Parameter                    | Symbol         | Conditions                   | Min. | Тур. | Max. | Units |

|------------------------------|----------------|------------------------------|------|------|------|-------|

| Peak Reverse Working Voltage | $V_{RWM}$      |                              |      |      | 5    | V     |

| Breakdown Voltage            | $V_{BR}$       | I <sub>t</sub> = 1mA         | 5.6  | 6.7  | 7.8  | V     |

| Reverse Leakage Current      | I <sub>R</sub> | V <sub>RWM</sub> = 5V T=25°C |      |      | 1.0  | μΑ    |

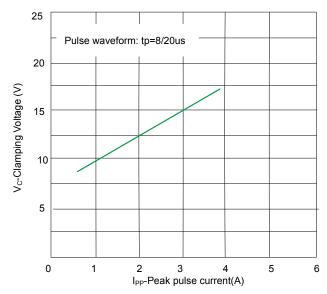

| Clamping Voltage             | Vc             | I <sub>PP</sub> =1A          |      |      | 9    | V     |

| Clamping Voltage             | V <sub>C</sub> | I <sub>PP</sub> =3A          |      |      | 12   | V     |

| Clamping Voltage             | V <sub>C</sub> | I <sub>PP</sub> =5A          |      |      | 15   | V     |

| Junction Capacitance         | C <sub>j</sub> | V <sub>R</sub> =0V f = 1MHz  |      | 1    |      | pF    |

## Absolute maximum rating@25°C

| Rating                                    | Symbol           | Value       | Units |

|-------------------------------------------|------------------|-------------|-------|

| Peak Pulse Power (t <sub>p</sub> =8/20µs) | P <sub>pp</sub>  | 80          | W     |

| Operating Temperature                     | TJ               | -55 to +150 | °C    |

| Storage Temperature                       | T <sub>STG</sub> | -55 to +150 | °C    |

# Typical Characteristics

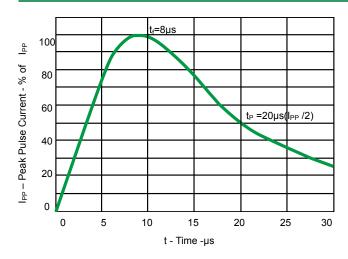

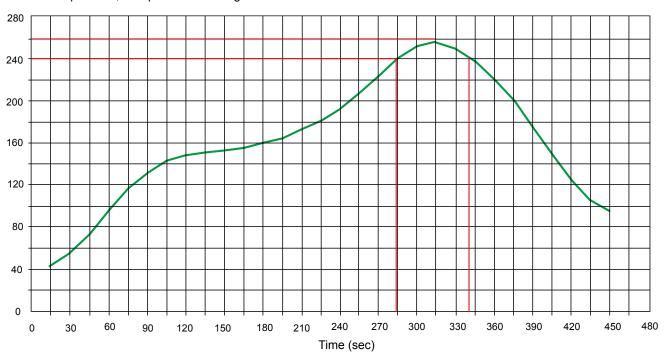

Fig 1.Pulse Waveform

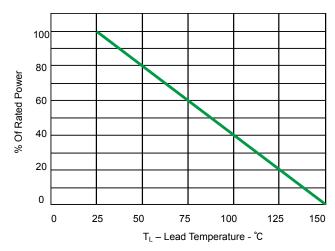

Fig 2.Power Derating Curve

## **ESD Protector**

Fig 3. Clamping voltage vs. Peak pulse current

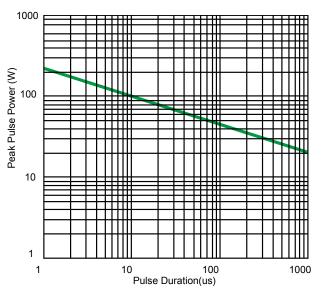

Fig 4. Non Repetitive Peak Pulse Power vs. Pulse time

## **Solder Reflow Recommendation**

Peak Temp=257°C, Ramp Rate=0.802deg. °C/sec

## **PCB** Design

For TVS diodes a low-ohmic and low-inductive path to chassis earth is absolutely mandatory in order to achieve good ESD protection. Novices in the area of ESD protection should take following suggestions to heart:

- Do not use stubs, but place the cathode of the TVS diode directly on the signal trace.

- > Do not make false economies and save copper for the ground connection.

- > Place via holes to ground as close as possible to the anode of the TVS diode.

- Use as many via holes as possible for the ground connection.

- Keep the length of via holes in mind! The longer the more inductance they will have.

# **ESD Protector**

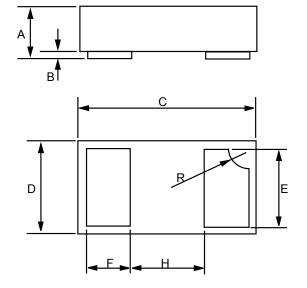

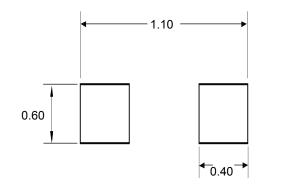

## **Product dimension (DFN1006-2L)**

| Dim | Incl      | hes   | Millimeters |       |  |

|-----|-----------|-------|-------------|-------|--|

|     | MIN       | MAX   | MIN         | MAX   |  |

| Α   | 0.013     | 0.015 | 0.34        | 0.40  |  |

| В   | 0.000     | 0.002 | 0.00        | 0.05  |  |

| С   | 0.037     | 0.042 | 0.95        | 1.075 |  |

| D   | 0.021     | 0.026 | 0.55        | 0.675 |  |

| E   | 0.017     | 0.021 | 0.45        | 0.55  |  |

| F   | 0.007     | 0.011 | 0.20        | 0.30  |  |

| Н   | 0.015Typ. |       | 0.40        | Tyo.  |  |

| R   | 0.001     | 0.005 | 0.05        | 0.15  |  |

Unit:mm