#### **Applications**

- · Commercial and military radar

- Communications

- Electronic Warfare

#### **Product Features**

Frequency Range: 0.1 – 3.0GHz

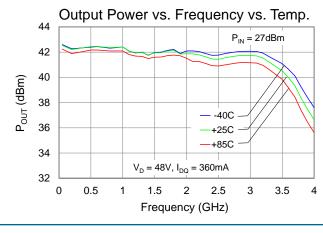

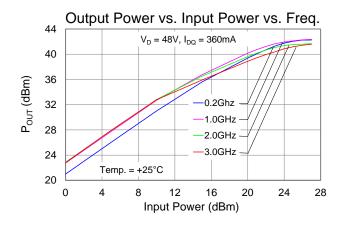

P<sub>SAT</sub>: 41dBm at P<sub>IN</sub> = 27dBm

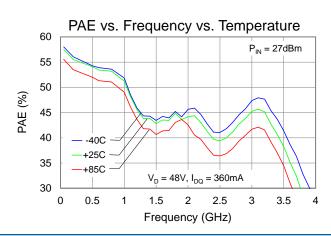

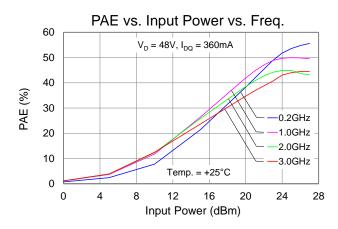

P1dB: >34dBmPAE: >40%

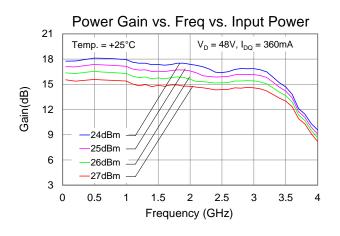

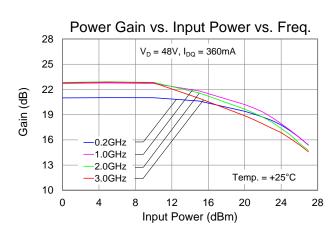

Large Signal Gain: 14dBSmall Signal Gain: 22dB

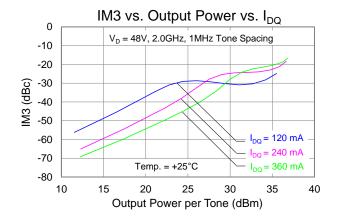

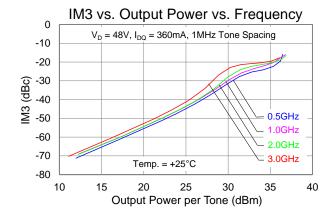

IM3 @ 120mA POUT< 33dBm/tone: -30dBc</li>

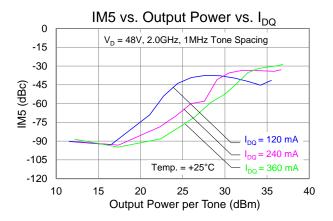

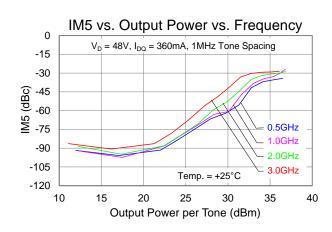

IM5 @ 120mA POUT< 33dBm/tone: -35dBc</li>

• Bias:  $V_D = 48V$ ,  $I_{DQ} = 360mA$ ,  $V_{G1} = -2.3V$  Typical,  $V_{G2} = +21.7V$  Typical

· Wideband Flat Gain and Power

Chip Dimensions: 1.8 x 1.8 x 0.10 mm

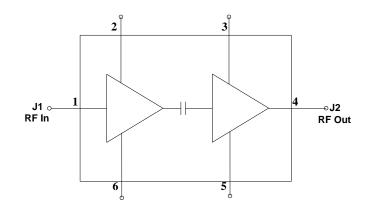

#### **Functional Block Diagram**

### **General Description**

TriQuint's TGA2216 is a wideband cascode amplifier fabricated on TriQuint's production 0.25um GaN on SiC process. The cascode configuration offers exceptional wideband performance as well as supporting 48V operation. The TGA2216 operates from 0.1 - 3.0GHz and provides 12W of saturated output power with 14dB of large signal gain and greater than 40% power-added efficiency.

The broadband performance supports both radar and communication applications across defense and commercial markets as well as electronic warfare. The TGA2216 is fully matched to  $50\Omega$  at both RF ports allowing for simple system integration. DC blocks are required on both RF ports and the drain voltage must be injected through an off chip bias-tee on the RF output port.

Lead-free and RoHS compliant.

Evaluation boards are available upon request.

### **Pad Configuration**

| Pad No. | Symbol                 |

|---------|------------------------|

| 1       | RF In, VG1             |

| 2, 6    | V <sub>G1</sub>        |

| 3, 5    | V <sub>G2</sub>        |

| 4       | RF Out, V <sub>D</sub> |

# **Ordering Information**

| Part    | <b>ECCN</b> | Description                             |

|---------|-------------|-----------------------------------------|

| TGA2216 | EAR99       | 0.1 – 3.0GHz 12W<br>GaN Power Amplifier |

Preliminary Datasheet: Rev A 10-15-15 © 2015 TriQuint

### **Absolute Maximum Ratings**

| Parameter                                                   | Value        |  |  |

|-------------------------------------------------------------|--------------|--|--|

| Drain Voltage (V <sub>D</sub> )                             | 80V          |  |  |

| Gate Voltage Range (V <sub>G1</sub> )                       | -8 to 0V     |  |  |

| Gate Voltage Range (V <sub>G2</sub> )                       | 0 to 40V     |  |  |

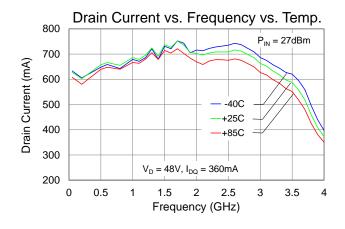

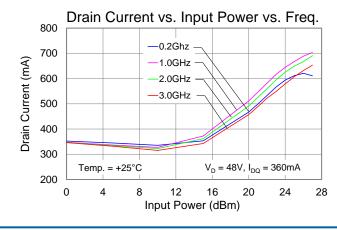

| Drain Current (I <sub>D</sub> )                             | 760mA        |  |  |

| Gate Current (I <sub>G1</sub> )                             | -5 to 5.6mA  |  |  |

| Gate Current (I <sub>G2</sub> )                             | -5 to 5.6mA  |  |  |

| Power Dissipation (P <sub>DISS</sub> ), 85°C                | 28W          |  |  |

| Input Power ( $P_{IN}$ ), CW, 50 $\Omega$ , 85°C,           | 33dBm        |  |  |

| Input Power ( $P_{IN}$ ), CW, VSWR 10:1, $V_D = 48V$ , 85°C | 30dBm        |  |  |

| Channel Temperature (T <sub>CH</sub> )                      | 275°C        |  |  |

| Mounting Temperature (30 Seconds)                           | 320°C        |  |  |

| Storage Temperature                                         | -55 to 150°C |  |  |

Operation of this device outside the parameter ranges given above may cause permanent damage. These are stress ratings only, and functional operation of the device at these conditions is not implied.

## **Recommended Operating Conditions**

| Parameter                                            | Value         |

|------------------------------------------------------|---------------|

| Drain Voltage (V <sub>D</sub> )                      | 48V           |

| Drain Current (I <sub>DQ</sub> )                     | 360mA         |

| Drain Current Under RF Drive (I <sub>D_Drive</sub> ) | 710mA         |

| Gate Voltage (V <sub>G1</sub> )                      | -2.3V (Typ.)  |

| Gate Voltage (V <sub>G2</sub> )                      | +21.7V (Typ.) |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

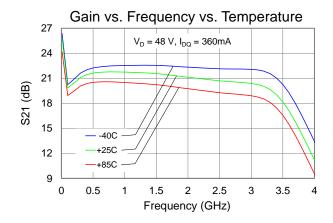

## **Electrical Specifications**

Test conditions unless otherwise noted:  $25^{\circ}$ C,  $V_D = 48$ V,  $I_{DQ} = 360$ mA,  $V_{G1} = -2.3$ V Typical,  $V_{G2} = +21.7$ V Typical

| Parameter                                 | Min | Typical       | Max | Units  |

|-------------------------------------------|-----|---------------|-----|--------|

| Operational Frequency Range               | 0.1 |               | 3.0 | GHz    |

| Small Signal Gain                         |     | 22            |     | dB     |

| Input Return Loss                         |     | 10 (mid band) |     | dB     |

| Output Return Loss                        |     | 10 (mid band) |     | dB     |

| Output Power (Pin = 27dBm)                |     | 41            |     | dBm    |

| Power Added Efficiency (Pin = 27dBm)      |     | > 40          |     | %      |

| Power @ 1dB Compression (P1dB)            |     | > 34          |     | dB     |

| IM3 @ 120mA POUT/Tone < 33dBm             |     | -30           |     | dBc    |

| IM5 @ 120mA Pout/Tone < 33dBm             |     | -35           |     | dBc    |

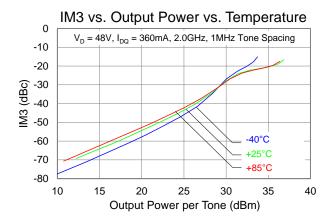

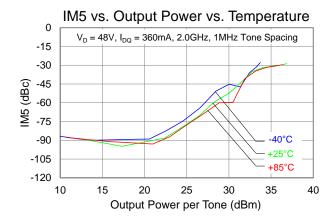

| Small Signal Gain Temperature Coefficient |     | -0.02         |     | dB/°C  |

| Output Power Temperature Coefficient      |     | -0.005        |     | dBm/°C |

| Recommended Operating Voltage:            | 40  | 48            | 50  | V      |

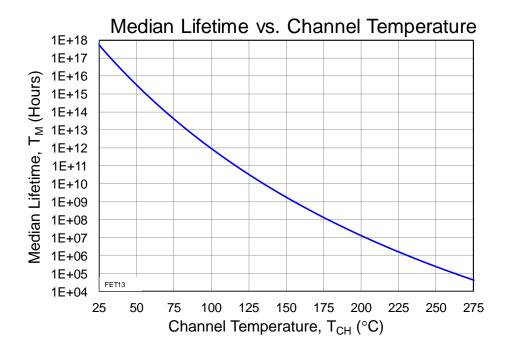

| Thermal and Reliability Information |

|-------------------------------------|

|-------------------------------------|

| Parameter                                               | Test Conditions                                                                                                  | Value       | Units |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------|-------|

| Thermal Resistance (θ <sub>JC</sub> ) <sup>(1)</sup>    | $T_{\text{base}} = 85^{\circ}\text{C}, \ V_{\text{D}}^{(2)} = 40\text{V}, \ I_{\text{DQ}} = 360\text{mA}$        | 6.56        | °C/W  |

| Channel Temperature (T <sub>CH</sub> ) (Under RF drive) | $T_{\text{base}} = 85^{\circ}\text{C}, V_{D}^{(2)} = 40\text{V}, I_{D\_Drive} = 635\text{mA}, Pout$              | 183         | °C    |

| Median Lifetime (T <sub>M</sub> )                       | $= 40$ dBm, $P_{DISS} = 15$ W                                                                                    | 6 x 10^8    | Hrs   |

|                                                         |                                                                                                                  |             |       |

| Thermal Resistance (θ <sub>JC</sub> ) <sup>(1)</sup>    | $T_{\text{base}} = 85^{\circ}\text{C}, V_{\text{D}}^{(2)} = 48\text{V}, I_{\text{DQ}} = 360\text{mA},$           | 6.85        | °C/W  |

| Channel Temperature (T <sub>CH</sub> ) (Under RF drive) | $T_{\text{base}} = 85^{\circ}\text{C}, V_{\text{D}}^{(2)} = 48\text{V}, I_{\text{D_Drive}} = 675\text{mA}, Pout$ | 222         | °C    |

| Median Lifetime (T <sub>M</sub> )                       | = 40.8dBm, P <sub>DISS</sub> = 20W                                                                               | 1.99 x 10^6 | Hrs   |

#### Notes:

- 1. Thermal resistance measured to back of carrier plate. MMIC mounted on 40 mils CuMo (80/20) carrier using 1.5 mil AuSn.

- 2. The drain voltage for Cascode amplifier transistor is  $\frac{1}{2}$  of the  $V_{D}$

## **Median Lifetime**

Test Conditions:  $V_D = 40 \text{ V}$ ; Failure Criteria = 10% reduction in  $I_{D \text{ MAX}}$

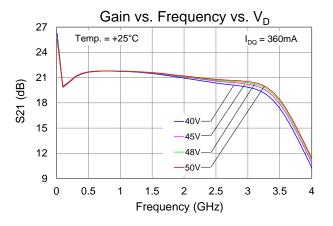

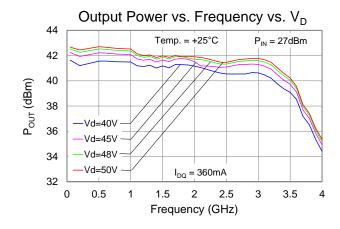

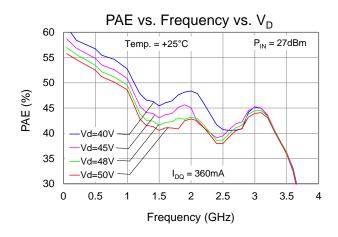

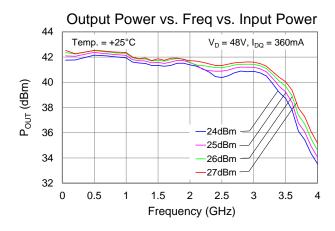

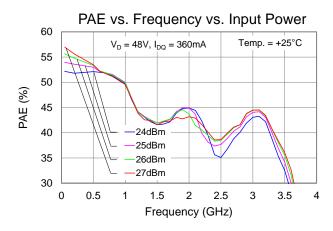

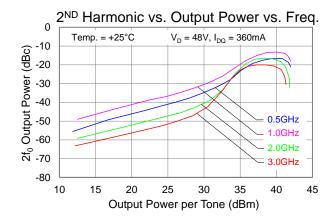

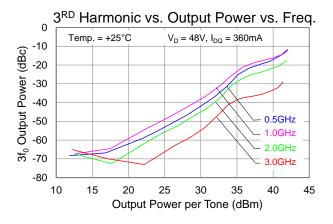

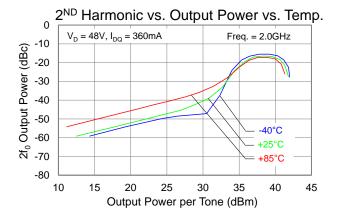

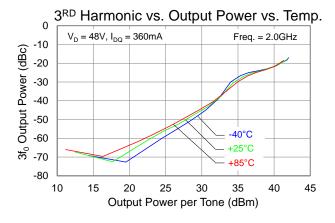

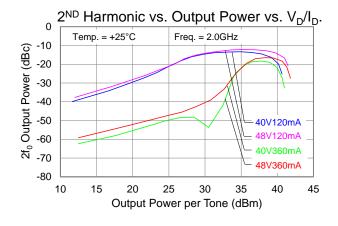

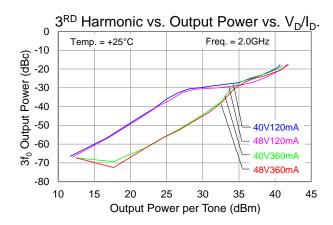

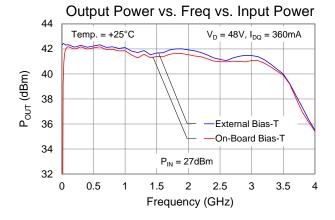

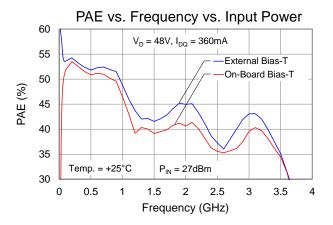

The plots reflect performance measured with an external coaxial bias tee and DC blocks (See application circuit on page 10)

Preliminary Datasheet: Rev A 10-15-15 © 2015 TriQuint

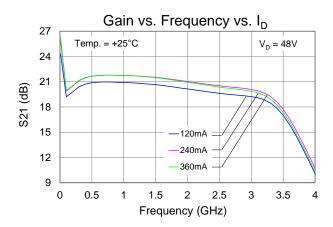

The plots reflect performance measured with an external coaxial bias tee and DC blocks (See application circuit on page 10)

Preliminary Datasheet: Rev A 10-15-15 © 2015 TriQuint

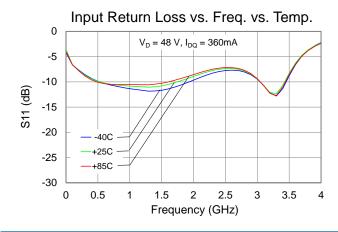

The plots reflect performance measured with an external coaxial bias tee and DC blocks (See application circuit on page 10)

Preliminary Datasheet: Rev A 10-15-15 © 2015 TriQuint

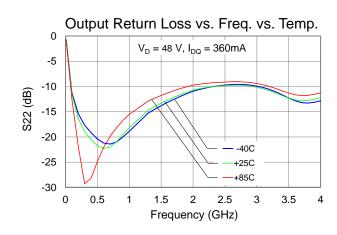

The plots reflect performance measured with an external coaxial bias tee and DC blocks (See application circuit on page 10)

The plots reflect performance measured with an external coaxial bias tee and DC blocks (See application circuit on page 10)

The plots below reflect performance measured between external bias tee and on-board bias tee (See application circuit on pages 10 and 12)

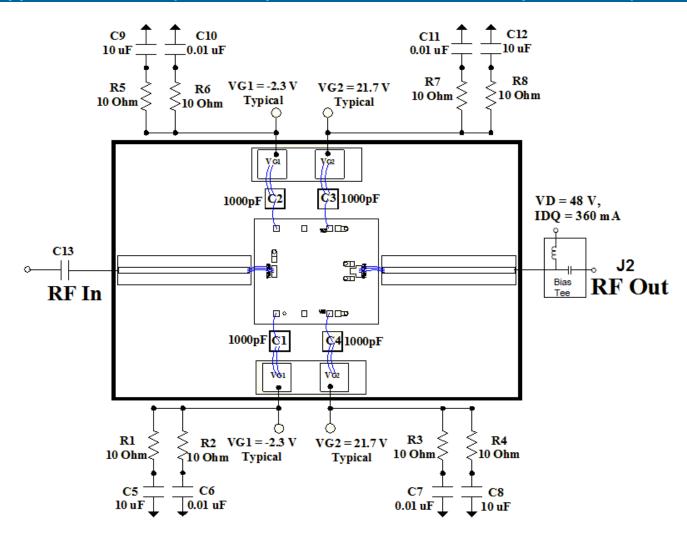

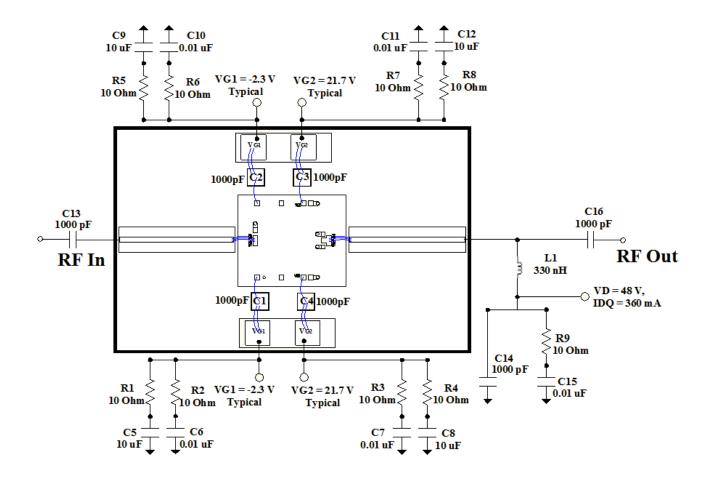

## Application Circuit (Coaxial input DC block and coaxial output bias tee)

#### Notes:

- 1. Vg1 & Vg2 can be biased from either side (Top or Bottom.)

- 2. Coaxial input DC block (C13) is used for input port (RF In.)

- 3. External wide bandwidth Bias-Tee is used for output port (RF Out). VD is applied through the output Bias-Tee.

### **Bias-up Procedure**

- 1. Set  $I_D$  limit to 720mA,  $I_{G1\ \&}\ I_{G2}$  limit to 5mA

- 2. Set V<sub>G1</sub> to -5.0V

- 3. Set  $V_{G2}$  to (VD/2) 2.7V or 48V/2 2.7V = 21.3V

- 4. Set VD +48V

- 5. Adjust  $V_{G1}$  more positive until  $I_{DQ}$  = 360mA ( $V_{G1} \sim$  2.3V Typical)

- 6. Adjust VG2 to (VD/2) + VG1;  $(V_{G2} \sim 21.7V \text{ Typical})$

- 7. Apply RF signal

#### **Bias-down Procedure**

- 1. Turn off RF signal

- 2. Reduce  $V_{G1}$  to -5.0V. Ensure  $I_{DQ} \sim 0 mA$

- 3. Reduce  $V_{G2}$  to 0V.

- 4. Set V<sub>D</sub> to 0V

- 5. Turn off V<sub>D</sub> supply

- 6. Turn off V<sub>G2</sub> supply

- 7. Turn off V<sub>G1</sub> supply

Preliminary Datasheet: Rev A 10-15-15 © 2015 TriQuint

- 10 of 16 -

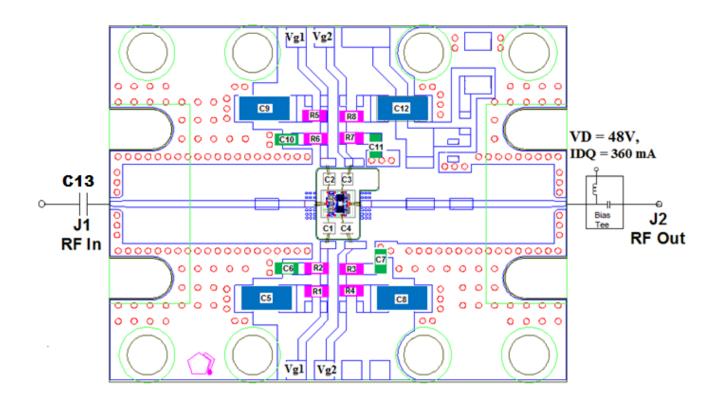

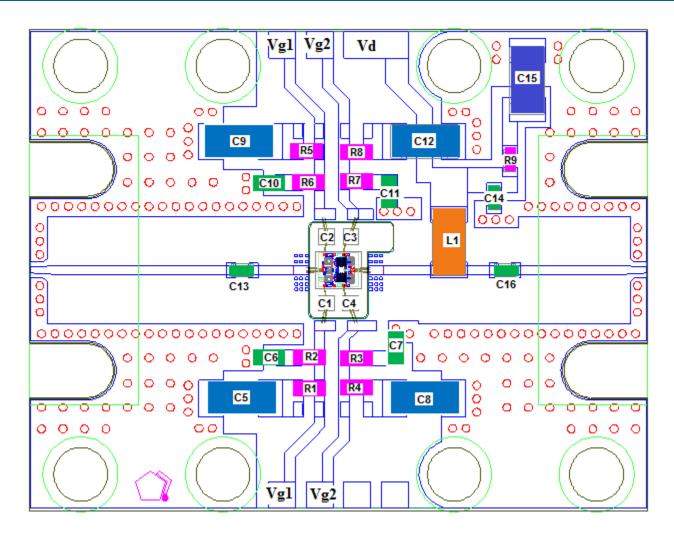

# Assembly Drawing (Coaxial input DC block and coaxial output bias tee)

## **Bill of Materials**

| Reference Design | Value  | Description              | Manufacturer | Part Number |

|------------------|--------|--------------------------|--------------|-------------|

| C1 – C4          | 1000pF | SLC, 50V                 | Various      |             |

| C5, C8, C9, C12  | 10uF   | Cap, 1206, 50V, 10%, X7R | Various      |             |

| C6, C7, C10, C11 | 0.01uF | Cap, 0402, 50V, 10%, X7R | Various      |             |

| C13              |        | DC Block                 | Various      |             |

| R1 – R8          | 10Ω    | Res, 0402                | Various      |             |

# Application Circuit (Option with board-level DC blocks and output bias tee)

#### Notes:

- 1. Performance of the MMIC with surface mount DC blocks and bias tee components may be degraded relative to the coaxial option. These components should be optimized for the desired operational bandwidth.

- 2.  $V_{G1}$  &  $V_{G2}$  can be biased from either side (Top or Bottom.)

# **Evaluation Board Layout with On-Board DC Blocks and Output Bias-T Option**

#### Bill of Materials For On-Board Bias-Tee

| Reference Design | Value  | Description               | Manufacturer | Part Number |

|------------------|--------|---------------------------|--------------|-------------|

| C13, C14, C16    | 1000pF | Cap, 0402, 100V, 10%, X7R | Various      |             |

| C15              | 0.01uF | Cap, 1206, 100V, 10%, X7R | Various      |             |

| L1               | 330nH  | Ind, 1206, 100V, 10%, X7R | Various      |             |

| R9               | 10Ω    | Res, 0402                 | Various      |             |

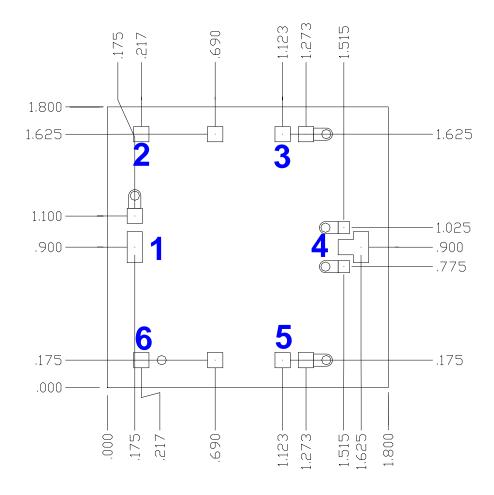

## **Mechanical Drawing & Bond Pad Description**

Unit: millimeters Thickness: 0.10

Die x, y size tolerance:  $\pm -0.050$

Chip edge to bond pad dimensions are shown to center of pad

Ground is backside of die

| <b>Bond Pad</b> | Symbol     | Pad Size      | Description                                                                                                |

|-----------------|------------|---------------|------------------------------------------------------------------------------------------------------------|

| 1               | RF In/ VG1 | 0.098 x 0.198 | RF Input; VG1 gate voltage is present here, DC block is required.                                          |

| 2, 6            | VG1        | 0.098 x 0.098 | Gate voltage 1, bias network is required; see Application Circuit on pages 10 and 12 as an example.        |

| 3, 5            | VG2        | 0.098 x 0.098 | Gate voltage 2, bias network is required; see Application Circuit on pages 10 and 12 as an example.        |

| 4               | RF Out/ VD | 0.098 x 0.198 | Output; Drain voltage, bias network is required; see Application Circuit on pages 10 and 12 as an example. |

#### **Assembly Notes**

Component placement and adhesive attachment assembly notes:

- · Vacuum pencils and/or vacuum collets are the preferred method of pick up.

- · Air bridges must be avoided during placement.

- The force impact is critical during auto placement.

- Organic attachment (i.e. epoxy) can be used in low-power applications.

- Curing should be done in a convection oven; proper exhaust is a safety concern.

#### Reflow process assembly notes:

- Use AuSn (80/20) solder and limit exposure to temperatures above 300°C to 3-4 minutes, maximum.

- · An alloy station or conveyor furnace with reducing atmosphere should be used.

- · Do not use any kind of flux.

- Coefficient of thermal expansion matching is critical for long-term reliability.

- Devices must be stored in a dry nitrogen atmosphere.

#### Interconnect process assembly notes:

- Thermosonic ball bonding is the preferred interconnect technique.

- Force, time, and ultrasonic are critical parameters.

- · Aluminum wire should not be used.

- Devices with small pad sizes should be bonded with 0.0007-inch wire.