#### **Product Description**

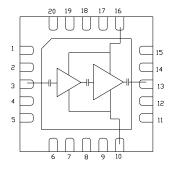

Qorvo's TGA2611-SM is a packaged broadband Low Noise Amplifier fabricated on Qorvo's QGaN25 0.25 um GaN on SiC process. The TGA2611-SM operates from 2 to 6 GHz and typically provides >18 dBm P1dB, >22 dB of small signal gain and 30 dBm of OTOI with 1.0 dB NF. In addition to the high overall electrical performance, this GaN amplifier also provides a high level of input power robustness which allows more flexibility in designing the receive chain circuit protection.

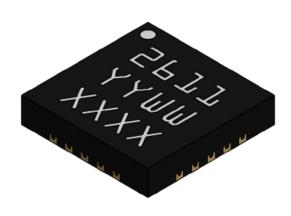

The TGA2611-SM is available in a low cost, surface mount 20-lead 4x4 mm plastic QFN. It is ideally suited to support both radar and satellite communication applications.

Both RF ports have intergraded DC blocking caps and are fully matched to 50 ohms.

Lead-Free and RoHS compliant.

Evaluation boards are available upon request.

#### **Product Features**

• Frequency Range: 2-6 GHz

• NF: 1.0 dB

• OTOI: 30 dBm @ Pout/Tone = 18 dBm

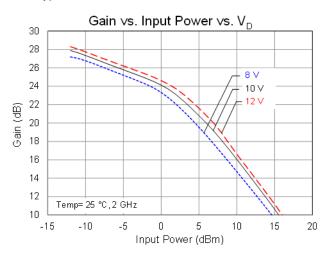

Small Signal Gain: 22 dB

• Return Loss: > 10 dB

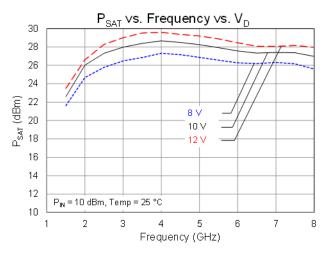

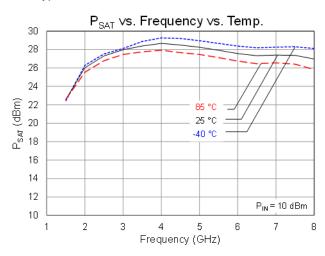

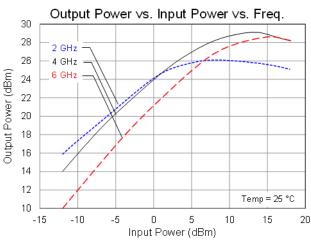

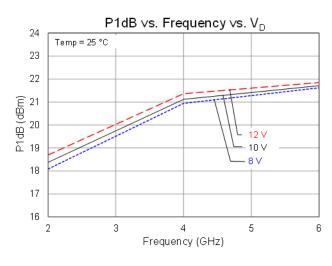

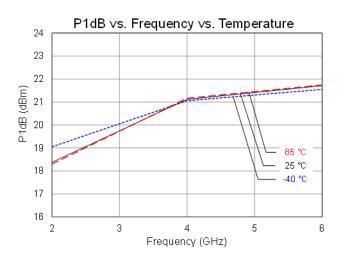

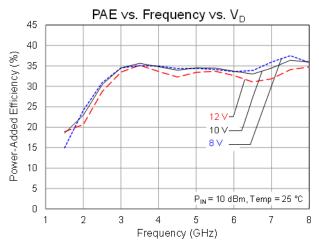

• P1dB: 18 dBm; P<sub>SAT</sub> = 26 dBm @ P<sub>IN</sub> = 10 dBm

• Bias:  $V_D = 10 \text{ V}$ ,  $I_{DQ} = 100 \text{ mA}$ ;  $V_G = -2.3 \text{ V}$  (Typical)

• Package Dimensions: 4.0 x 4.0 x 0.85 mm

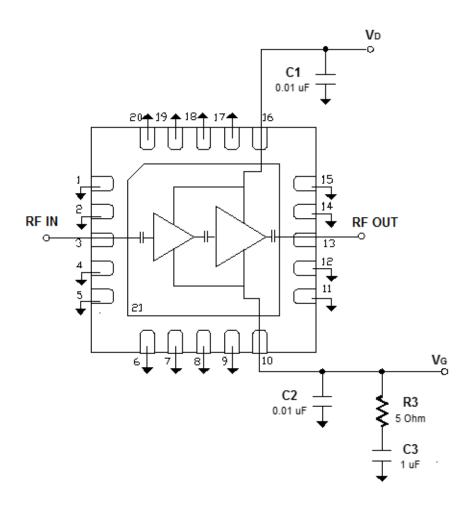

### **Functional Block Diagram**

# **Applications**

- Commercial & Military Radar

- Communications

### **Ordering Information**

| Part No.   | ECCN  | Description     |

|------------|-------|-----------------|

| TGA2611-SM | EAR99 | 2-6 GHz GaN LNA |

# TGA2611-SM 2-6 GHz GaN LNA

#### **Absolute Maximum Ratings**

| Parameter                                     | Range / Value          | Units |

|-----------------------------------------------|------------------------|-------|

| Drain Voltage (V <sub>D</sub> )               | +40                    | V     |

| Gate Voltage (V <sub>G</sub> )                | −5 to 0                | V     |

| Drain Current (I <sub>D</sub> )               | 300                    | mA    |

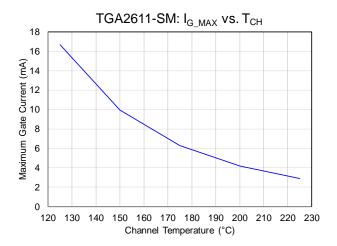

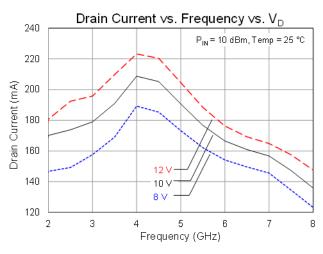

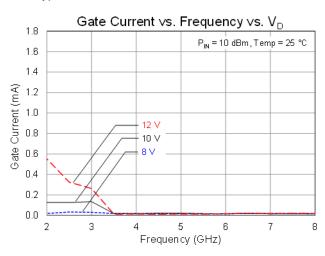

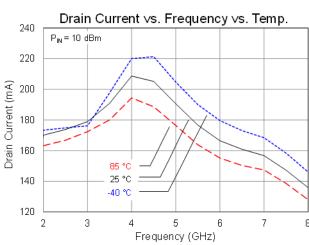

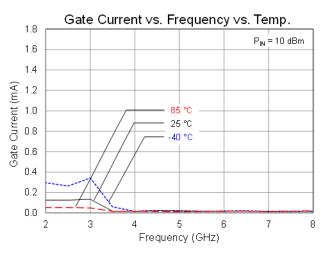

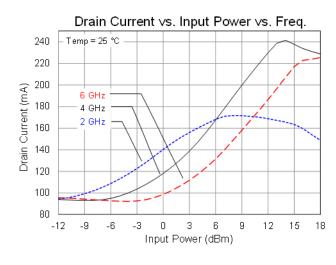

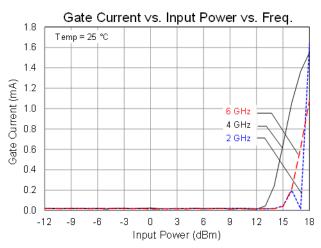

| Gate Current (I <sub>G</sub> )                | See graph on page<br>3 | _     |

| Power Dissipation, 85 °C (P <sub>DISS</sub> ) | 6                      | W     |

| RF Input Power, CW, 50 Ω                      | 30                     | dBm   |

| Channel Temperature (T <sub>CH</sub> )        | +275                   | °C    |

| Mounting Temperature (30 seconds maximum)     | +260                   | °C    |

| Storage Temperature                           | −55 to +150            | °C    |

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability.

#### **Recommended Operating Conditions**

| Parameter                        |                |  |  |  |

|----------------------------------|----------------|--|--|--|

| Drain Voltage (V <sub>D</sub> )  | 10 V           |  |  |  |

| Gate Voltage (V <sub>G</sub> )   | -2.3 V Typical |  |  |  |

| Quiescent Drain Current (IDQ)    | 100 mA         |  |  |  |

| Temperature (T <sub>BASE</sub> ) | -40 to 85 °C   |  |  |  |

Electrical performance is measured under conditions noted in the electrical specifications table. Specifications are not guaranteed over all recommended operating conditions.

### **Electrical Specifications**

| Parameter                                                | Conditions                                      | Min | Тур   | Max | Units |

|----------------------------------------------------------|-------------------------------------------------|-----|-------|-----|-------|

| Operational Frequency Range                              |                                                 | 2   |       | 6   | GHz   |

| Small Signal Gain                                        |                                                 |     | > 22  |     | dB    |

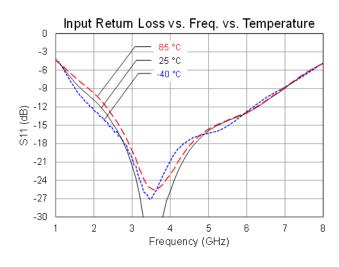

| Input Return Loss                                        |                                                 |     | > 10  |     | dB    |

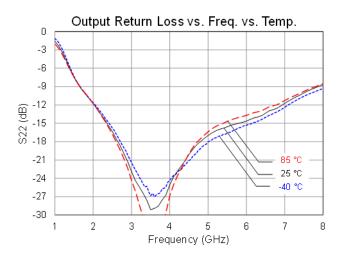

| Output Return Loss                                       |                                                 |     | > 10  |     | dB    |

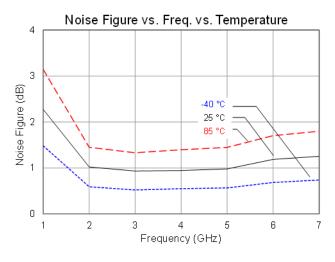

| Noise Figure                                             |                                                 |     | 1     |     | dB    |

| Output Power @ 1 dB Gain Compression (P <sub>1dB</sub> ) |                                                 |     | > 18  |     | dBm   |

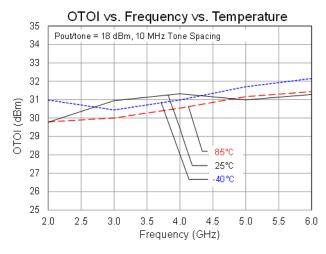

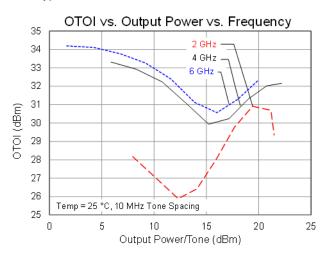

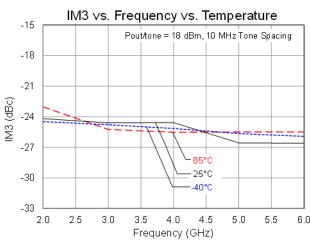

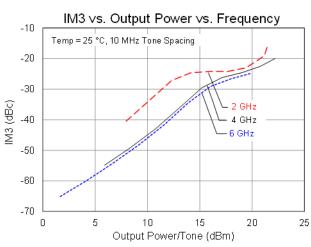

| Output TOI                                               | P <sub>OUT</sub> /Tone = 18 dBm,<br>Δf = 10 MHz |     | 30    |     | dBm   |

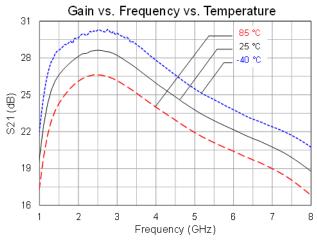

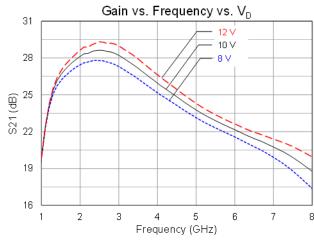

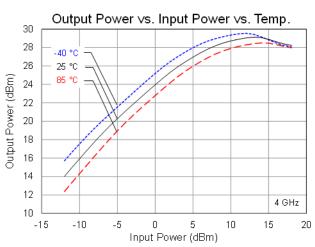

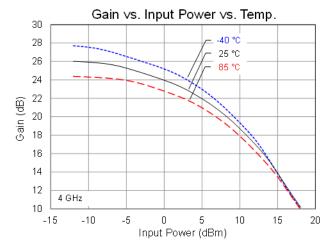

| Small Signal Gain Temperature Coefficient                |                                                 |     | -0.03 |     | dB/°C |

| Noise Figure Temperature Coefficient                     |                                                 |     | 0.007 |     | dB/°C |

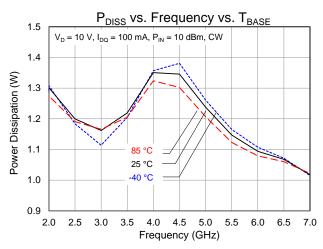

Test conditions unless otherwise noted: T<sub>BASE</sub> = +25 °C, V<sub>D</sub> = 10V, I<sub>DQ</sub> = 100mA, V<sub>G</sub> = -2.3V Typical, CW

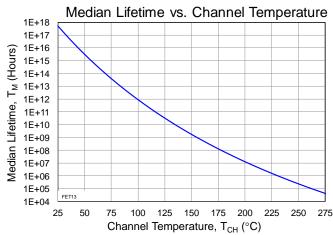

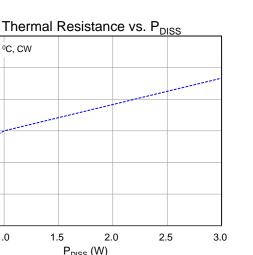

#### **Thermal and Reliability Information**

| Parameter                                            | Test Conditions                                                                      | Value   | Units |

|------------------------------------------------------|--------------------------------------------------------------------------------------|---------|-------|

| Thermal Resistance (θ <sub>JC</sub> ) <sup>(1)</sup> | $T_{BASE} = +85 ^{\circ}\text{C}, V_D = 10 \text{V}, I_{DQ} = 100 \text{mA},$        | 19      | °C/W  |

| Channel Temperature (T <sub>CH</sub> ) (1)           | $I_{D_{DRIVE}} = 195 \text{ mA}, P_{IN} = 10 \text{ dBm}, P_{OUT} = 28 \text{ dBm},$ | 110     | °C    |

| Median Lifetime (T <sub>M</sub> )                    | Freq. = 4 GHz, P <sub>DISS</sub> = 1.3 W, CW                                         | 2.3E+11 | Hrs.  |

#### Notes:

#### **Median Lifetime**

22

21

20

18

17

16

0.5

$R_{JC}$  (C/W) 19  $T_{BASE} = 85 \, {}^{\circ}\text{C}, \, \text{CW}$

1.0

Test Conditions:  $V_D = 40 \text{ V}$ ; Failure Criterion = 10% reduction in  $I_{D \text{ MAX}}$

1.5

2.0

P<sub>DISS</sub> (W)

<sup>1.</sup> Package backside temperature fixed at 85 °C.

### Performance Plots - Small Signal

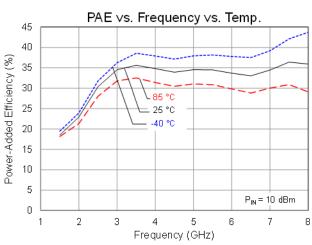

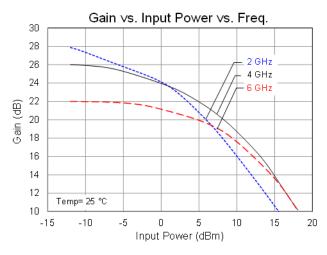

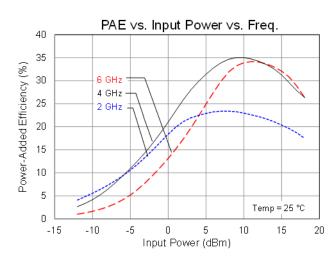

### Performance Plots - Large Signal

### Performance Plots - Large Signal

# Performance Plots – Large Signal

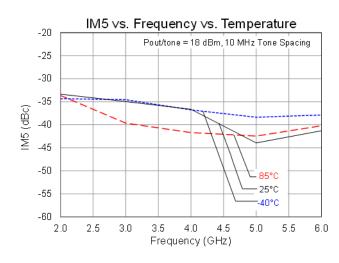

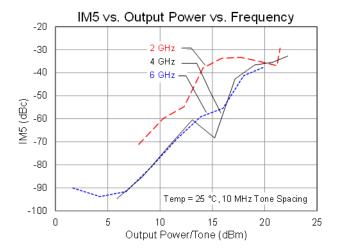

### **Performance Plots – Linearity**

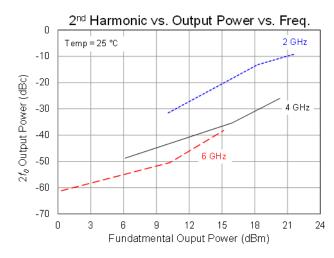

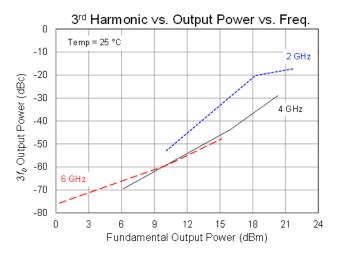

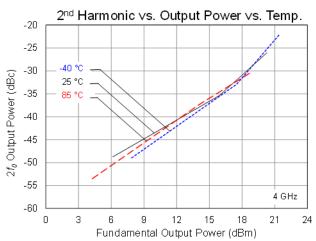

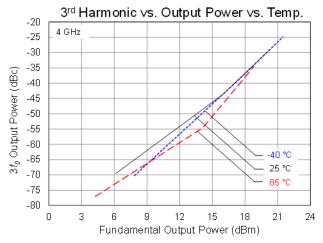

### **Performance Plots – Harmonic**

# **Application Circuit**

# **Bias Up Procedure**

- 1. Set I<sub>D</sub> limit to 300 mA, I<sub>G</sub> limit to 3 mA

- 2. Set V<sub>G</sub> to -5.0V

- 3. Set V<sub>D</sub> +10V

- 4. Adjust  $V_G$  more positive until  $I_{DQ} = 100$  mA.

(V<sub>G</sub> ~ -2.3 V Typical)

5. Apply RF signal

#### **Bias Down Procedure**

- 1. Turn off RF signal

- 2. Set  $V_G$  to -5.0V. Ensure  $I_{DQ} \sim 0 mA$

- 3. Set V<sub>D</sub> to 0V

- 4. Turn off V<sub>D</sub> supply

- 5. Turn off V<sub>G</sub> supply

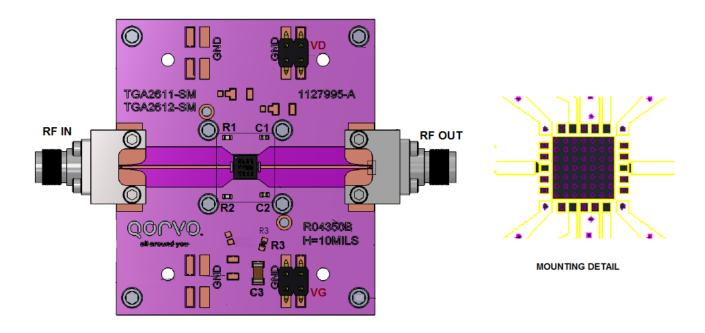

#### **Evaluation Board Layout**

The microstrip line at the connector interface is optimized for the Southwest Microwave end launch connector 1092-01A-5.

The pad pattern shown has been developed and tested for optimized assembly at Qorvo. The PCB land pattern has been developed to accommodate lead tolerances. Since processes vary from company to company, careful process development is recommended

Multiple vias should be employed under the package center paddle to minimize inductance resistance.

#### **Bill of Materials**

| Reference Des. | Value   | Description                                   | Manuf.  | Part Number |

|----------------|---------|-----------------------------------------------|---------|-------------|

| C1, C2         | 0.01 µF | Cap, 0402, 50 V, 10%, X7R                     | Various | _           |

| C3             | 1 μF    | Cap, 1206, 50 V, 10%, X7R                     | Various | _           |

| R1, R2         | 0 Ω     | Res, 0402, 5% (Required for above EVB design) | Various |             |

| R3             | 5 Ω     | Res, 0603, 5%                                 | Various | _           |

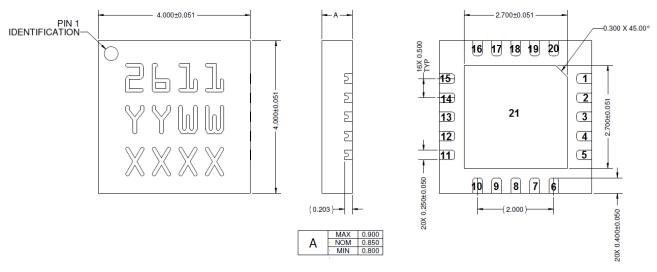

### **Mechanical Information, Pin Configuration and Description**

NOTES:

OTES:

1. PACKAGE LEADS ARE GOLD PLATED.

2. PART IS MOLD ENCAPSULATED.

3. PART MARKING:

2611: PART NUMBER

YY: PART ASSEMBLY YEAR

WW: PART ASSEMBLY WEEK

XXXX: BATCH ID

| UNLESS OTHERWISE<br>SPECIFIED: DIMENSION<br>ARE IN MM                          |

|--------------------------------------------------------------------------------|

| TOLERANCES<br>X.XX = ±.25<br>X.XXX = ±.127<br>X.XXXX = ±.0254<br>ANGLES = 0.5° |

| Pin No.                         | Label          | Description                                                                                    |

|---------------------------------|----------------|------------------------------------------------------------------------------------------------|

| 1-2, 4-9, 11, 12, 14, 15, 17-20 | N/C            | Recommend grounding on PCB for improved package isolation. Connected to ground paddle (21)     |

| 3                               | RF Input       | RF input, matched to 50 Ω, DC blocked                                                          |

| 10                              | V <sub>G</sub> | Gate voltage. Bias network required                                                            |

| 13                              | RF Output      | RF output, matched to 50 Ω, DC blocked                                                         |

| 16                              | $V_D$          | Drain voltage. Bias network required.                                                          |

| 21                              | GND            | Ground Paddle. Multiple vias should be employed to minimize inductance and thermal resistance. |

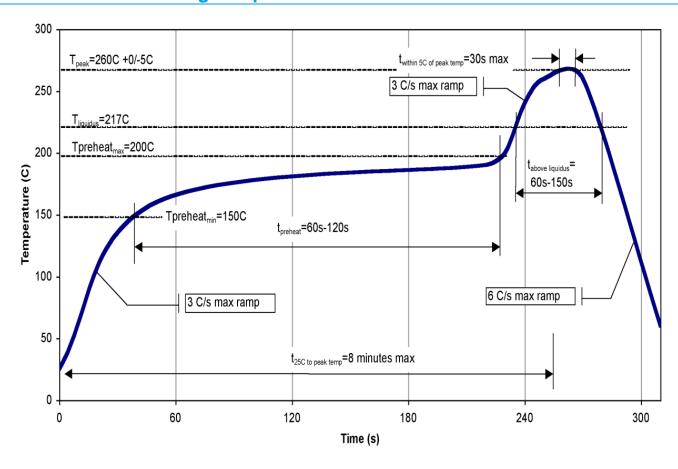

### **Recommended Soldering Temperature Profile**