# GigaDevice Semiconductor Inc.

# GD32F103xx ARM<sup>®</sup> 32-bit Cortex<sup>™</sup>-M3 CPU

# 用户手册

本文档由北京锐鑫同创科技有限公司依据 GD32F103xx User Manual V1.0 翻译整理完成,已经进行了全面的校对,由于我们的水平有限以及文档篇幅的庞大,翻译的过程中难免会有错误和遗漏的地方,希望广大读者们能够及时向我们反馈您在阅读期间所发现的错误和问题,我们会尽快在下一个版本中更正。您可以发邮件到 gd32@realsenes.com.cn 向我们提出您的意见和建议,谢谢。

版本: 1.0

发布日期: 2013年9月1日

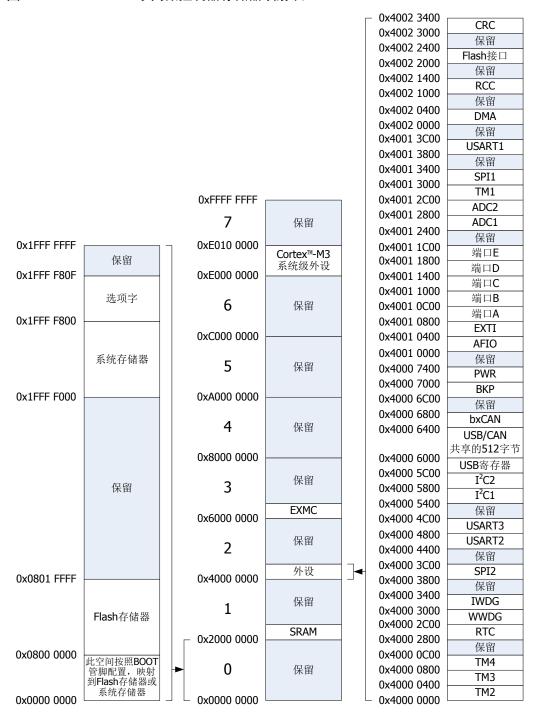

# 目 录

| 第1章 | 系统及存储器架构                    | 1   |

|-----|-----------------------------|-----|

| 1   | ARM Cortex-M3 处理器           | 1   |

| 2   | 系统架构                        | 2   |

| 3   | 存储器映射                       | 4   |

| 4   | 引导配置                        | 7   |

| 5   | CRC 计算单元                    | 7   |

| 第2章 | 电源控制( <b>PWR</b> )          | 11  |

| 1   | 简介                          | 11  |

| 2   | 主要特点                        | 11  |

| 3   | 功能描述                        | 11  |

| 4   | PWR 寄存器                     | 14  |

| 第3章 | 复位及时钟控制单元(RCCU)             | 20  |

| 1   | 复位控制单元( <b>RCU</b> )        | 20  |

| 2   | 时钟控制单元( <b>CCU</b> )        | 21  |

| 3   | RCCU 寄存器                    | 25  |

| 第4章 | 通用 I/O(GPIO)及备选功能 I/O(AFIO) | 42  |

| 1   | GPIO                        |     |

| 2   | GPIO 寄存器                    | 50  |

| 3   | AFIO                        | 57  |

| 4   | AFIO 寄存器                    | 62  |

| 第5章 | 中断及事件                       | 68  |

| 1   | 简介                          | 68  |

| 2   | 主要特点                        | 68  |

| 3   | 功能描述                        | 68  |

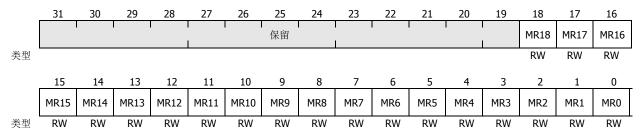

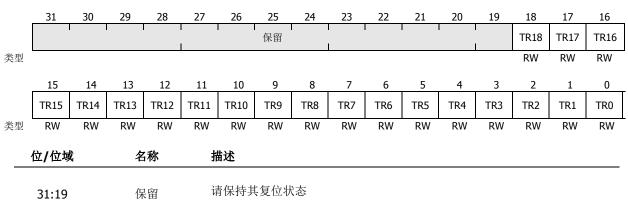

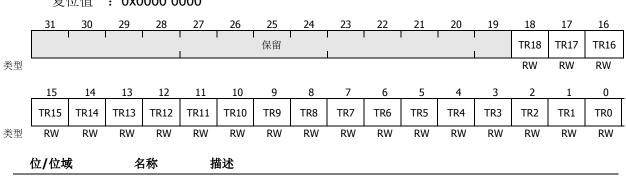

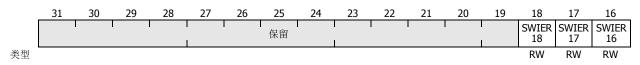

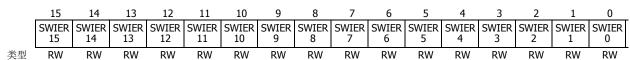

| 4   | 中断及 <b>EXTI</b> 寄存器         | 71  |

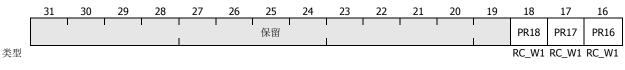

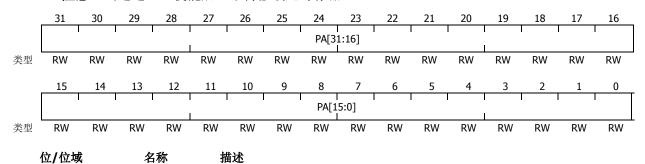

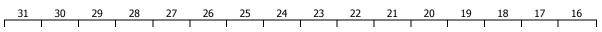

| 第6章 | DMA 控制器                     | 75  |

| 1   | 简介                          | 75  |

| 2   | 主要特点                        | 75  |

| 3   | 功能描述                        | 75  |

| 4   | DMA 寄存器                     | 80  |

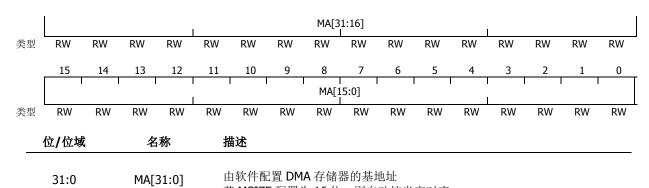

| 第7章 | 定时器( <b>TMx</b> )           | 85  |

| 1   | 高级定时器(TM1)                  | 85  |

| 2   | TM1 寄存器                     | 114 |

| 3   | 通用定时器(TM2~TM4)              | 132 |

| 4   | TM2~TM4 寄存器                 | 155 |

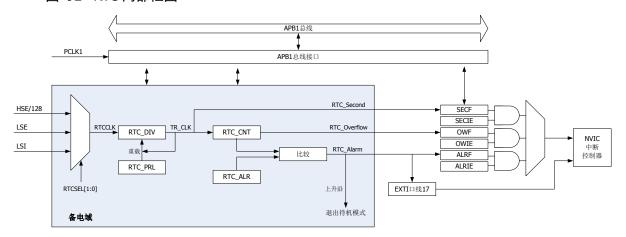

| 第8章 | 实时时钟 RTC                    |     |

| 1   | 简介                          |     |

| 2   | 主要特点                        |     |

| 3   | 功能描述                        | 172 |

| 4      | RTC 寄存器                | 175 |

|--------|------------------------|-----|

| 第9章    | 看门狗(WDG)               | 180 |

| 1      | 独立式看门狗( <b>IWDG</b> )  | 180 |

| 2      | IWDG 寄存器               | 182 |

| 3      | 窗口式看门狗( <b>WWDG</b> )  | 184 |

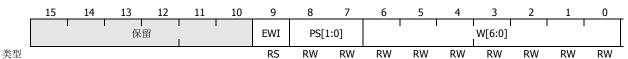

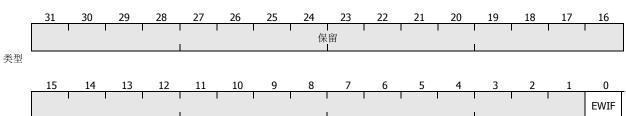

| 4      | WWDG 寄存器               | 186 |

| 第 10 章 | 模数转换器(ADC)             | 189 |

| 1      | 简介                     | 189 |

| 2      | 主要特点                   | 189 |

| 3      | 功能描述                   | 189 |

| 4      | ADC 寄存器                | 202 |

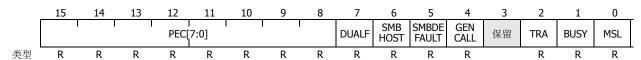

| 第 11 章 | I <sup>2</sup> C 接口    | 212 |

| 1      | 简介                     | 212 |

| 2      | 主要特点                   | 212 |

| 3      | 功能描述                   | 212 |

| 4      | I <sup>2</sup> C 寄存器   |     |

| 第 12 章 | SPI 接口                 | 234 |

| 1      | 简介                     | 234 |

| 2      | 主要特点                   | 234 |

| 3      | 功能描述                   | 234 |

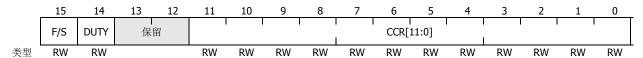

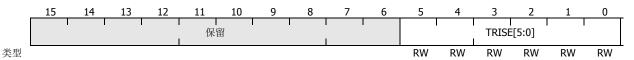

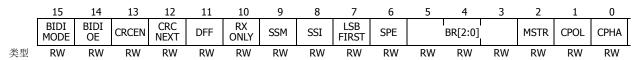

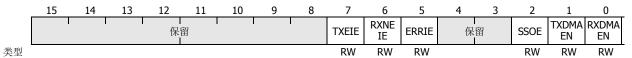

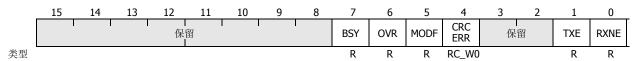

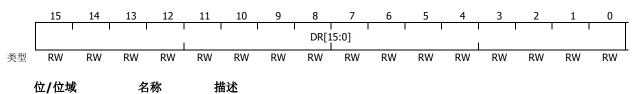

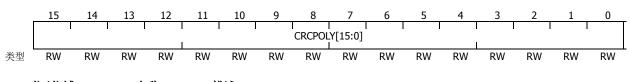

| 4      | SPI 寄存器                |     |

| 第 13 章 | 通用同步/异步收发器(USART)      |     |

| 1      | 简介                     | 250 |

| 2      | 主要特点                   | 250 |

| 3      | 功能描述                   |     |

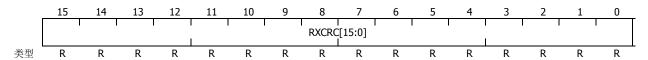

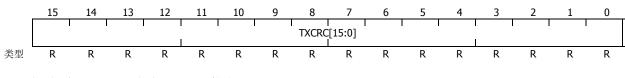

| 4      | USART 寄存器              |     |

| 第 14 章 | 通用串行总线全速接口(USB2.0 FS)  | 269 |

| 1      | 简介                     | 269 |

| 2      | 主要特点                   |     |

| 3      | 功能描述                   |     |

| 4      | USB 寄存器                |     |

| 第 15 章 | 控制器局域网络(bxCAN)         | 282 |

| 1      | 简介                     | 282 |

| 2      | 主要特点                   |     |

| 3      | 功能描述                   |     |

| 4      | bxCAN 寄存器              |     |

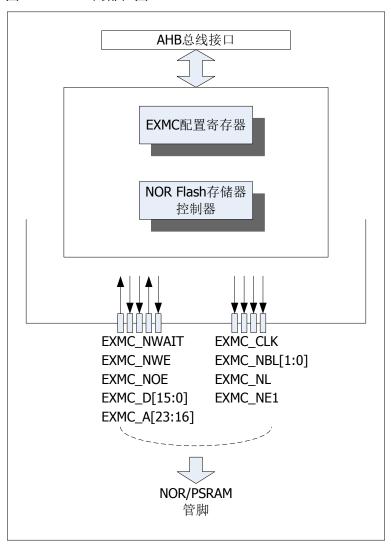

| 第 16 章 | 外部存储器接口( <b>EXMC</b> ) | 312 |

| 1      | 简介                     |     |

| 2      | 主要特点                   |     |

| 3      | 功能描述                   |     |

| 4      | EXMC 寄存器               | 328 |

# 图

| 图 | 1  | Cortex™-M3 内部框图                | 2   |

|---|----|--------------------------------|-----|

| 图 | 2  | GD32F103xx 系列微控制器系统架构          | 3   |

| 图 | 3  | GD32F103xx 系列微控制器存储器映射表        | 5   |

| 图 | 4  | CRC 计算单元框图                     | 8   |

| 图 | 5  | 电源概览                           | 12  |

| 图 | 6  | 系统复位电路框图                       | 20  |

| 图 | 7  | 时钟树                            | 22  |

| 图 | 8  | HSE 时钟源                        | 23  |

| 图 | 9  | 标准 I/O 管脚的基本结构                 | 43  |

| 图 | 10 | 标准 I/O 管脚与可耐受 5V 的 I/O 管脚      | 44  |

| 图 | 11 | 浮空输入/上拉输入/下拉输入的配置              | 45  |

| 图 | 12 | 输出配置                           | 46  |

| 图 | 13 | 高阻模拟输入配置                       | 47  |

| 图 | 14 | 备选功能配置                         | 48  |

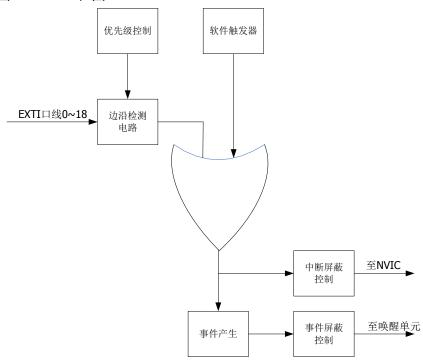

| 图 | 15 | EXTI 框图                        | 71  |

| 图 | 16 | DMA 请求映射                       | 78  |

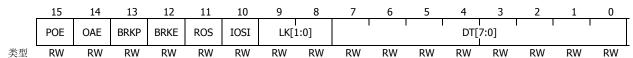

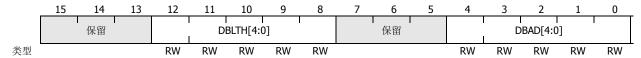

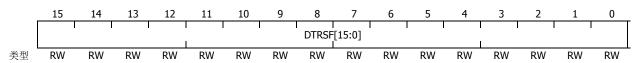

| 图 | 17 | 高级定时器内部框图                      | 86  |

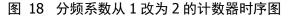

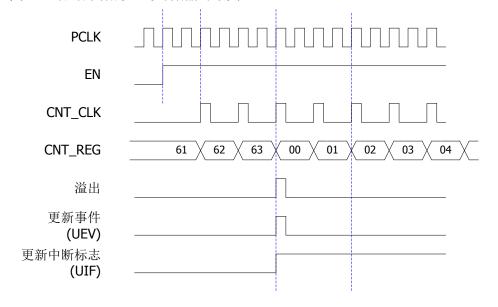

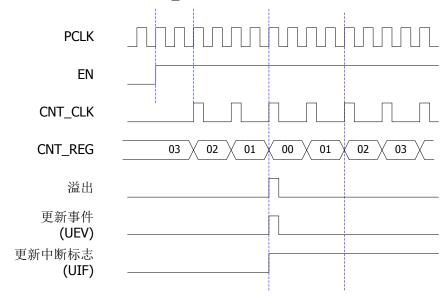

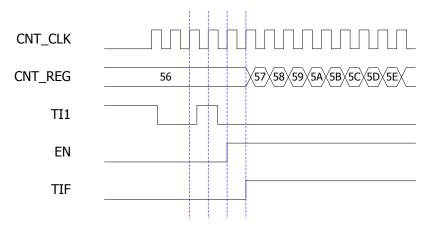

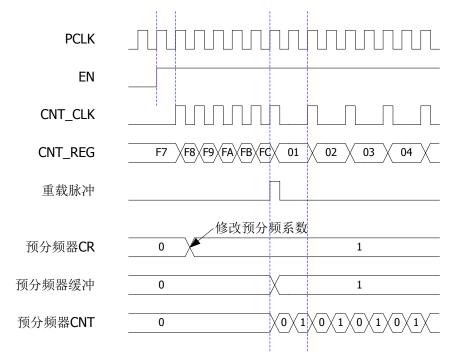

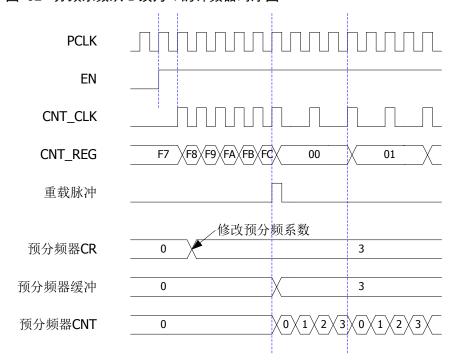

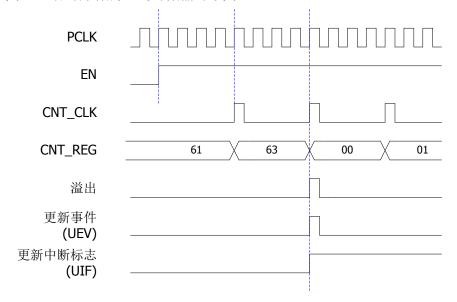

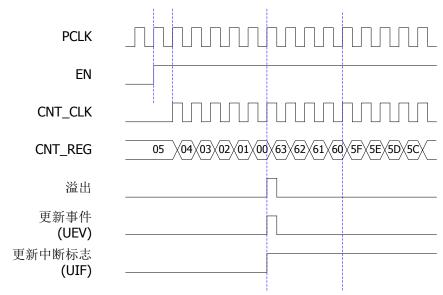

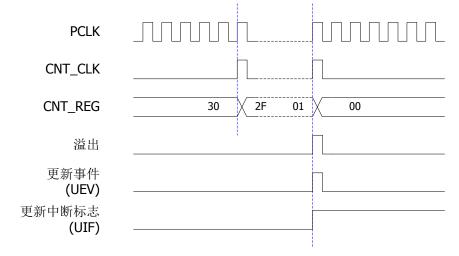

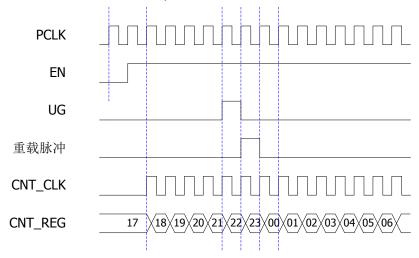

| 图 | 18 | 分频系数从1改为2的计数器时序图               | 87  |

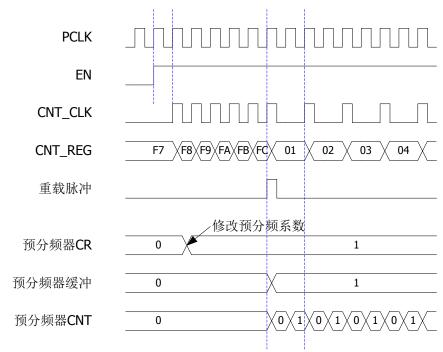

| 图 | 19 | 分频系数从1改为4的计数器时序图               | 87  |

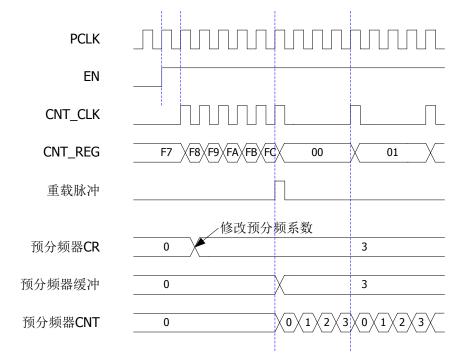

| 图 | 20 | 分频系数为1的计数器时序图                  | 88  |

| 图 | 21 | 分频系数为2的计数器时序图                  | 88  |

| 图 | 22 | 分频系数为4的计数器时序图                  | 89  |

| 图 | 23 | 分频系数为 N 的计数器时序图                | 89  |

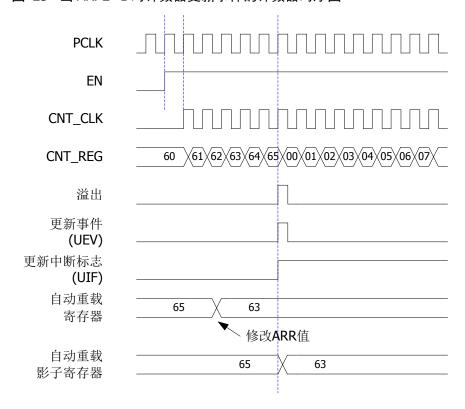

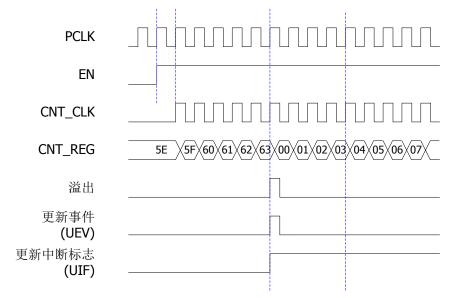

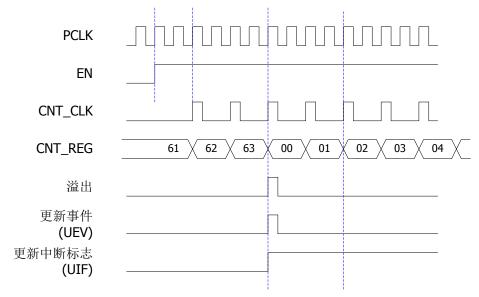

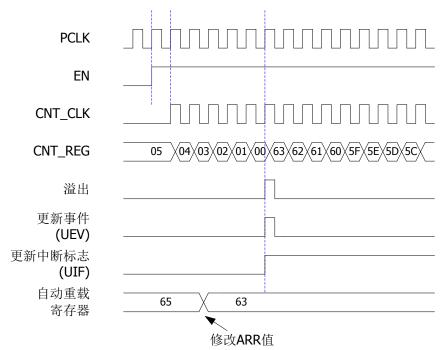

| 图 | 24 | 当 ARPE=0 时计数器更新事件的计数器时序图       | 90  |

| 图 | 25 | 当 ARPE=1 时计数器更新事件的计数器时序图       | 90  |

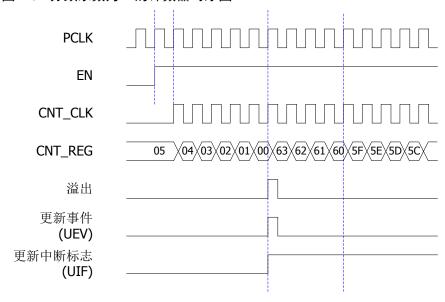

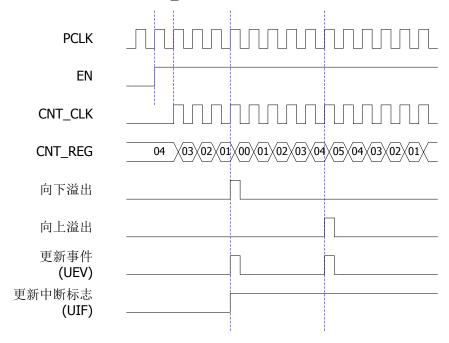

| 图 | 26 | 分频系数为1的计数器时序图                  | 91  |

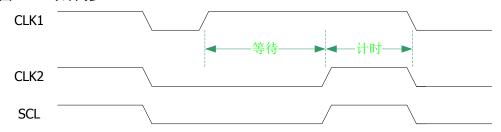

| 图 | 27 | 分频系数为2的计数器时序图                  | 92  |

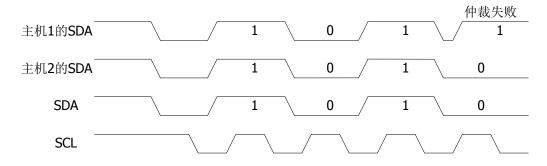

| 图 | 28 | 分频系数为4的计数器时序图                  | 92  |

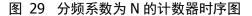

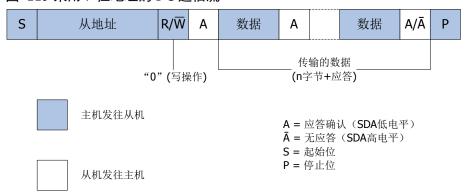

| 图 | 29 | 分频系数为 N 的计数器时序图                | 93  |

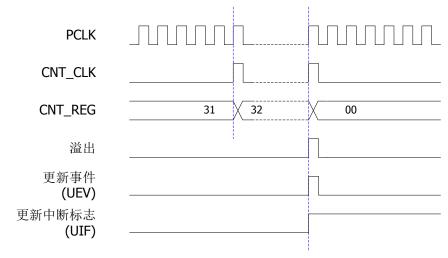

| 图 | 30 | 当计数器未使用时,计数器更新事件的计数器时序图        | 93  |

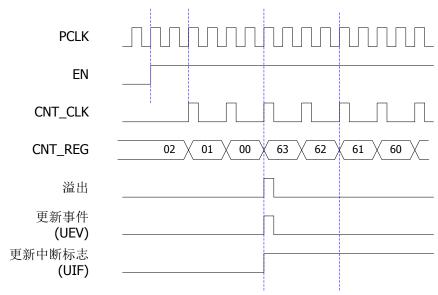

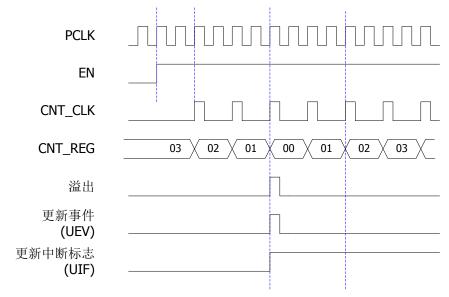

| 图 | 31 | 分频系数为 1、TMx_ARR = 0x5 的计数器时序图  | 94  |

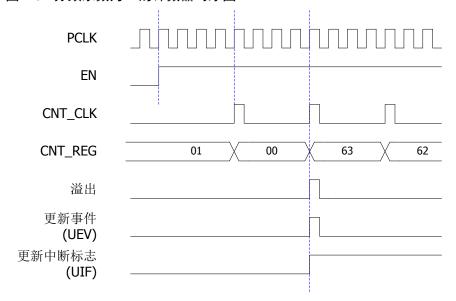

| 图 | 32 | 分频系数为 2、TMx_ARR = 0x5 的计数器时序图  | 95  |

| 图 | 33 | 分频系数为 4、TMx_ARR = 0x63 的计数器时序图 | 95  |

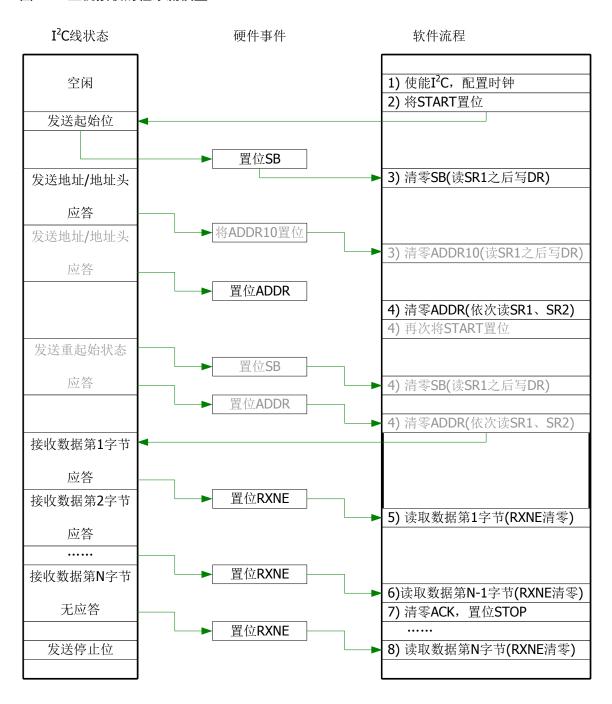

| 图 | 34 | 分频系数为 N 时的计数器时序图               | 96  |

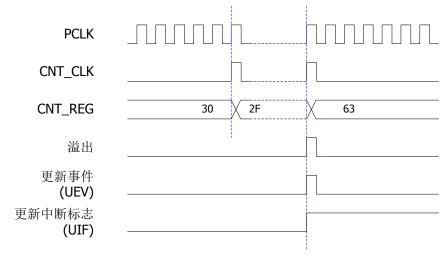

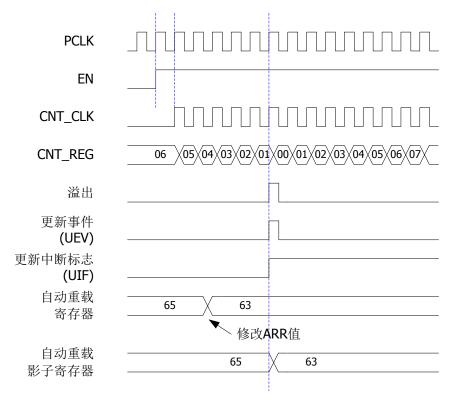

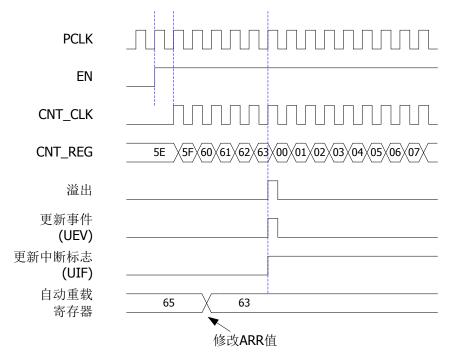

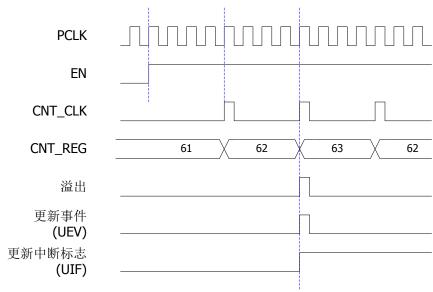

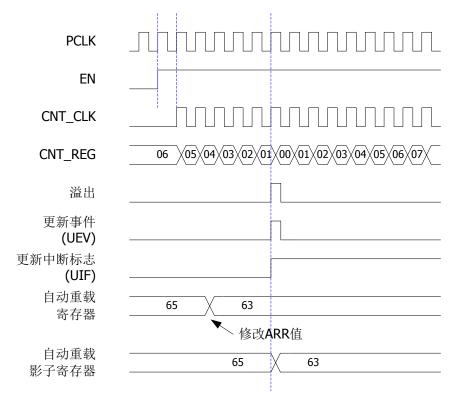

| 图 | 35 | APRE = 1 时计数器更新事件的计数器时序图       | 96  |

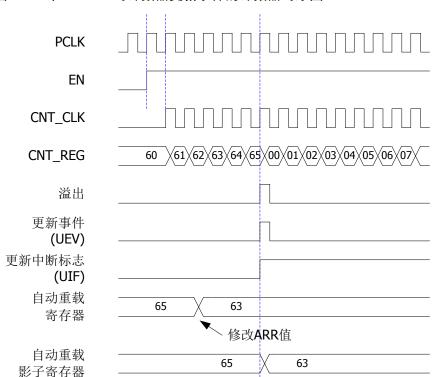

| 图 | 36 | APRE = 1 时计数器更新事件的计数器时序图       |     |

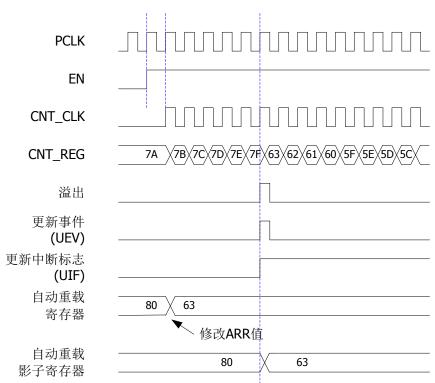

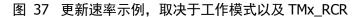

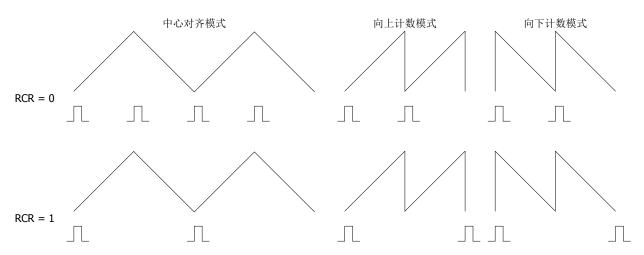

| 图 | 37 | 更新速率示例,取决于工作模式以及 TMx_RCR       | 98  |

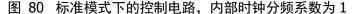

| 图 | 38 | 标准模式下的控制电路,内部时钟分频系数为1          | 98  |

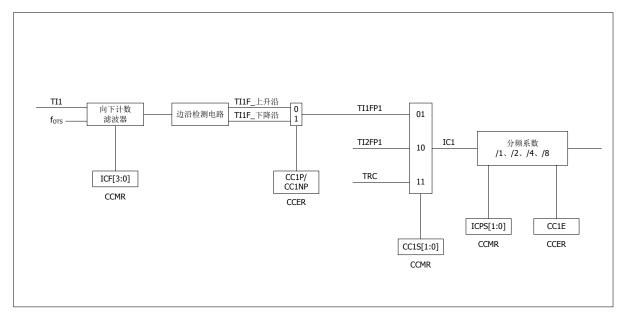

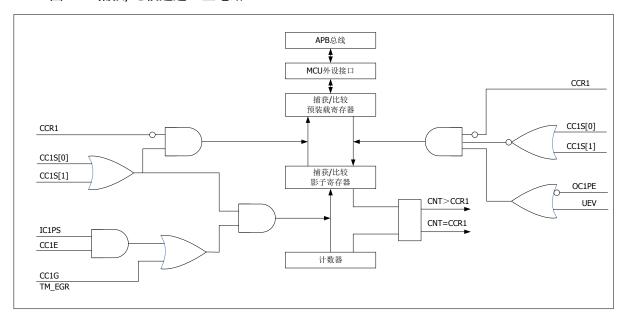

| 图 | 39 | 捕获/比较通道(示例:通道1输入级)             | 100 |

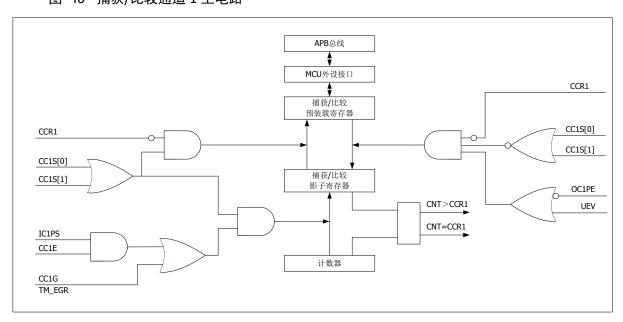

| 图 | 40 | 捕获/比较通道 1 主电路                   | 100 |

|---|----|---------------------------------|-----|

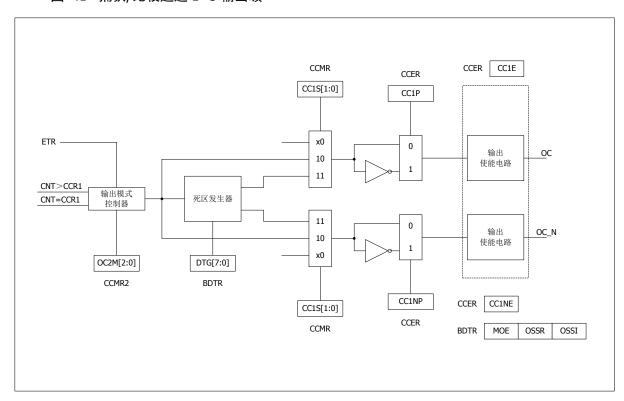

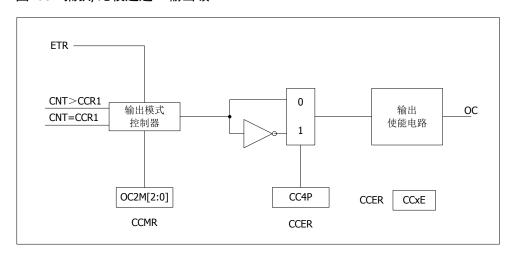

| 图 | 41 | 捕获/比较通道 1~3 输出级                 | 101 |

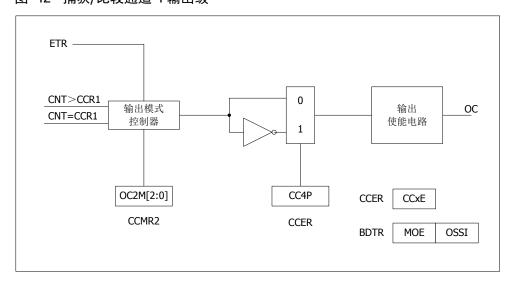

| 图 | 42 | 捕获/比较通道 4 输出级                   | 101 |

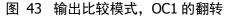

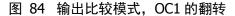

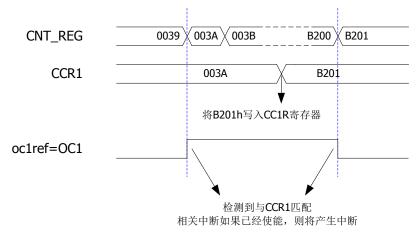

| 图 | 43 | 输出比较模式, <b>OC1</b> 的翻转          | 102 |

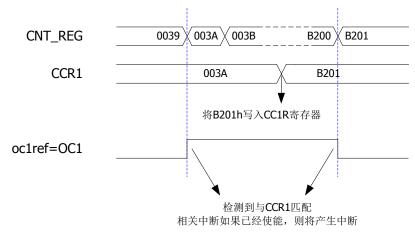

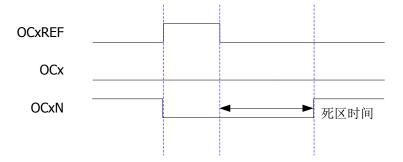

| 图 | 44 | 带有死区时间插入的互补输出                   | 103 |

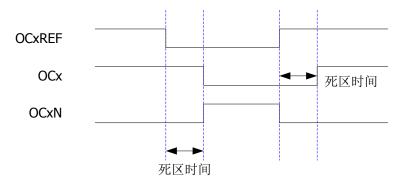

| 图 | 45 | 当延迟大于负脉冲时的死区时间波形                | 103 |

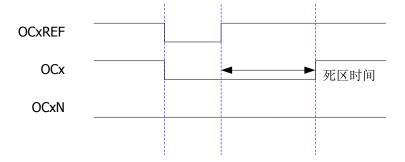

| 图 | 46 | 当延迟大于正脉冲时的死区时间波形                | 103 |

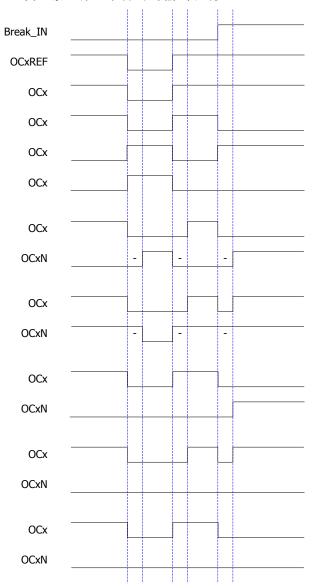

| 图 | 47 | 发生紧急停止事件时的输出表现                  | 104 |

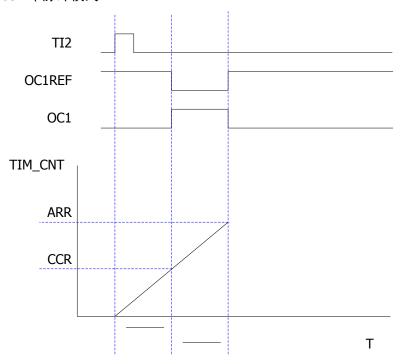

| 图 | 48 | 单脉冲模式                           | 105 |

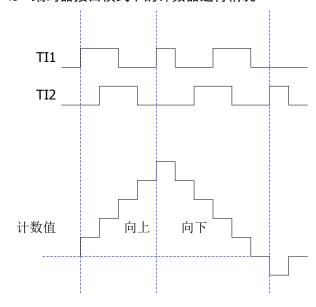

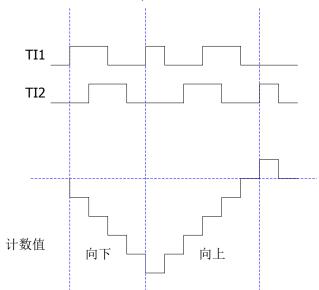

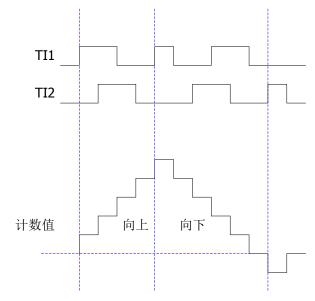

| 图 | 49 | 编码器接口模式下的计数器运行情况                | 106 |

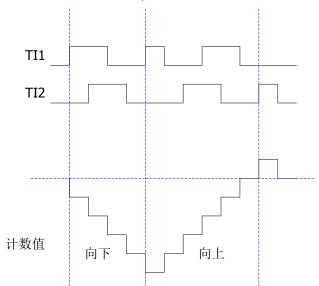

| 图 | 50 | TF1FP1 极性反转后,编码器接口模式下的计数器运行情况   | 107 |

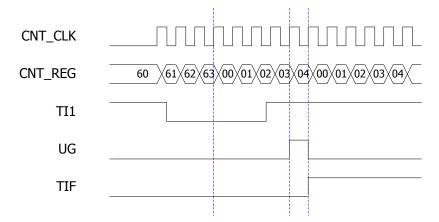

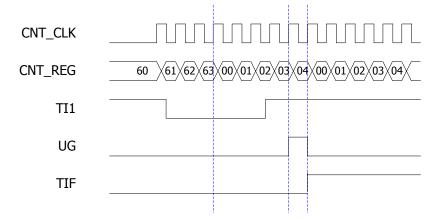

| 图 | 51 | 重启模式下的控制电路                      | 108 |

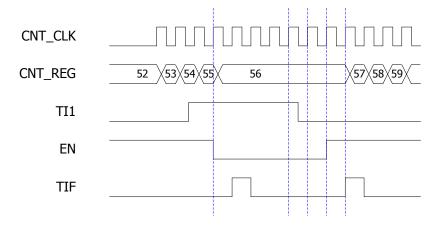

| 图 | 52 | 暂停模式下的控制电路                      | 108 |

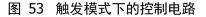

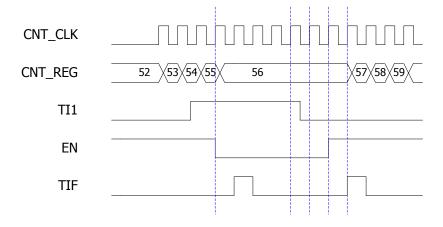

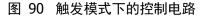

| 图 | 53 | 触发模式下的控制电路                      | 109 |

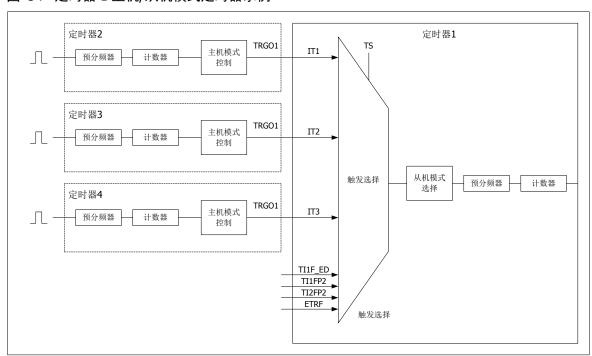

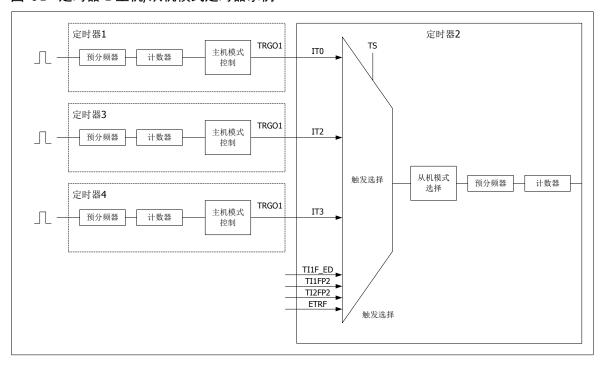

| 图 | 54 | 定时器 1 主机/从机模式定时器示例              | 109 |

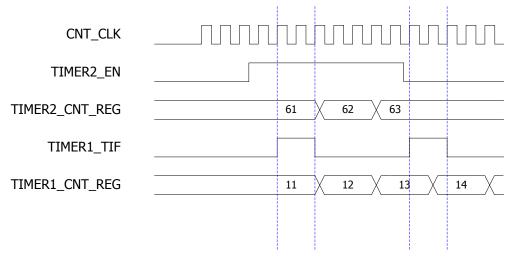

| 图 | 55 | 用定时器 2 的使能输出触发定时器 1             | 110 |

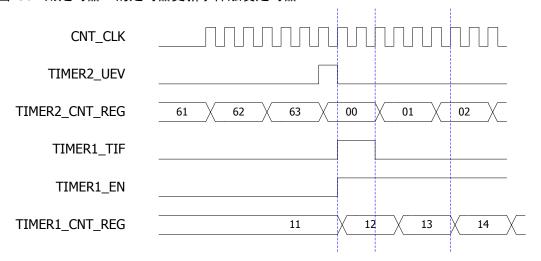

| 图 | 56 | 用定时器 2 的定时器更新事件触发定时器 1          | 111 |

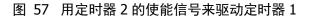

| 图 | 57 | 用定时器 2 的使能信号来驱动定时器 1            | 112 |

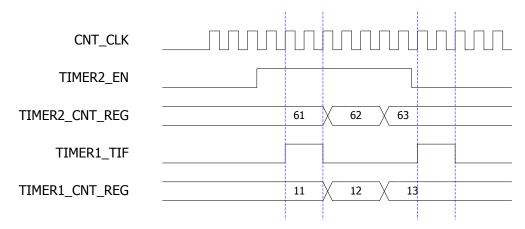

| 图 | 58 | 用定时器 2 的 OC1REF 信号来驱动定时器 1      | 112 |

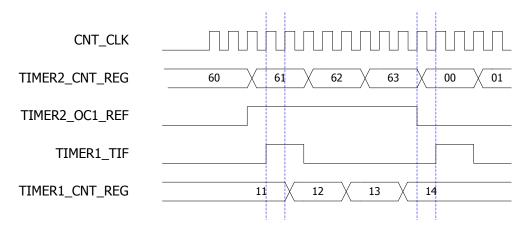

| 图 | 59 | 用定时器1的TI1信号来触发定时器1和定时器2         | 113 |

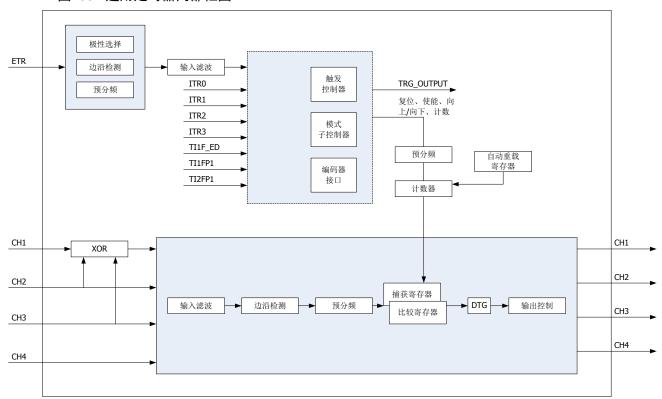

| 图 | 60 | 通用定时器内部框图                       | 133 |

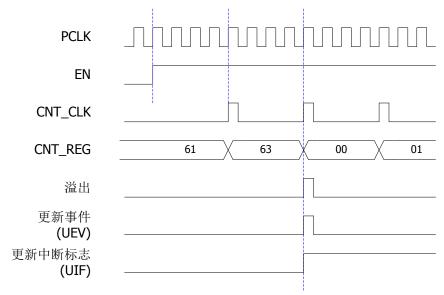

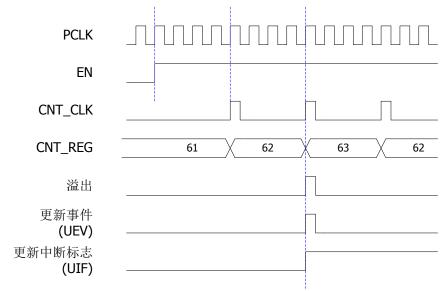

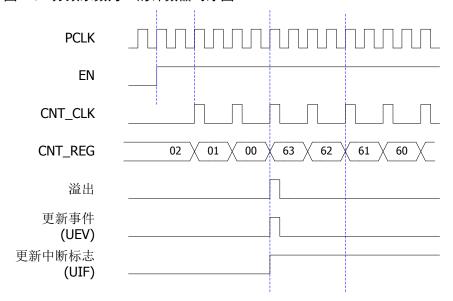

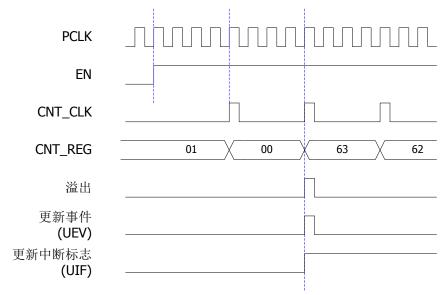

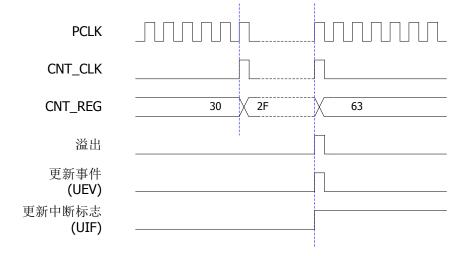

| 图 | 61 | 分频系数从1改为2的计数器时序图                | 135 |

| 图 | 62 | 分频系数从1改为4的计数器时序图                | 135 |

| 图 | 63 | 分频系数为1的计数器时序图                   | 136 |

| 图 | 64 | 分频系数为2的计数器时序图                   | 137 |

| 图 | 65 | 分频系数为4的计数器时序图                   | _   |

| 图 | 66 | 分频系数为 N 的计数器时序图                 | 138 |

| 图 | 67 | 当 ARPE=0 时计数器更新事件的计数器时序图        | 138 |

| 图 | 68 | 当 ARPE=1 时计数器更新事件的计数器时序图        | 139 |

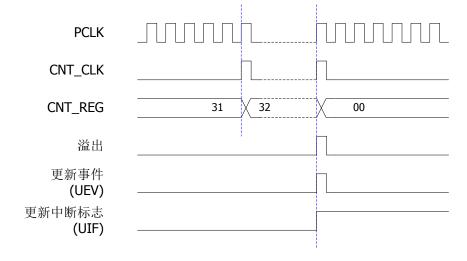

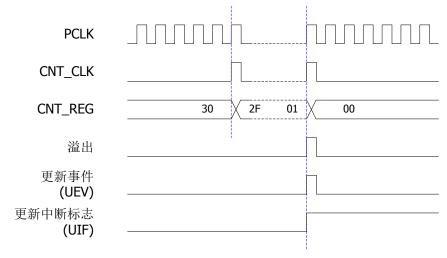

| 图 | 69 | 分频系数为1的计数器时序图                   |     |

| 图 | 70 | 分频系数为2的计数器时序图                   | 140 |

| 图 | 71 | 分频系数为4的计数器时序图                   | 141 |

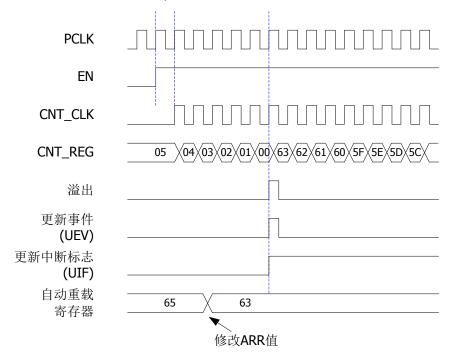

| 图 | 72 | 分频系数为 N 的计数器时序图                 |     |

| 图 | 73 | 当计数器未使用时,计数器更新事件的计数器时序图         |     |

| 图 | 74 | 分频系数为 1、TMx_ARR = 0x5 的计数器时序图   | 143 |

| 图 | 75 | 分频系数为2的计数器时序图                   |     |

| 图 | 76 | 分频系数为 4、TMx_ARR = 0x63 的计数器时序图  | 144 |

| 图 | 77 | 分频系数为 N 时的计数器时序图                |     |

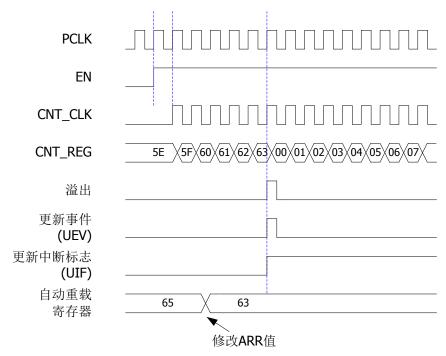

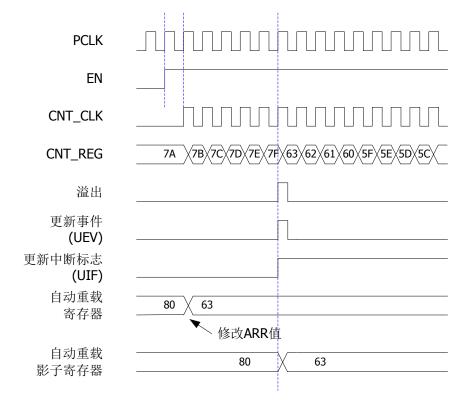

| 图 | 78 | APRE = 1 时计数器更新事件的计数器时序图        |     |

| 图 | 79 | APRE = 1 时计数器更新事件(计数器上溢)的计数器时序图 | 145 |

| 冬 | 80 | 标准模式下的控制电路,内部时钟分频系数为1           | 146 |

| 图 | 81  | 捕获/比较通道(示例:通道1输入级)                          | 147 |

|---|-----|---------------------------------------------|-----|

| 图 | 82  | 捕获/比较通道 1 主电路                               | 148 |

| 图 | 83  | 捕获/比较通道 4 输出级                               | 148 |

| 图 | 84  | 输出比较模式, OC1 的翻转                             | 149 |

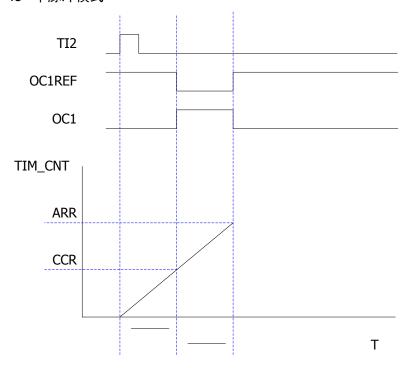

| 图 | 85  | 单脉冲模式                                       | 150 |

| 图 | 86  | 编码器接口模式下的计数器运行情况                            | 151 |

| 图 | 87  | TF1FP1 极性反转后,编码器接口模式下的计数器运行情况               | 152 |

| 图 | 88  | 重启模式下的控制电路                                  | 153 |

| 图 | 89  | 暂停模式下的控制电路                                  | 153 |

| 图 | 90  | 触发模式下的控制电路                                  | 154 |

| 图 | 91  | 定时器 1 主机/从机模式定时器示例                          | 154 |

| 图 | 92  | RTC 内部框图                                    | 173 |

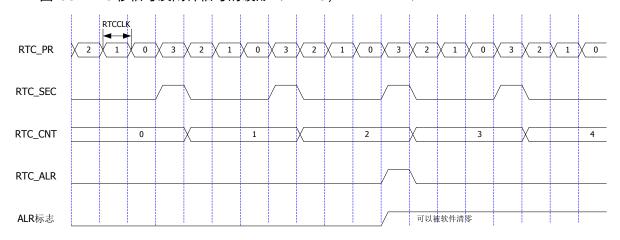

| 图 | 93  | RTC 秒信号及闹钟信号的波形(PR = 3, ALARM = 2)          | 174 |

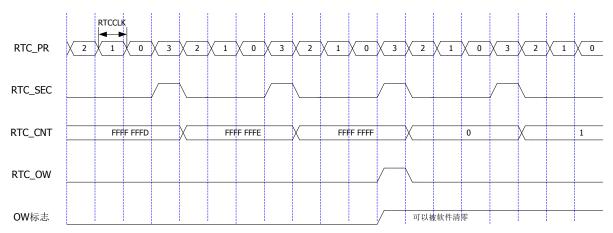

| 图 | 93  | RTC 秒信号及溢出信号的波形 (PR = 3)                    | 175 |

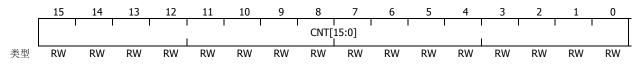

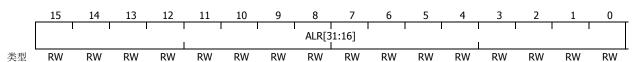

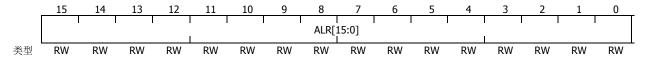

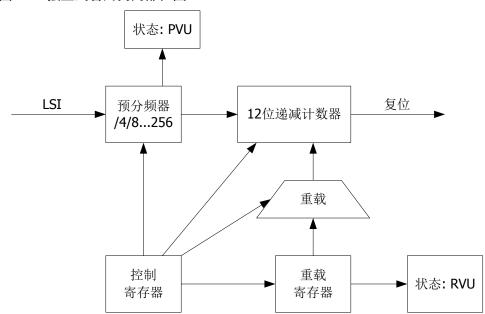

| 图 | 95  | 独立式看门狗内部框图                                  | 181 |

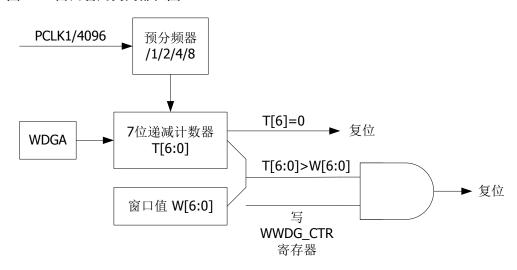

| 图 | 96  | 窗口看门狗内部框图                                   | 185 |

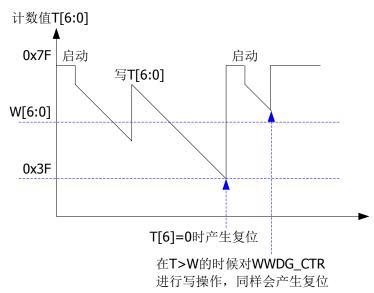

| 图 | 97  | 窗口式看门狗时序图                                   | 186 |

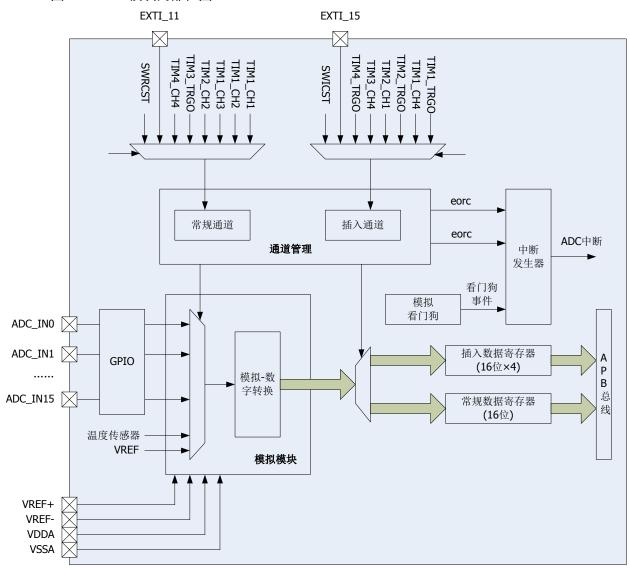

| 图 | 98  | ADC 模块内部框图                                  | 190 |

| 图 | 99  | 单次转换模式                                      | 191 |

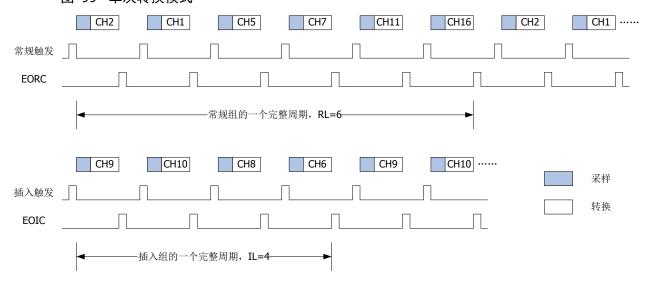

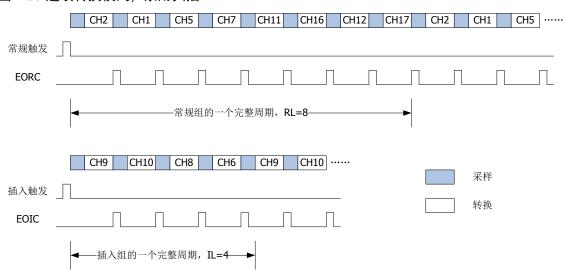

| 图 | 100 | 连续转换模式,禁用扫描                                 | 192 |

| 图 | 101 | 连续转换模式,使能扫描                                 | 192 |

| 图 | 102 | 扫描转换模式                                      | 193 |

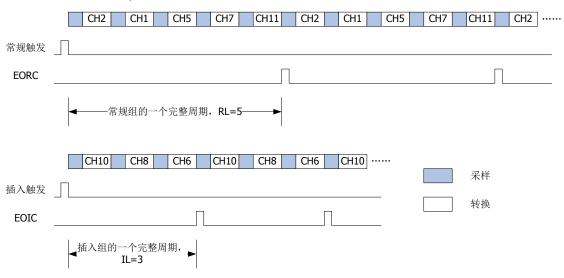

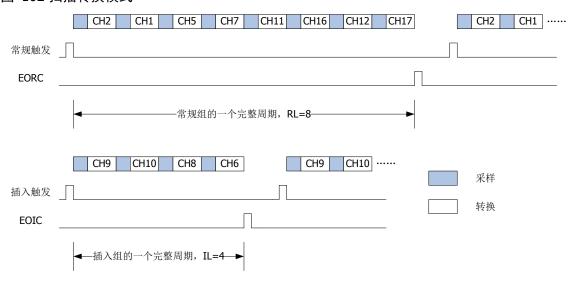

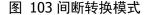

| 图 | 103 | 间断转换模式                                      | 194 |

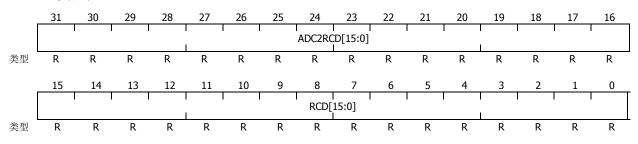

| 图 | 104 | 数据对齐                                        | 195 |

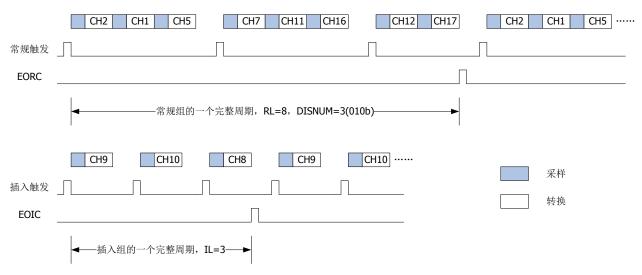

| 图 | 105 | 双 ADC 模式下的功能框图                              | 197 |

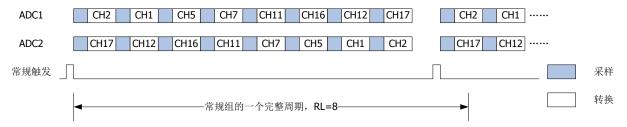

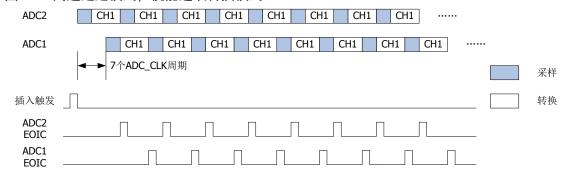

| 图 | 106 | 常规组并发模式                                     | 198 |

| 图 | 107 | 插入组并发模式                                     | 198 |

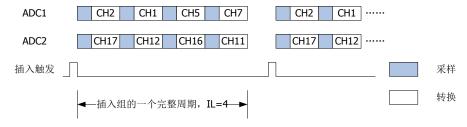

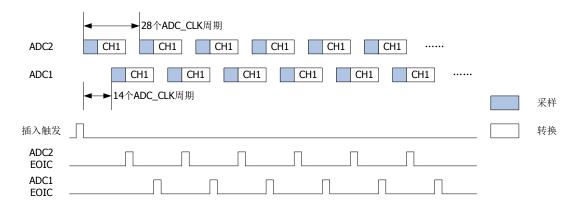

| 图 | 108 | 交替触发模式,禁用插入间断模式                             | 199 |

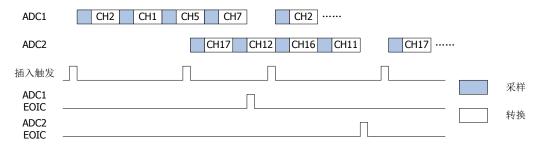

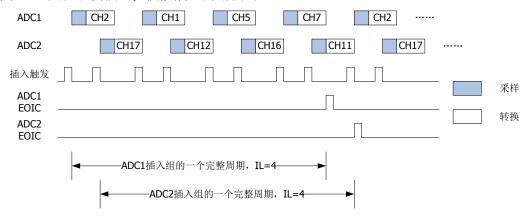

| 图 | 109 | 交替触发模式,使能插入间断模式                             | 199 |

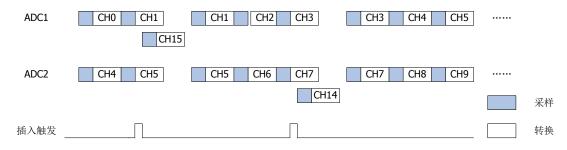

| 图 | 110 | 高速延迟模式,使能连续转换模式                             | 200 |

| 图 | 111 | 低速延迟模式                                      | 200 |

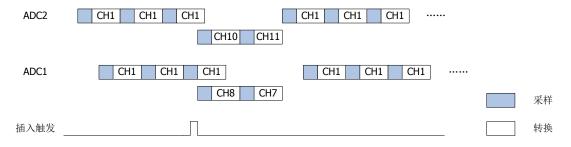

| 图 | 112 | 常规组并发+交替触发模式                                | 201 |

| 图 | 113 | 插入组并发+延迟模式                                  | 201 |

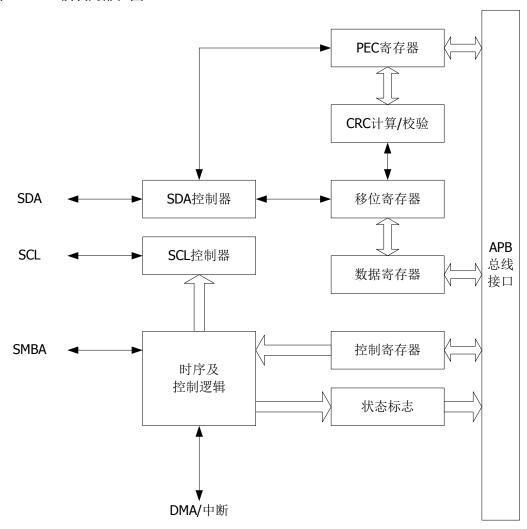

| 图 | 114 | I <sup>2</sup> C 模块内部框图                     | 213 |

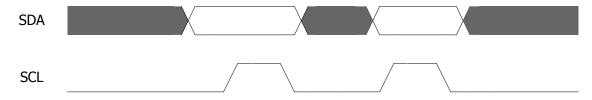

| 图 | 115 | I <sup>2</sup> C 数据有效性                      | 214 |

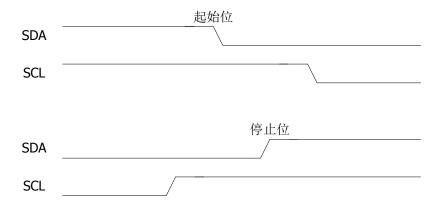

| 图 | 116 | 起始位与停止位                                     | 214 |

| 图 | 117 | 时钟同步                                        | 215 |

| 图 | 118 | SDA 线仲裁                                     | 215 |

| 图 | 119 | 采用 $7$ 位地址的 $I^2$ C通信流                      | 216 |

| 图 | 120 | 采用 <b>10</b> 位地址的 <b>I<sup>2</sup>C</b> 通信流 | 216 |

| 冬 | 121 | 从机发送的程序流模型                                  | 218 |

| 图 | 122 | 从机接收的程序流模型                  | 219 |

|---|-----|-----------------------------|-----|

| 图 | 123 | 主机发送的程序流模型                  | 221 |

| 图 | 124 | 主机接收的程序流模型                  | 223 |

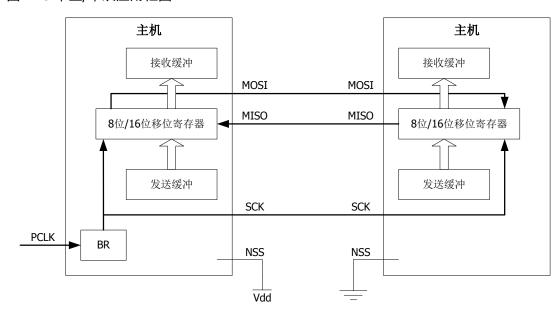

| 图 | 125 | 单主/单从应用框图                   | 235 |

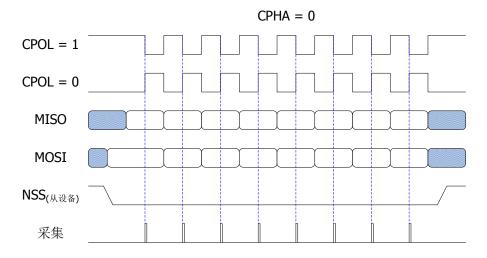

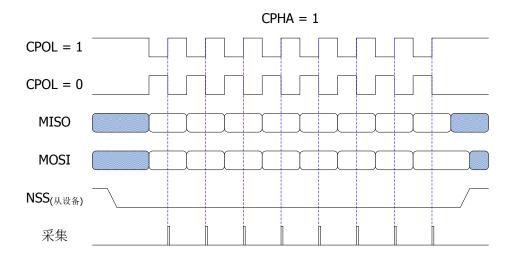

| 图 | 126 | SPI 数据时钟时序图                 | 236 |

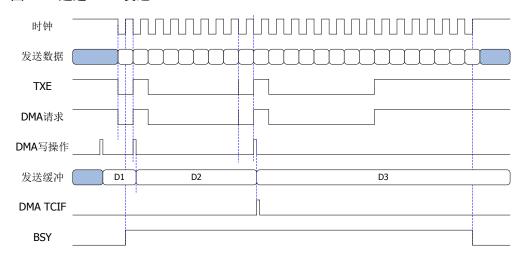

| 图 | 127 | 通过 DMA 发送                   | 242 |

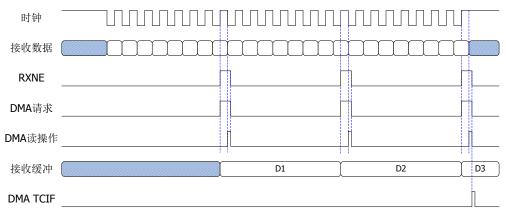

| 图 | 128 | 通过 DMA 接收                   | 244 |

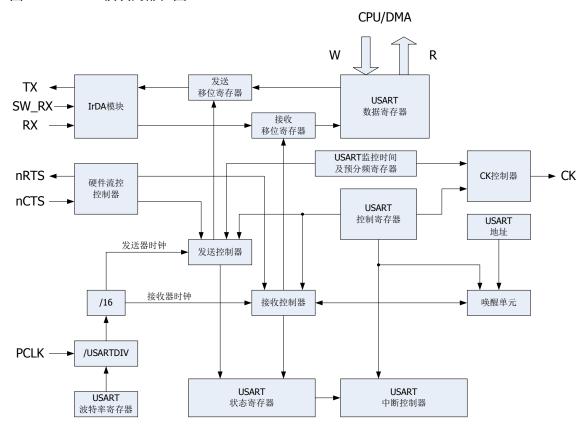

| 图 | 129 | USART 模块内部框图                | 252 |

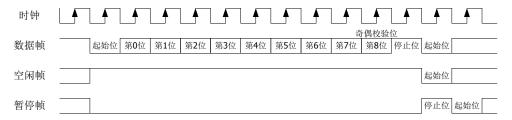

| 图 | 130 | USART 字符帧(9 数据位+1 停止位)      | 253 |

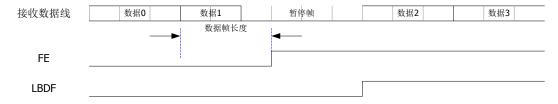

| 图 | 131 | LIN 模式下的帧格式错误检测以及暂停帧检测      | 255 |

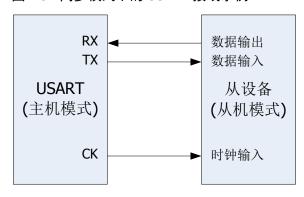

| 图 | 132 | 同步模式下的 <b>USART</b> 接线示例    | 256 |

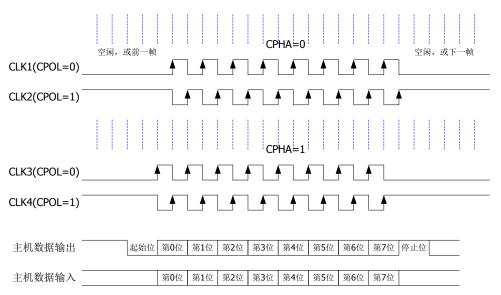

| 图 | 133 | 8 位格式的 USART 同步通信波形(LBCL=1) | 256 |

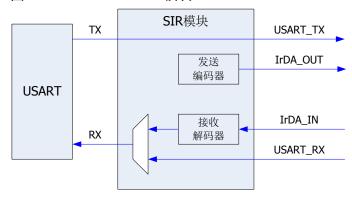

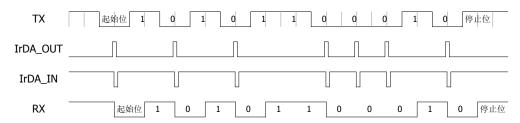

| 图 | 134 | IrDA SIR ENDEC 模块           | 258 |

| 图 | 135 | IrDA 数据调制                   | 258 |

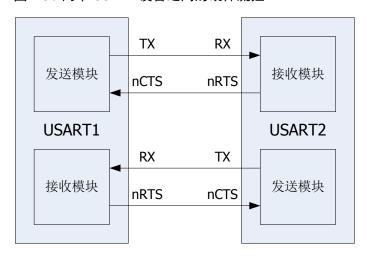

| 图 | 136 | 两个 USART 设备之间的硬件流控          | 258 |

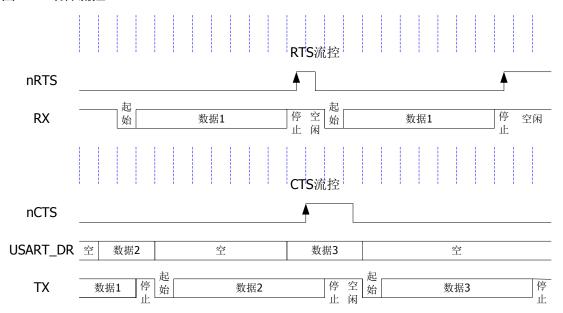

| 图 | 137 | 硬件流控                        |     |

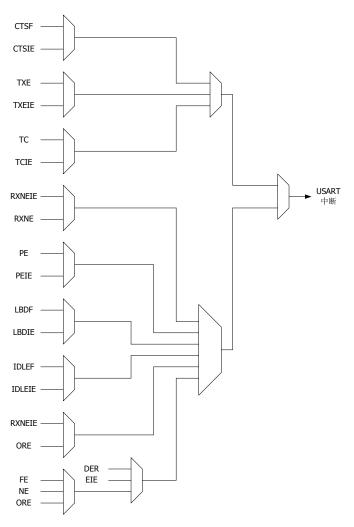

| 图 | 138 | USART 中断映射框图                | 261 |

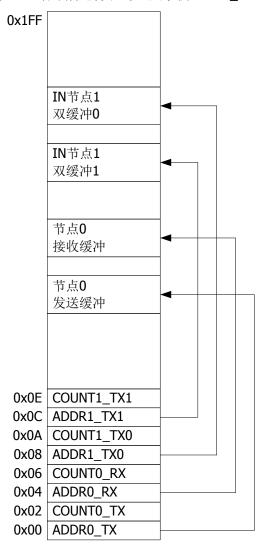

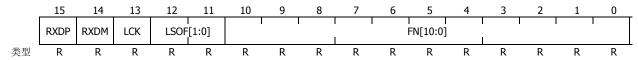

| 图 | 139 | 缓冲描述符表的用法示例(USB_BTABLE=0)   | 270 |

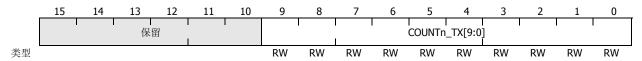

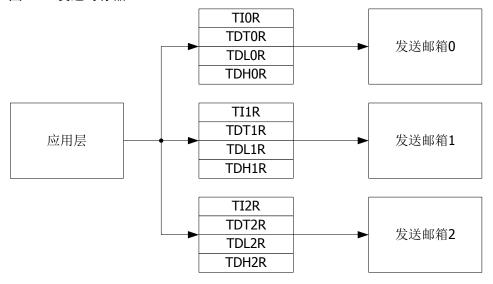

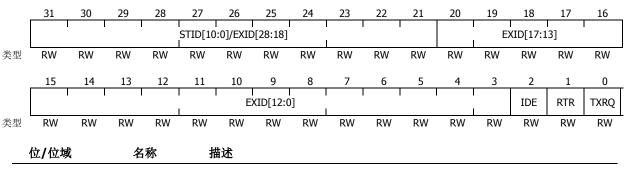

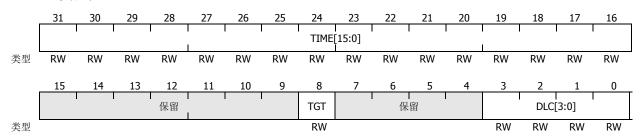

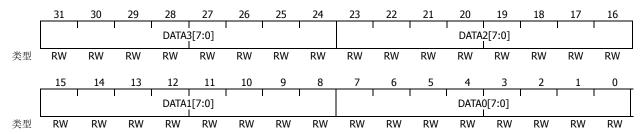

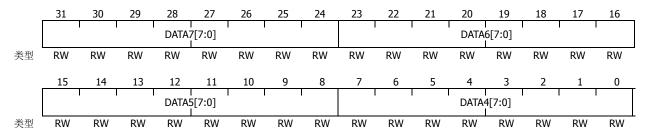

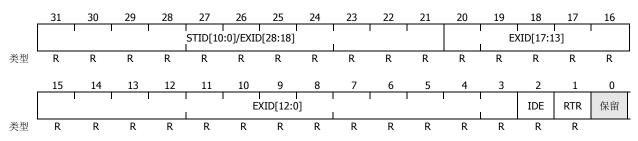

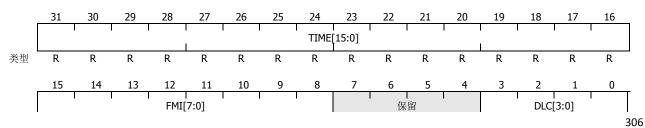

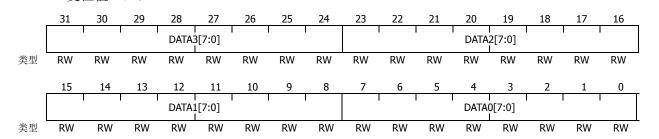

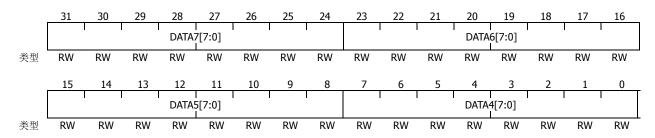

| 图 | 140 | 发送寄存器                       | 285 |

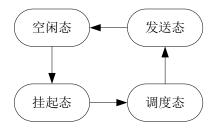

| 图 | 141 | 发送邮箱的基本工作态                  | 285 |

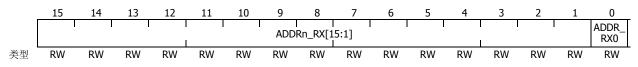

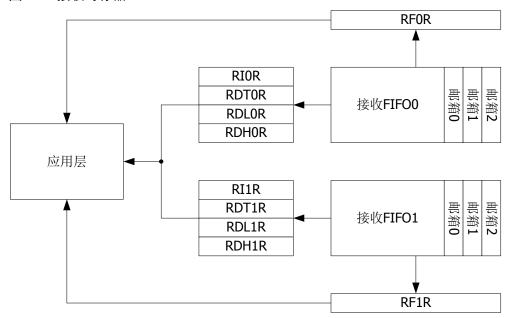

| 图 | 142 | 接收寄存器                       | 287 |

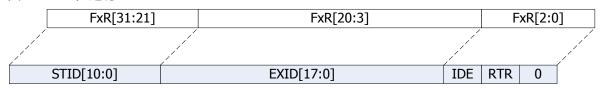

| 图 | 143 | 32 位过滤                      | 288 |

| 图 | 144 | 16 位过滤                      | 288 |

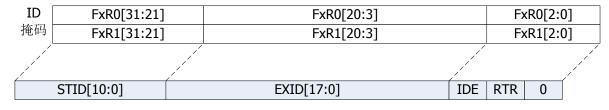

| 图 | 145 | 32 位掩码过滤                    | 288 |

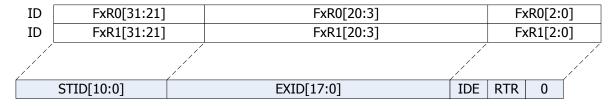

| 图 | 146 | 32 位掩码过滤                    | 289 |

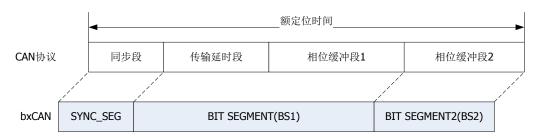

| 图 | 147 | 位时间的组成                      | 291 |

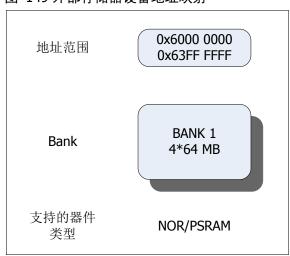

| 图 | 148 | EXMC 内部框图                   | 313 |

| 图 | 149 | 外部存储器设备地址映射                 | 313 |

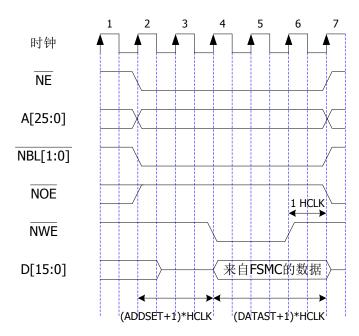

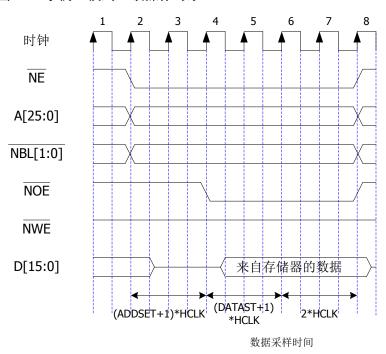

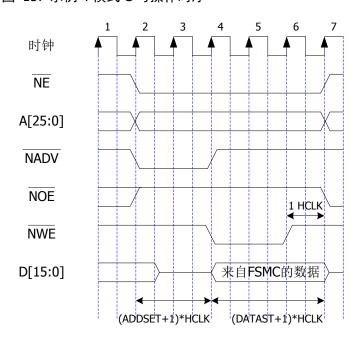

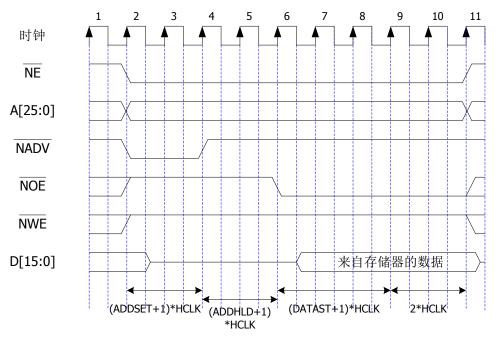

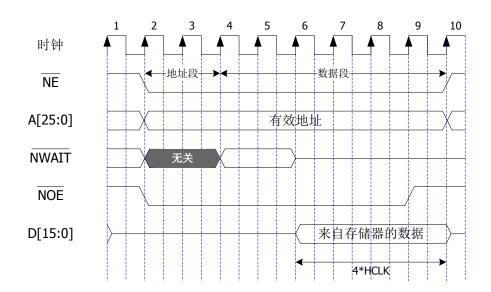

| 图 | 150 | 示例 1 模式 1 写操作时序             | 316 |

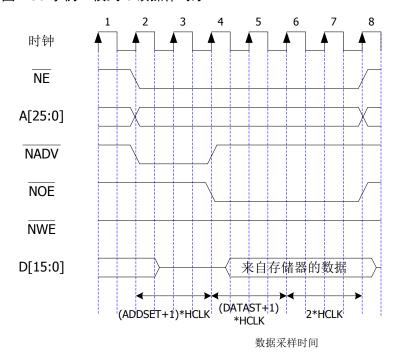

| 图 | 151 | 示例 1 模式 1 读操作时序             | 316 |

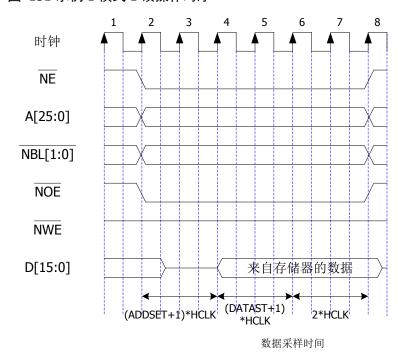

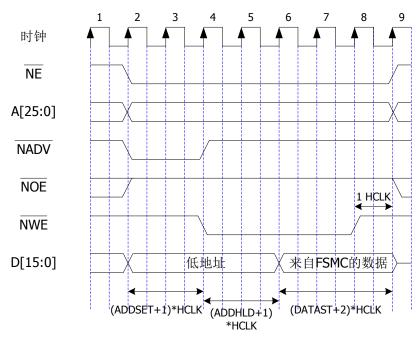

| 图 | 152 | 示例 2 模式 A 写操作时序             |     |

| 图 | 153 | 示例 2 模式 A 读操作时序             | 318 |

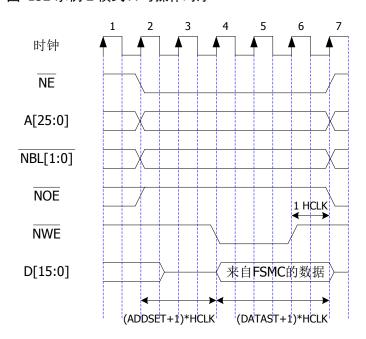

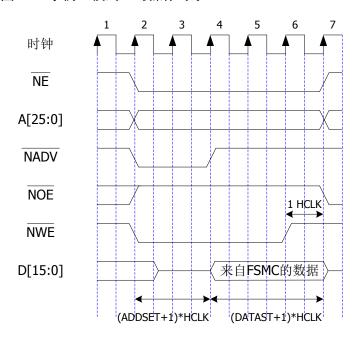

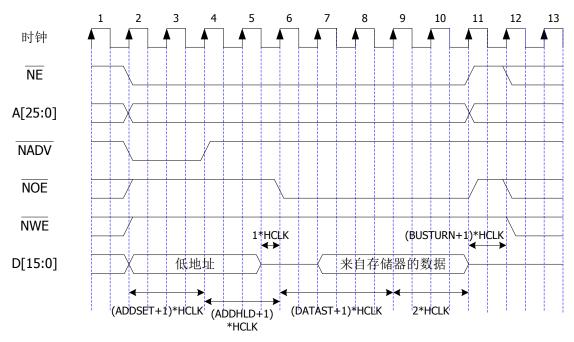

| 图 | 154 | 示例 3 模式 B 写操作时序             | 319 |

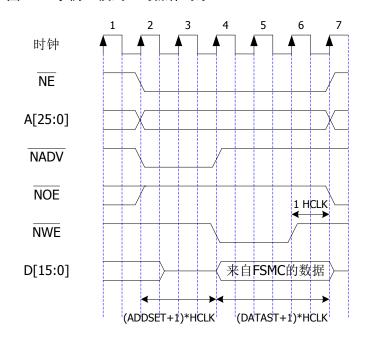

| 图 | 155 | 示例 3 模式 2 写操作时序             | 319 |

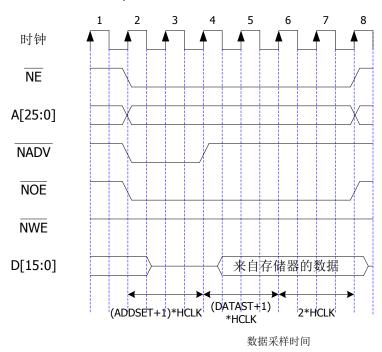

| 图 | 156 | 示例 3 模式 2/B 读操作时序           | 321 |

| 图 | 157 | 示例 4 模式 C 写操作时序             | 322 |

| 图 | 158 | 示例 4 模式 C 读操作时序             | 322 |

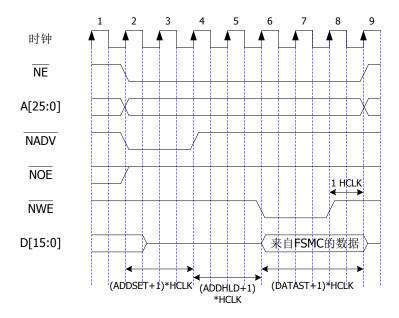

| 图 | 159 | 示例 5 模式 D 写操作时序             | 323 |

| 图 | 160 | 示例 5 模式 D 读操作时序             | 324 |

| 图 | 161 | 示例 6 复用模式写操作时序              | 326 |

| 图 | 162 | 示例 6 复用模式读操作时序              | 326 |

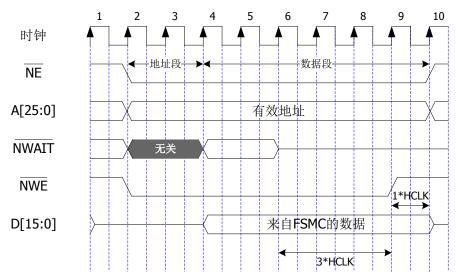

| 图 163 | 示例7异步等待信号作用时的写操作时序 | 327 |

|-------|--------------------|-----|

| 图 164 | 示例7异步等待信号作用时的读操作时序 | 327 |

# 表

| 表 1  | Flash 模块的组织               | 6   |

|------|---------------------------|-----|

| 表 2  | 引导模式                      | 7   |

| 表 3  | 节电模式小结                    | 14  |

| 表 4  | CKOUT 的时钟源选择              | 25  |

| 表 5  | GPIO 端口配置位                | 43  |

| 表 6  | 高级定时器 TM1                 | 48  |

| 表 7  | 通用定时器 TM2/3/4             | 48  |

| 表 8  | USART                     | 49  |

| 表 9  | SPI                       | 49  |

| 表 10 | I <sup>2</sup> C          | 49  |

| 表 11 | bxCAN                     | 50  |

| 表 12 | USB                       | 50  |

| 表 13 | ADC                       | 50  |

| 表 14 | 其它 I/O                    | 50  |

| 表 15 | 调试接口信号                    | 57  |

| 表 16 | 调试接口映射                    | 58  |

| 表 17 | ADC1 外部触发插入式转换备选功能重映射     | 58  |

| 表 18 | ADC1 外部触发标准转换备选功能重映射      | 58  |

| 表 19 | ADC2 外部触发插入式转换备选功能重映射     | 58  |

| 表 20 | ADC2 外部触发标准转换备选功能重映射      | 58  |

| 表 21 | TM1 备选功能重映射               | 59  |

| 表 22 | TM2 备选功能重映射               | 59  |

| 表 23 | TM3 备选功能重映射               | 59  |

| 表 24 | TM4 备选功能重映射               | 60  |

| 表 25 | USART1 备选功能重映射            | 60  |

| 表 26 | USART2 备选功能重映射            | 60  |

| 表 27 | USART3 备选功能重映射            | 60  |

| 表 28 | I <sup>2</sup> C1 备选功能重映射 | 61  |

| 表 29 | SPI1 备选功能重映射              | 61  |

| 表 30 | CAN 备选功能重映射               | 61  |

| 表 31 | OSC32 管脚配置                | 62  |

| 表 32 | OSC 管脚配置                  | 62  |

| 表 33 | Cortex™-M3 中的 NVIC 异常类型   | 69  |

| 表 34 | GD32F103xx 的中断向量表         | 69  |

| 表 35 | DMA 在源与地址间的访问动作           | 77  |

| 表 36 | 各 DMA 通道的可用请求             | 79  |

| 表 37 | 编码器信号以及计数方向               | 106 |

| 表 38 | 编码器信号以及计数方向               | 151 |

| 表 39 | 40kHz(LSI) 频率下的 IWDG 超时范围 | 181 |

| 表 40 | 36MHz(f <sub>PCLK1</sub> )频率下的 WWDG 超时范围 | 186 |

|------|------------------------------------------|-----|

| 表 41 | ADC 管脚定义                                 | 190 |

| 表 42 | 常规通道的外部触发选择                              | 195 |

| 表 43 | 插入通道的外部触发选择                              | 196 |

| 表 44 | I <sup>2</sup> C 总线相关术语定义                | 213 |

| 表 45 | 事件状态标志                                   | 225 |

| 表 46 | I <sup>2</sup> C 错误标志                    | 225 |

| 表 47 | SPI 中断请求                                 | 244 |

| 表 48 | USART 重要管脚描述                             | 251 |

| 表 49 | 停止位配置                                    | 253 |

| 表 50 | USART 中断请求                               | 260 |

| 表 51 | 双缓冲的用法                                   | 273 |

| 表 52 | 接收状态编码                                   | 279 |

| 表 53 | 节点类型编码                                   | 279 |

| 表 54 | 节点类别含义                                   | 279 |

| 表 55 | 发送状态编码                                   |     |

| 表 56 | 32 位列表模式过滤条目编号                           | 289 |

| 表 57 | 匹配索引                                     | 290 |

| 表 58 | NOR Flash 接口信号功能                         | 314 |

| 表 59 | PSRAM 接口信号功能                             | 314 |

| 表 60 | PSRAM 接口信号功能                             | 315 |

| 表 61 | 示例1模式1相关寄存器配置                            | 315 |

| 表 62 | 示例 1 模式 A 相关寄存器配置                        | 317 |

| 表 63 | 示例 3 模式 2/B 相关寄存器配置                      | 318 |

| 表 64 | 示例 4 模式 C 相关寄存器配置                        | 321 |

| 表 65 | 示例 5 模式 D 相关寄存器配置                        | 323 |

| 表 66 | 示例 6 复用模式相关寄存器配置                         | 324 |

| 表 67 | 修订历史                                     | 333 |

# 第1章 系统及存储器架构

GD32F103xx 系列微控制器的系统架构将在本章进行详细介绍,包括 ARM<sup>®</sup> Cortex™-M3 处理器内核、总线架构以及存储器构成。Cortex™-M3 处理器是一种面向新时代的内核,实现了许多新颖的特性。高度集成化以及各种先进功能,使 Cortex™-M3 处理器非常适用于那些要求微控制器兼顾高性能、低功耗的市场和产品。简单说来,Cortex™-M3 处理器包含三组 AHB 总线,分别称为 ICode 总线、DCode 总线以及系统总线。Cortex™-M3 处理器的所有存储器访问都是在这三组总线上执行的,根据访问功能以及目的存储空间予以选择。存储器部分采用哈佛型总线架构,预定义存储器映射,且最高可提供 4GB 的寻址空间,充分保障了系统的灵活性和可扩展性。

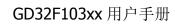

### 1 ARM Cortex-M3 处理器

Cortex™-M3 处理器是一种通用的 32 位处理器内核,尤其适用于兼顾高性能、低功耗的微控制器设计。该处理器具有许多新颖的特性,例如 Thumb2 指令集、硬件除法器、低延迟中断响应、原子级位绑定访问以及多总线同时工作。Cortex™-M3 处理器是基于 ARMv7 架构的,既支持 Thumb指令集也支持 Thumb2 指令集。此外 Cortex™-M3 处理器提供了以下的系统级外设:

- 内部总线矩阵,用于实现 ICode 总线、DCode 总线、系统总线、专用外设总线(PPB)以及调试专用总线(AHB-AP)的互联

- 嵌套式向量型中断控制器 (Nested Vectored Interrupt Controller, 简写为 NVIC)

- 闪存地址重载及断点单元(Flash Patch and Breakpoint,简写为 FPB)

- 数据观测点及跟踪单元(Data Watchpoint and Trace,简写为 DWT)

- 跟踪仪器宏单元(Instrument Trace Macrocell,简写为 ITM)

- 串行线 JTAG 调试接口(Serial Wire JTAG Debug Port, 简写为 SWJ-DP)

- 跟踪端口接口单元(Trace Port Interface Unit,简写为 TPIU)

下图为 Cortex™-M3 处理器的内部框图。如果您想了解关于 Cortex™-M3 更详尽的信息,请参阅《ARM® Cortex™-M3 技术参考手册》。

#### 图 1 Cortex™-M3 内部框图

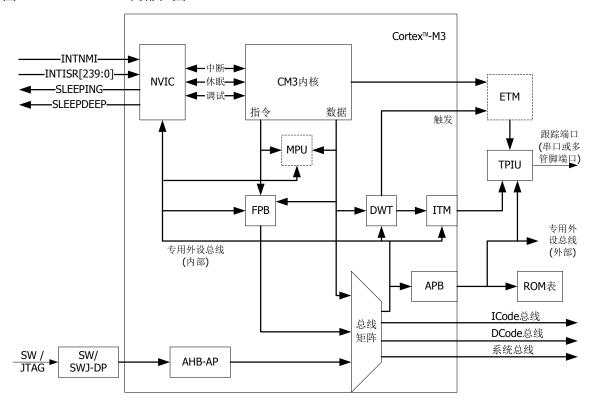

## 2 系统架构

GD32F103xx 系列微控制器的系统架构如下图所示。AHB 总线矩阵是基于 AMBA 3.0 AHB-LITE 技术的,这是一种多层级的 AHB,可确保系统中多个主设备和从设备之间可建立并行的访问路径。AHB 总线矩阵中有四个主设备: Cortex™-M3 内核的 ICode 总线、DCode 总线、系统总线,以及 DMA 控制器。ICode 总线即指令总线,同时也可以从代码存储区(0x0000 0000~0x1FFF FFFF)取出向量送至 Cortex™-M3 内核。DCode 总线即数据总线,主要用于加载/贮存数据,同时也可用于代码存储区的调试访问。与之类似,系统总线主要用于取值/取向量、加载/贮存数据以及调试访问系统存储区。系统存储区可划分为片内 SRAM 区、外部存储映射区以及外设映射区。AHB总线矩阵中有五个从设备: Flash 存储控制器的 ICode、DCode 接口,片内 SRAM,外部存储控制器以及系统 AHB 总线。

系统 AHB 总线与所有的 AHB 外设相连,此外还包含两条 AHB-APB 总线桥,这样可以在系统 AHB 总线以及两个 APB 总线之间实现完全同步连接。两条 APB 总线则与所有的 APB 外设相连。APB1 总线的最高速度限制为 54MHz, APB2 总线则可全速运行(依器件型号而定,最高可达 108MHz)。以上所述设备通过多层级 AHB 总线架构相互连接,如图 2 所示:

#### 图 2 GD32F103xx 系列微控制器系统架构

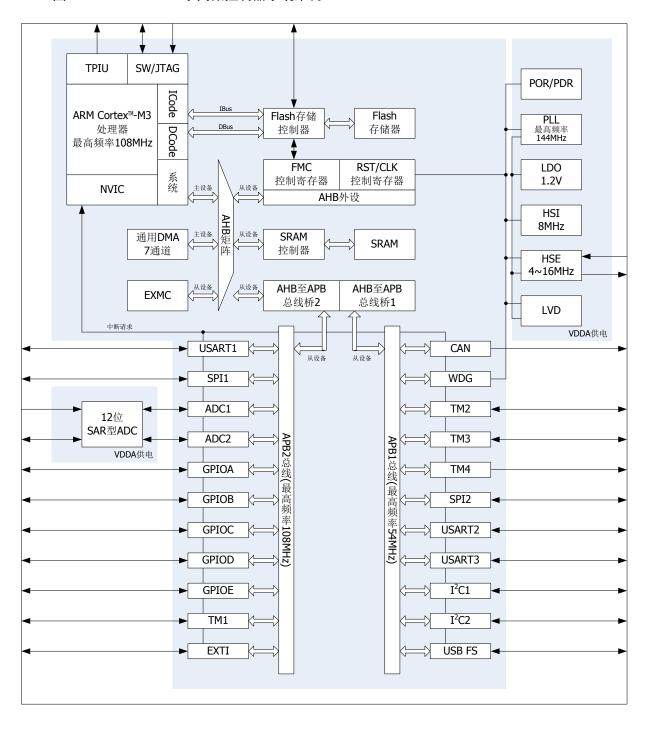

### 3 存储器映射

ARM® Cortex™-M3 处理器采用哈佛型架构,取指和加载/贮存数据各自采用不同的总线。指令代码和数据从逻辑上位于同一寻址空间内,但分别划分在不同的地址段内。程序存储器、数据存储器、寄存器以及 I/O 端口均整合于同一个 4GB 线性寻址空间内(Cortex™-M3 内核总线宽度为 32位,因此最大寻址空间为 4GB)。此外,Cortex™-M3 处理器提供预定义的存储器映射,这样对于用户开发而言,可以降低不同器件供应商芯片的软件差异程度,减少重复性的基础工作。不过,有些存储段是保留用于 Cortex™-M3 处理器系统级外设的。下图是 GD32F103xx 系列微控制器的存储器映射,包括代码、SRAM、外设以及其它预定义存储段。每种类型的每个外设统一分配 1kB空间,这样能够极大简化针对单个外设的地址译码。APB1 外设位于 0x4000 0000~0x4000 FFFF存储段内,APB2 外设位于 0x4001 0000~0x4001 7FFF 存储段内。AHB 外设位于 0x4001 8000~0x4002 FFFF 存储段内。

#### 图 3 GD32F103xx 系列微控制器存储器映射表

#### 3.1 位绑定

为减少"读-修改-写"操作所消耗的时间,Cortex™-M3 处理器提供了位绑定功能(bit-banding),可按位为单位进行原子级的访问。存储器映射表中包含了两个位绑定段,分别位于 SRAM 和外设

中。在位绑定段中,位别名区的某个字会映射到位绑定区的某个位上。

根据如下的映射计算公式,即可体现出位别名区的每个字如何对应于位绑定区的每个位。计算公式为:

位别名地址 = 位绑定基地址 + (字节偏移 $\times$ 32) + (位偏移 $\times$ 4)

#### 其中:

- 位别名地址:位别名区中,对应于指定位的单个字的映射地址

- 位绑定基地址: 位别名区的起始地址

- 字节偏移:包含目标位的字节在位绑定区中的字节偏移

- 位偏移:目标位在该字节中的偏移

举例来说,要想对 0x2000 0200 的第7位进行原子级操作,其对应的位别名地址为:

位别名地址 = 0x2200 0000 + (0x200 \* 32) + (7 \* 4) = 0x2200 401C

如果对 0x2200 401C 进行写操作,那么 0x2000 0200 的第 7 位将会相应变化;如果对 0x2200 401C 进行读操作,那么视 0x2000 0200 的第 7 位状态将会分别返回 0x0000 0001 或 0x0000 0000。

### 3.2 片上 SRAM

GD32F103xx 系列微控制器提供最大 20kB 的片上 SRAM, 起始地址为 0x2000 0000。片上 SRAM 支持按字节(8 位对齐)访问、按半字(16 位对齐)访问、按字(32 位对齐)访问。

#### 3.3 片上 Flash

GD32F103xx 系列微控制器提供最大 128kB 的片上 Flash,支持单周期 32 位的读操作,无任何等待延时。片上 Flash 支持按字节(8位对齐)访问、按半字(16位对齐)访问、按字(32位对齐)访问。Flash 存储器可以单次编程一个半字(16位)或一个字(32位)。Flash 存储器的每个页都可以分别擦除。Flash 存储器可以单次执行全片擦除(除信息块之外)。

Flash 存储器最大 128kB,可分为 128 页,每页 1kB。此外片上还包含一个 2kB 的信息块,用于存储引导加载程序(Boot Loader)。详见下表。

表 1 Flash 模块的组织

| 块         | 名称      | 地址范围                      | 大小  |

|-----------|---------|---------------------------|-----|

|           | 第0页     | 0x0800 0000 ~ 0x0800 03FF | 1kB |

|           | 第1页     | 0x0800 0400 ~ 0x0800 07FF | 1kB |

| 主 Flash 块 | 第2页     | 0x0800 0800 ~ 0x0800 0BFF | 1kB |

|           | •••••   | •••••                     |     |

|           | •••••   | •••••                     |     |

|           | 第 127 页 | 0x0801 FC00 ~ 0x0801 FFFF | 1kB |

| 信息块       | 系统存储器   | 0x1FFF F000 ~ 0x1FFF F7FF | 2kB |

| 旧心坏       | 选项字节    | 0x1FFF F800 ~ 0x1FFF F80F | 16B |

### 4 引导配置

GD32F103xx 系列微控制器提供三种引导源,可通过 BOOT1、BOOT0 管脚来配置。BOOT 管脚的状态是在复位后的第 4 个 SYSCLK 上升沿锁存的,因此用户应确保上电复位或系统复位之后 BOOT1、BOOT0 管脚处于正确的状态,才能确保正确选择引导源。详见下表:

表 2 引导模式

| 引导来源        | 引导模式选择脚 |       |  |

|-------------|---------|-------|--|

| りみ水源        | BOOT1   | воото |  |

| 主 Flash 存储器 | Х       | 0     |  |

| 系统存储器       | 0       | 1     |  |

| 片上 SRAM     | 1       | 1     |  |

执行完上电序列后、或系统复位后,ARM<sup>®</sup> Cortex™-M3 处理器将会依次从 0x0000 0000 地址取出栈项值,从 0x0000 0004 取出引导代码起始地址,之后按照引导代码起始地址开始执行。

根据所选的引导模式,主 Flash 存储器(实际地址 0x0800 0000 开始)或系统存储器(实际地址 0x1FFF F000 开始)将被映射到引导空间内,即从 0x0000 0000 开始。如果用户选用片上 SRAM(实际地址 0x2000 0000 开始)作为引导源,那么在应用程序的初始化代码中,用户必须通过修改 NVIC 异常向量表以及偏移寄存器,将向量表重置到 SRAM 中。

系统存储器中包含内嵌的引导加载程序,可用于对 Flash 存储器编程。在 GD32F103xx 系列微控制器中,引导加载程序是通过 USART1 接口激活工作的。

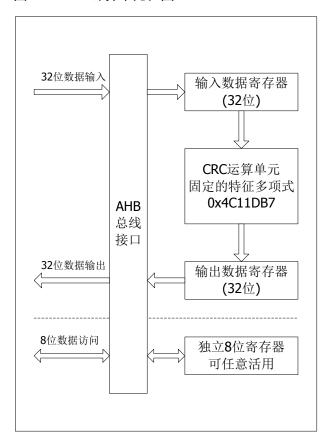

# 5 CRC 计算单元

CRC(Cyclic Redundancy Check,循环冗余校验)是一种常用的错误校验机制,多用于数字化网络以及存储设备中,可校验原始数据是否发生意外改变。

本器件中的 CRC 计算单元仅可计算特征多项式固定、32 位的 CRC 值。

CRC 计算单元具有以下主要特性:

- 32 位数据输入、32 位数据输出。从输入数据到计算结果就绪,所需计算时间为 4 个 AHB 时钟周期。

- 另提供一个与计算无关的通用8位寄存器,用户可自行用于任何目的。

- 固定的特征多项式: **0x4C11DB7**  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X + 1$

#### 图 4 CRC 计算单元框图

#### CRC 计算单元具有以下功能:

- 用于计算 32 位原始数据的 CRC 校验值。CRC\_DR 寄存器接收原始数据,同时也保存计算结果。假如没有事先清除 CRC\_DR 寄存器的内容(软件写 CRC\_CR 寄存器),那么新输入的 32 位原始数据将会基于 CRC\_DR 的原有值继续计算。CRC 计算要消耗 4 个 AHB 总线时钟周期,在此期间 AHB 总线将被 CRC 计算单元挂起,这样可以实现背靠背的数据写入操作、或背靠背的写入-读出操作。

- 本模块提供一个通用 8 位寄存器 CRC\_IDR,供用户自由使用。CRC\_IDR 与 CRC 计算过程毫无关联,在此寄存器中暂存的值可以随时读出。

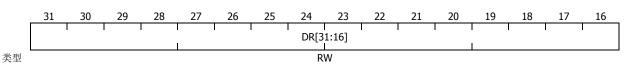

#### 5.1 CRC 寄存器

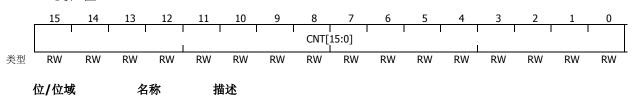

#### CRC 数据寄存器 (CRC\_DR)

地址偏移: 0x00

复位值 : 0xFFFF FFFF

位/位域 名称 描述

31:0 DR[31:0] CRC 计算结果 软件可读可写。

注意: 写入的值是无法回读的, 因为回读到的值是计算后的结果。

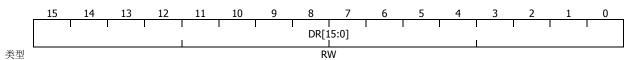

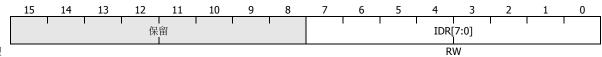

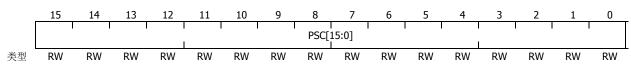

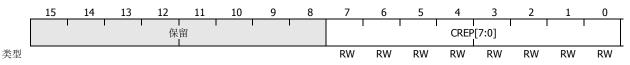

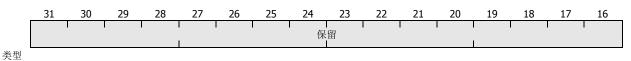

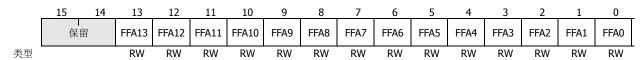

### CRC 独立数据寄存器 (CRC\_IDR)

地址偏移: 0x04

复位值 : 0x0000 0000

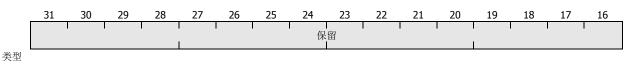

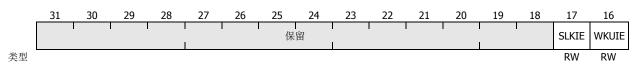

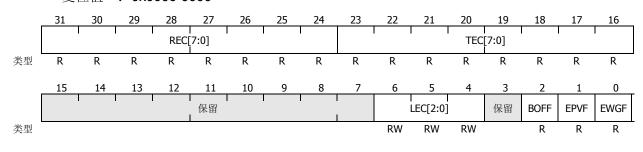

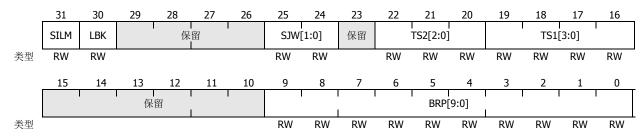

类型

类型

| 位/位域 | 名称       | 描述                 |

|------|----------|--------------------|

| 31:8 | 保留       | 请保持其复位状态           |

| 7:0  | IDR[7:0] | 通用数据寄存器<br>软件可读可写。 |

本位域的值与 CRC 计算无关,因此本字节可由任意外设(或软件)用于任何用途。CRC\_CR 寄存器对此字节无任何影响。

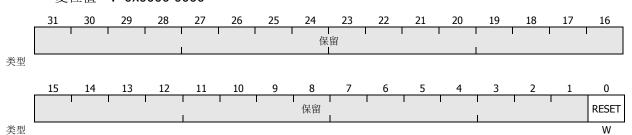

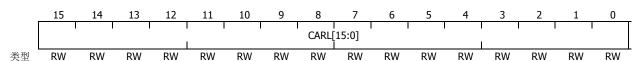

#### CRC 控制寄存器 (CRC\_CR)

地址偏移: 0x08

复位值 : 0x0000 0000

| 位/位域 | 名称    | 描述                                                                              |

|------|-------|---------------------------------------------------------------------------------|

| 31:1 | 保留    | 请保持其复位状态                                                                        |

| 0    | RESET | 复位 CRC 计算单元<br>软件对本位写 1,即可复位 CRC 计算单元并将数据寄存器置为 0xFFFF FFFF。<br>本位只能写 1,由硬件自动清零。 |

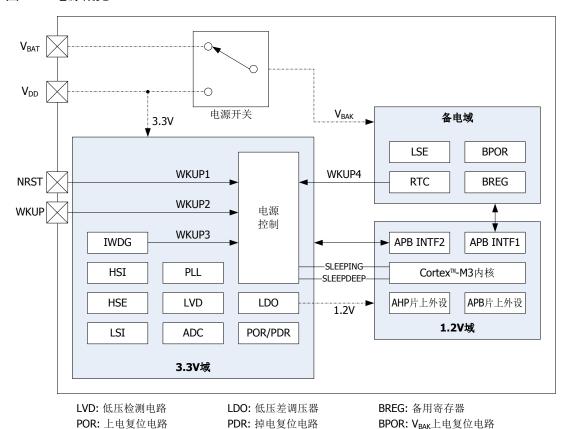

# 第2章 电源控制 (PWR)

## 1 简介

GD32F103xx 系列微控制器一直将功耗视为最重要的设计方向之一,因此在电源控制单元(PWR)中提供三种降低功耗的工作模式,分别是休眠模式、熟睡模式以及待机模式。这些模式可以降低器件功耗,使应用在 CPU 运行时间、运行速度以及能耗这几个相互冲突的指标之间达到最佳的平衡。芯片内电源部分可划分为三个电源域:  $V_{DD}$ 域、1.2V 域以及备电域。 $V_{DD}$ 域的电源来自  $V_{DD}$ 管脚。 $V_{DD}$ 域中的内置 LDO 调压后给 1.2V 域供电。备电域有一个电源开关,当  $V_{DD}$ 电源关闭后从  $V_{BAT}$  供电。

### 2 主要特点

- 三个电源域: V<sub>DD</sub>域、1.2V 域以及备电域

- 三种低功耗工作模式:休眠模式、熟睡模式以及待机模式

- 内部调压器提供 1.2V 电源

- 提供 84 字节由 V<sub>BAK</sub> 供电的备用寄存器,在待机模式下可保存用户的应用数据

- 当供电低于预设的门限时,低压检测电路可产生中断或唤醒事件

- 当 V<sub>DD</sub> 电源关闭时,由电池(V<sub>BAT</sub>)为备用电源域供电

- 提供校正寄存器,保存RTC校正值

# 3 功能描述

下图详细描绘出 PWR 模块以及相关电源域的内部配置。

#### 图 5 电源概览

#### 3.1 备电域

备电域根据内部电源开关的选择,可从  $V_{DD}$  或电池( $V_{BAT}$ )供电。为了在  $V_{DD}$  关断后保持备用寄存器的内容并保持 RTC 的供电,可将  $V_{BAT}$  管脚连接到备用的供电电源(电池或其它电源)。内部电源开关是由  $V_{DD}$  域的掉电复位电路控制的。假如应用设计不采用外部电池,那么推荐将  $V_{BAT}$  通过一个 100nF 的外部陶瓷退耦电容连接到  $V_{DD}$  上。

备电域的复位源包括备电域上电复位(BPOR)以及备电域软件复位。BPOR 信号可将设备保持在复位状态,直至  $V_{BAK}$ 完全上电。应用软件也可以触发备电域软件复位,方法是对 RCC\_BDCR 寄存器中的 BKPRST 写 1。

实时时钟(Real Time Clock,简写为 RTC)单元既可以从内部低速 RC 振荡电路(LSI)获取时钟,也可以从外部低速晶体振荡器(LSE)获取时钟。当 V<sub>DD</sub> 掉电后,RTC 单元只能采用 LSE 作为时钟源。在执行 WFI/WFE 指令进入节电模式之前,Cortex™-M3 需要先将预期的唤醒时间写入比较寄存器,并且使能唤醒功能以产生 RTC 定时器唤醒事件。这样在进入节电模式一定时间后,当比较匹配事件产生时,便会产生 RTC 闹钟事件唤醒器件。关于 RTC 的配置及操作,详见 RTC 的相关章节。

备电域提供了  $42 \land 16$  位寄存器、总计 84 字节,用于存储用户的应用数据。这些寄存器由  $V_{BAK}$  供电,当  $V_{DD}$  电源关闭后可持续供电。只有当备电域上电复位或备电域软件复位时,备用寄存器的内容才会复位。

#### 3.2 V<sub>DD</sub> 电源域

所有的模拟模块都处于 V<sub>DD</sub> 电源域内,包括 LDO (电压整流器)、LVD (低压检测模块)、POR/PDR (上电复位/掉电复位模块)、ADC (模数转换器)、HSI (内部高速 RC 振荡电路)、HSE (外部高速晶体振荡电路)、LSI (内部低速 RC 振荡电路)、PLL (锁相环电路)、IWDG (独立式看门狗)以及所有管脚。LDO 为 1.2V 电源域供电,提供三种工作模式:运行模式(最大功耗)、熟睡模式(低功耗)、待机模式(关断)。LVD 用于检测 V<sub>DD</sub> 是否低于预设值,一旦低于预设值则将产生中断告知 Cortex™-M3 内核。HSI 是默认的系统时钟源,其频率校正到 8MHz 左右。复位后,系统时钟将由 HSI 直接驱动。

#### 3.3 1.2V 电源域

Cortex<sup>TM</sup>-M3 内核逻辑部分、AHB/APB 外设、与备电域/ $V_{DD}$  电源域的 APB 接口等主要功能模块均位于此电源域内。当 1.2V 上电后,POR 单元将在 1.2V 电源域产生复位序列。复位完成后,如果要进入指定的节电模式,必须先配置相关的控制位,之后一旦执行 WFI(Wait For Interrupt,等待中断)指令或 WFE(Wait For Event,等待事件)指令,器件便可进入该节电模式。关于这方面的详细内容,将在后续章节予以说明。

#### 3.4 节电模式

系统复位或上电复位之后,GD32F103xx 系列微控制器默认开启所有功能,且所有电源域全部通电。若用户希望降低功耗,可降低系统时钟(HCLK、PCLK1、PCLK2),或关闭未用外设的时钟。此外为了进一步降低功耗,器件提供三种节电模式,分别为休眠模式、熟睡模式、待机模式。

#### 休眠模式

体眠模式对应于 Cortex™-M3 的 SLEEPING 工作模式。在休眠模式下,只关闭 Cortex™-M3 内核的时钟。要进入休眠模式,只需将 Cortex™-M3 系统控制寄存器的 SLEEPDEEP 位清零,之后执行 WFI 指令或 WFE 指令。若通过 WFI 指令进入休眠模式,则任意中断都可以唤醒系统。若通过 WFE 指令进入休眠模式,则任意唤醒事件都可以唤醒系统。这种节电模式的唤醒时间最短,因为无需浪费时间在中断入口或出口。

#### 熟睡模式

熟睡模式对应于 Cortex™-M3 的 SLEEPDEEP 工作模式。在熟睡模式下,1.2V 电源域的所有时钟全部关闭,HSI、HSE 以及 PLL 也全部禁用。此时的 LDO 可以工作在正常模式或低功耗模式下,取决于 PWR\_CTL 寄存器中 LDO\_LP 位的设置。要进入熟睡模式之前,需要将 Cortex™-M3 系统

控制寄存器的 SLEEPDEEP 位置位,并将 PWR\_CTL 寄存器的 SDBM 位清零。之后执行 WFI 指令或 WFE 指令后即可进入熟睡模式。任何来自 EXTI 的中断或者唤醒事件都能将系统从熟睡模式中唤醒。当退出熟睡模式时,HSI 将被选作系统时钟。请注意,假如熟睡时 LDO 处于低功耗模式,那么唤醒时还将需要额外的延时。

#### 待机模式

待机模式也是基于 Cortex™-M3 的 SLEEPDEEP 工作模式的。在待机模式下,整个 1.2V 电源域全部停止供电,LDO 关断,HSI、HSE、PLL 全部禁用。要进入待机模式,应将 Cortex™-M3 系统控制寄存器中的 SLEEPDEEP 位置位,并且将 PWR\_CTL 寄存器中的 DSPD 置位。之后执行 WFI 指令或 WFE 指令后,系统即进入待机模式。待机模式有四个唤醒源,分别是: NRST 管脚的外部复位信号、RTC 闹钟信号、IWDG 复位信号、WKUP 管脚的上升沿。借助待机模式可以获得最低的功耗,但相应的唤醒时间也是最长的。此外,在待机模式下所有 SRAM 和寄存器(除备用寄存器外)的内容将全部丢失。退出待机模式时将会产生上电复位序列,Cortex™-M3 内核会从 0x0000 0000 开始重新执行指令。

表 3 节电模式小结

| 模式名称   | 睡眠模式                                               | 深度睡眠模式                                              | 待机模式                                         |

|--------|----------------------------------------------------|-----------------------------------------------------|----------------------------------------------|

| 描述     | 仅 CPU 时钟被关闭                                        | ■ 1.2V 电源域的所<br>有时钟全部关闭<br>■ HSI、HSE 以及 PLL<br>均被禁用 | ■ 1.2V 电源域停止<br>供电<br>■ HSI、HSE以及PLL<br>均被禁用 |

| LDO 状态 | 开启                                                 | 开启或低功耗模式                                            | 关闭                                           |

| 配置     | SLEEPDEEP = 0                                      | SLEEPDEEP = 1                                       | SLEEPDEEP = 1                                |

| 印止     |                                                    | SDBM = 0                                            | SDBM = 1                                     |

| 入口     | WFI 或 WFE                                          | WFI 或 WFE                                           | WFI 或 WFE                                    |

| 唤醒     | 若从 WFI 进入,则任<br>何中断均可唤醒<br>若从 WFE 进入,则任<br>何事件均可唤醒 | 来自 EXTI 线的任何中<br>断或事件                               | ■ NRST 管脚 ■ WKUP 管脚 ■ RTC 闹钟 ■ IWDG 复位信号     |

| 唤醒延时   | 无                                                  | HSI 唤醒时间<br>LDO 唤醒时间(假如<br>LDO 处于低功耗模式)             | 上电序列                                         |

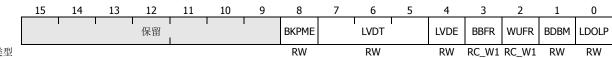

# 4 PWR 寄存器

外设寄存器可按半字(16位)或字(32位)访问。

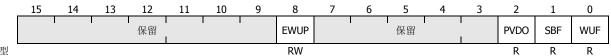

#### 4.1 电源控制寄存器 (PWR\_CTL)

地址偏移: 0x00

复位值 : 0x0000 0000 (从待机模式唤醒后复位)

类型

类型

| 位/位域 | 名称        | 描述                                                                                                               |

|------|-----------|------------------------------------------------------------------------------------------------------------------|

| 31:9 | 保留        | 请保持其复位状态                                                                                                         |

| 8    | BKPWE     | 备电域写入使能<br>0: 禁用对备用寄存器的写操作<br>1: 使能对备用寄存器的写操作<br>复位后,所有对备用寄存器的写操作均无效。要想对这些寄存器进行写操作,<br>必须先将此标志位置位。               |

| 7:5  | LVDT[2:0] | 低压检测电路门限<br>000: 2.2V<br>001: 2.3V<br>010: 2.4V<br>011: 2.5V<br>100: 2.6V<br>101: 2.7V<br>110: 2.8V<br>111: 2.9V |

| 4    | LVDE      | 低压检测电路使能<br>0:禁用低压检测电路<br>1:使能低压检测电路                                                                             |

| 3    | SBFR      | 待机标志复位<br>0: 无实际效果<br>1: 清零待机标志位<br>本位始终回读为 0。                                                                   |

| 2    | WUFR      | 唤醒标志复位<br>0: 无实际效果<br>1: 清零唤醒标志位<br>本位始终回读为 0。                                                                   |

| 1    | SDBM      | 待机模式<br>0: 当 Cortex™-M3 进入 DEEPSLEEP 模式时,器件进入熟睡模式<br>1: 当 Cortex™-M3 进入 DEEPSLEEP 模式时,器件进入待机模式                   |

| 0    | LDOLP     | LDO 低功耗模式<br>0: 熟睡模式下, LDO 正常工作<br>1: 熟睡模式下, LDO 按低功耗方式工作                                                        |

#### 4.2 电源状态寄存器 (PWR\_ST)

地址偏移: 0x04

复位值 : 0x0000 0000 (从待机模式唤醒后不复位)

类型

| 位/位域 | 名称   | 描述                                                                                                                                                              |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:9 | 保留   | 请保持其复位状态                                                                                                                                                        |

| 8    | WUPE | WAKEUP 管脚使能<br>0: 禁用 WAKEUP 管脚功能<br>1: 使能 WAKEUP 管脚功能<br>假如在进入节电模式之前将 WUPE 置位,则 WAKEUP 管脚的上升沿可将系统<br>从节电模式中唤醒。<br>注意:由于 WAKEUP 管脚是高电平有效的,因此本位置位时管脚将会打开内<br>部下拉。 |

| 7:3  | 保留   | 请保持其复位状态                                                                                                                                                        |

| 2    | LVDF | 低压检测电路状态标志 0:未产生低压事件(V <sub>DD</sub> 始终高于预设的门限值) 1:检测到低压事件(V <sub>DD</sub> 低于或等于预设的门限值)                                                                         |

| 1    | SBF  | 待机标志 0: 系统未处于待机模式中 1: 系统处于待机模式中 仅当发生上电复位/掉电复位、或者将 PWR_CTL 寄存器的 SBFR 置位时,本标志位才会清零。                                                                               |

| 0    | WUF  | 唤醒标志 0: 未发生过唤醒事件 1: 检测到来自 WKUP 管脚或 RTC 闹钟的唤醒事件 仅当发生上电复位/掉电复位、或者将 PWR_CTL 寄存器的 SBFR 置位时,本                                                                        |

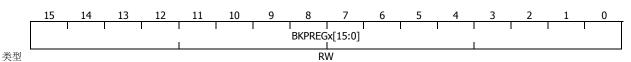

#### 4.3 备用数据寄存器 x (BKP\_REGx) ( $x = 1 \sim 42$ )

标志位才会清零。

地址偏移: 0x04~0x28, 0x40~0xBC

复位值 : 0x0000

| 位/位域  | 名称      | 描述                                                                                      |

|-------|---------|-----------------------------------------------------------------------------------------|

| 31:16 | 保留      | 请保持其复位状态                                                                                |

| 15:0  | BKPREGx | 备用寄存器 $x$ ( $x = 1\sim42$ )<br>这些寄存器用于通用数据存储。即使 $1.2V$ 电源域停止供电,BKPREGx 寄存器<br>的内容也不会丢失。 |

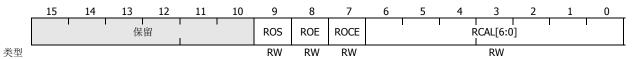

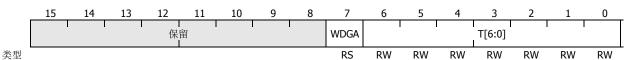

### 4.4 RTC 时钟寄存器 (BKP\_RTCC)

地址偏移: 0x2C

复位值 : 0x0000

| 位/位域  | 名称        | 描述                                                                                                                                                                 |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:10 | 保留        | 请保持其复位状态                                                                                                                                                           |

| 9     | ROS       | RTC 输出选择 0: 选择 RTC 闹钟输出信号作为 RTC 的输出信号 1: 选择 RTC 秒输出信号作为 RTC 的输出信号 只有当备电域复位时,本标志位才会复位。                                                                              |

| 8     | ROE       | RTC 输出使能 0: 禁用 RTC 输出 1: 使能 RTC 输出 使能之后,RTC 输出信号将通过 BR 管脚输出。 只有当备电域复位时,本标志位才会复位。                                                                                   |

| 7     | RCOE      | RTC 时钟输出使能 0: 禁用 RTC 时钟输出 1: 使能 RTC 时钟输出 1: 使能 RTC 时钟输出 使能之后,RTC 时钟信号将通过 BR 管脚输出。ROE 的优先级高于 RCOE,若 ROE 置位,则不管 RCOE 的值为何,BR 管脚输出的都是 RTC 输出信号。仅当上电复位/掉电复位后,本标志位才会复位。 |

| 6:0   | RCAL[6:0] | RTC 时钟校正值<br>本位域的数值代表每 2 <sup>20</sup> 个时钟脉冲将忽略多少个时钟脉冲。                                                                                                            |

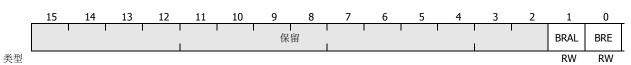

# 4.5 备用域复位控制寄存器(BKP\_BRC)

地址偏移: 0x30

复位值 : 0x0000

| 位/位域  | 名称   | 描述                                                                               |

|-------|------|----------------------------------------------------------------------------------|

| 31:16 | 保留   | 请保持其复位状态                                                                         |

| 1     | BRAL | BR 管脚有效电平<br>0: 高电平有效<br>1: 低电平有效                                                |

| 0     | BRE  | 备电域复位使能 0: BR 管脚用作 GPIO 1: BR 管脚专用于备电域复位功能。当 BR 管脚检测到有效电平后,将清除所有 BKPREGx 寄存器的内容。 |

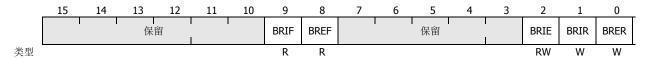

### 4.6 备用域复位中断寄存器(BKP\_BRI)

地址偏移: 0x34

复位值 : 0x0000

| 位/位域  | 名称   | 描述                                                                             |

|-------|------|--------------------------------------------------------------------------------|

| 31:10 | 保留   | 请保持其复位状态                                                                       |

| 9     | BRIF | 备电域复位中断标志<br>0:未检测到 BR 中断<br>1:检测到 BR 中断<br>向 BRIR 写 1,或者当 BRIE 为 0 时,本标志位将复位。 |

| 8     | BREF | 备电域复位事件标志 0: 未检测到 BR 事件 1: 检测到 BR 事件 向 BRER 写 1 后,本标志位将复位。                     |

| 7:3   | 保留   | 请保持其复位状态                                                                       |

| 2     | BRIE | 备电域复位中断使能 0: 禁用备电域复位中断 1: 使能备电域复位中断 仅当发生系统复位并且从待机模式唤醒后,本标志位才会复位。               |

| 1     | BRIR | 备电域复位中断复位<br>0: 无意义<br>1: 复位 BRIF 标志<br>本标志位始终回读为 0。                           |

| 0     | BRER | 备电域复位事件复位<br>0: 无意义<br>1: 复位 BREF 标志<br>本标志位始终回读为 0。                           |

# 第3章 复位及时钟控制单元(RCCU)

## 1 复位控制单元(RCU)

#### 1.1 简介

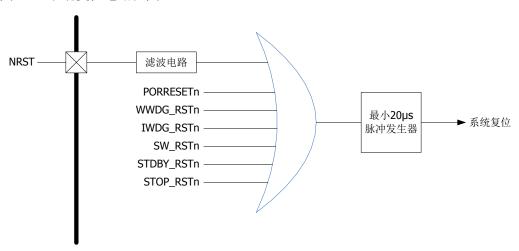

GD32F103xx 系列微控制器的复位控制单元负责控制三种类型的复位:上电复位、系统复位以及备电域复位。上电复位通常又称为冷复位,能够在上电过程中复位除备电域外的整个系统。系统复位可复位处理器内核以及外设 IP 部分,除 SW-DP 控制器及备电域以外。备电域复位则专门用于复位备电域。复位可通过外部信号触发,可通过内部事件触发,还能通过复位发生器触发。本章将对这些内容进行详细说明。

#### 1.2 功能描述

#### 电源复位

电源复位可通过外部复位信号产生(例如上电复位/掉电复位),也可以通过内部复位发生器产生(退出待机模式时)。电源复位将所有寄存器(除备用域外)恢复到初始值。当内部 LDO 调压器已准备好提供 1.2V 电源后,低电平有效的电源复位信号将会转为失效状态。RESET 异常服务子程序的向量固定位于存储器映射表的 0x0000 0004 处。

#### 图 6 系统复位电路框图

#### 系统复位

系统复位可以由下列事件产生:

■ 上电复位 (PORRESETn)

- 外部管脚复位(NRST)

- 窗口式看门狗定时器复位(WWDG\_RSTn)

- 独立式看门狗定时器复位(IWDG RSTn)

- Cortex<sup>™</sup>-M3 应用中断及复位控制寄存器中的 SYSRESETREQ 置位 (SW RSTn)

- 若用户选项字的 nRST\_STDBY 被改写,则每当试图进入待机模式时都将产生系统复位 (STOP RSTn)

- 若用户选项字的 nRST\_STOP 被改写,则每当试图进入停机模式时都将产生系统复位 (STOP\_RSTn)

对任意复位源(不论是外部复位还是内部复位),系统复位脉冲发生器可保障产生最短 **20µs** 的低电平脉冲。

#### 备电域复位

将备电域控制寄存器中的 BKPRST 置位,或者产生备电域上电复位(假如  $V_{DD}$  和  $V_{BAT}$  之前都已经掉电,则  $V_{DD}$  或  $V_{BAT}$  上电即产生备电域上电复位),即可将备电域复位。

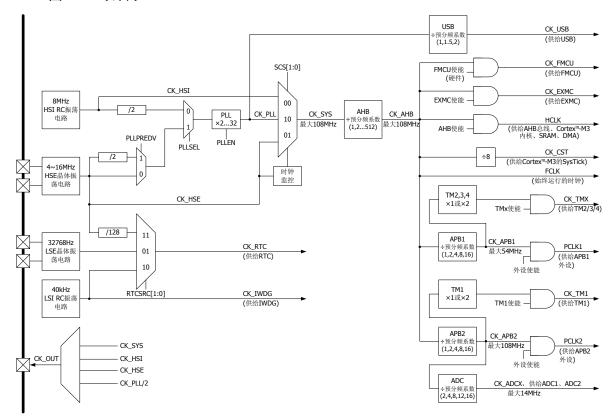

### 2 时钟控制单元(CCU)

#### 2.1 简介

时钟控制单元提供各种频率控制及时钟控制功能。这包括一路内部高速 RC 振荡电路(HSI)、一路外部高速晶体振荡电路(HSE)、一路内部低速 RC 振荡电路(LSI)、一路外部低速晶体振荡电路(LSE)、一路锁相环(PLL)、一个 HSE 时钟监控电路、时钟预分频器、时钟多路复用开关以及时钟整形电路。

AHB 总线、APB 总线以及 Cortex™-M3 内核的时钟都是从系统时钟(CK\_SYS)分频得到的。系统时钟可以从 HSI、HSE 或 PLL 获得。系统时钟(CK\_SYS)的最高频率可达 108MHz。独立式看门狗定时器以及实时时钟(RTC)则采用 LSI 或 LSE 作为时钟源。

#### 图 7 时钟树

AHB 频率、高速 APB(APB2)以及低速 APB(APB1)时钟域频率,可分别通过预分频器进行配置。AHB 和 APB2 时钟域的最高频率可达 108MHz,APB1 时钟域的最高频率可达 54MHz。Cortex™-M3 系统定时器(SysTick)的外部时钟是由 AHB 时钟(HCLK)8 分频后得到的。SysTick 模块要么采用这个时钟,要么直接采用 AHB 时钟(HCLK),这可以通过系统定时器控制及状态寄存器进行设置。模数转换器都是由高速时钟域(APB2)提供时钟的,分频系数可从 2、4、6、8、12 或 16 中选择。

假如 APB 预分频系数为 1,那么定时器时钟频率就是 AHB 频率除以 1,否则就是 AHB 频率除以 APB 预分频系数的一半。

#### 2.2 主要特点

- 4~16MHz 外部高速晶体振荡电路(HSE)

- 8MHz 内部高速 RC 振荡电路 (HSI)

- 32.768kHz 外部低速晶体振荡电路(LSE)

- 40kHz 内部低速 RC 振荡电路(LSI)

- PLL 时钟源可以来自 HSE 或 HSI

- HSE 时钟监控

#### 2.3 功能描述

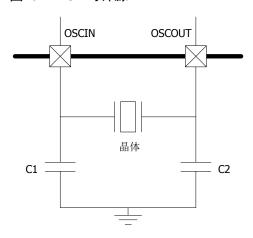

#### 备用域复位

外部高速晶体振荡电路(HSE)支持 4~16MHz 的外部晶体,可产生高精度的时钟源用作系统时钟。工作时,必须将特定频率的晶体连接到两根 HSE 管脚之间,并且晶体与管脚的距离应尽可能短。为确保振荡可靠性,还需要连接特定的外部电阻和电容元件。

#### 图 8 HSE 时钟源

通过全局时钟控制寄存器 GCC\_GCCR 的 HSEEN 位,可以打开或关闭 HSE 晶体振荡电路。查询全局时钟控制寄存器 RCC\_GCCR 的 HSESTB 标志位,可表明外部高速晶体的振荡是否稳定。HSE 上电时并不会立即投入使用,直到 HSESTB 标志由硬件置位后才行。这个延迟时间就是众所周知的"晶体起振时间"。当 HSE 工作稳定之后,若全局时钟控制寄存器 RCC\_GCCR 的 HSESTBIE=1,则会产生中断。此时 HSE 时钟才能够用作系统时钟源或用作 PLL 的输入时钟。

通过设置全局时钟控制寄存器 RCC\_GCCR 的 HSEBPS 位以及 HSEEN 位,即可选中外部时钟旁通模式。CK\_HSE 等于驱动 OSC\_IN 管脚的外部时钟。

#### HSI 时钟

内部高速 RC 振荡电路 HSI,具有 8MHz 的固定频率,是器件上电后的默认时钟源。由于无需外接元件,HSI 振荡电路提供了一种低成本的时钟源。通过设置全局时钟控制寄存器 RCC\_GCCR 的 HSIEN 位,可开启或关闭 HSI 的 RC 振荡电路。查询全局时钟控制寄存器 RCC\_GCCR 的 HSIRSTB 标志,可表明内部 RC 振荡电路是否已经工作稳定。HSI 振荡电路的起振时间要比 HSE 晶体振荡电路的起振时间短。当 HSI 工作稳定之后,若全局时钟控制寄存器 RCC\_GCCR 中的 HSISTBIE=1,则会产生中断。HSI 时钟也可以用作 PLL 的时钟输入。

HSI 的频率精度可以由制造商校正,但其运行频率仍不及 HSE 精准。选择何种振荡类型,需结合应用设计要求、工作环境以及成本要求进行综合考量。

若 HSE 或 PLL 作为系统时钟源,为了尽量减少系统从停机模式中恢复所需的时间,当系统刚刚唤醒时会强制使用 HSI 作为系统时钟。

#### **PLL**

内部锁相环 PLL 可提供 16~108MHz 的时钟输出,具体输出频率为基频(4~16MHz)的 2~32 倍。通过全局时钟控制寄存器 RCC\_GCCR 的 PLLEN 位,可选择开启或关闭 PLL。查询全局时钟控制寄存器 RCC\_GCCR 的 PLLSTB 标志,可表明 PLL 时钟是否已经稳定。当 PLL 工作稳定后,若全局时钟控制寄存器 RCC\_GCCR 的 PLLSTBIE=1,则会产生中断。

#### LSE 时钟

32.768kHz 外部低速晶体(或陶瓷谐振器)振荡电路,为实时时钟模块提供了低功耗、高精度的时钟源。通过备电域控制寄存器 RCC\_BDCR 的 LSEEN 位,可选择开启或关闭 LSE 振荡电路。查询备用域控制寄存器 RCC\_BDCR 的 LSESTB 标志,可表明 LSE 时钟是否已经稳定。当 LSE 工作稳定后,若备用域控制寄存器 RCC\_BDCR 中的 LSESTBIE=1,则将产生中断。

通过设置备用域控制寄存器 RCC\_BDCR 中的 LSEBPS 位以及 LSEEN 位,可选择外部时钟的旁通模式。CK\_LSE 等于驱动 OSC32\_IN 管脚的外部时钟频率。

#### LSI 时钟

内部低速 RC 振荡电路的频率大约为 40kHz,是供给实时时钟电路或独立式看门狗定时器的低功耗时钟源。由于无需外接元件,LSI 提供了低成本的时钟源。通过全局时钟控制寄存器 RCC\_GCCR 的 LSIEN 位,可选择开启或关闭 LSI 的 RC 振荡电路。查询全局时钟控制寄存器 RCC\_GCCR 的 LSISTB 标志,可表明 LSI 时钟是否已经工作稳定。当 LSI 工作稳定后,若全局时钟控制寄存器 RCC GCCR 中的 LSISTBIE=1,则将产生中断。

#### 系统时钟(SYS\_CLK)的选择

系统复位后,默认的 CK\_SYS 时钟源为 HSI,也可以通过修改全局时钟配置寄存器 RCC\_GCFGR 中的系统时钟切换 SCS 位域切换为 HSE 或 PLL。当改变 SCS 位域的值时,CK\_SYS 仍将采用之前的时钟源进行工作,直到目标时钟源稳定后才会切换。如果某个时钟源是直接连接 CK\_SYS 或 PLL的,那么该时钟源是不可停止的。

#### HSE 时钟监控器(CKM)

通过全局时钟控制寄存器 RCC\_GCCR 的 CKMEN (HSE 时钟监控使能位),可使能 HSE 时钟监控功能。此功能应在 HSE 起振延时之后开启,且应在 HSE 停止振荡之后关闭。一旦检测到 HSE 停振,HSE 将会自动被禁用,此时全局时钟控制寄存器 RCC\_GCCR 中的 CKMF(HSE 时钟阻塞标志)将会置位,同时还会产生一个 HSE 故障事件。该故障事件的中断连接在 Cortex™-M3 的不可屏蔽中断 NMI 上。假如 HSE 被选作 CK\_SYS 或 PLL 的时钟源,那么 HSE 故障将会强制将 CK\_SYS 切换到 HSI,并且自动关闭 PLL。

#### 时钟输出能力

时钟输出的有效频率范围为 32kHz 到 54MHz。通过全局时钟配置寄存器 RCC\_GCFGR 的 CKOUTSRC(CKOUT 时钟源选择位域),可选择数种时钟信号。请注意,要输出所选的时钟信号,相应的 GPIO 管脚必须配置为适当的备选功能 I/O (AFIO) 模式。

表 4 CKOUT 的时钟源选择

| CKOUTSRC | 所选时钟源    |

|----------|----------|

| 0xx      | 无时钟      |

| 100      | CK_SYS   |

| 101      | CK_HSI   |

| 110      | CK_HSE   |

| 111      | CK_PLL/2 |

## 3 RCCU 寄存器

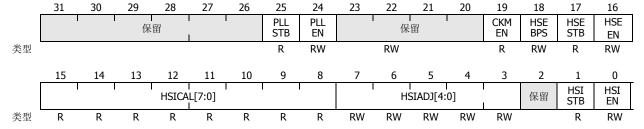

#### 3.1 全局时钟控制寄存器(RCC\_GCCR)

地址偏移: 0x00

复位值 : 0x0000 XX83 (其中 X 代表未定义)

| 位/位域        | 名称           | 描述                                                                                               |

|-------------|--------------|--------------------------------------------------------------------------------------------------|

| 31:26<br>25 | 保留<br>PLLSTB | 请保持其复位状态 PLL 时钟稳定标志                                                                              |

|             |              | 由硬件置位,表明 PLL 输出时钟已工作稳定,可供使用。<br>0: PLL 未稳定<br>1: PLL 已稳定                                         |

| 24          | PLLEN        | PLL 使能<br>由软件置位及清零。假如 PLL 用作系统时钟源,则本位不得清零。当进入停<br>机或待机模式时,硬件自动将本位清零。<br>0: PLL 被关闭<br>1: PLL 被打开 |

| 23:20       | 保留           | 请保持其复位状态                                                                                         |

| 位/位域 | 名称          | 描述                                                                                                                                                                                                                                                                        |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19   | CKMEN       | HSE 时钟监控使能 0: 禁用对外部 4~16MHz 晶体振荡电路(HSE)的监控功能 1: 使能对外部 4~16MHz 晶体振荡电路(HSE)的监控功能 1: 使能对外部 4~16MHz 晶体振荡电路(HSE)的监控功能 当硬件检测到 HSE 时钟发生阻塞、始终保持低电平或高电平时,内部硬件将系统时钟切换到内部高速 RC 振荡电路(HSI)。要恢复初始系统时钟源,要么通过外部复位,要么通过上电复位,或者软件清零 CKSF。 请注意: 当使能 HSE 时钟监控功能后,不管 HSIEN 的状态如何,系统都会自动使能 HSI。 |

| 18   | HSEBPS      | 外部晶体振荡电路(HSE)时钟旁通模式使能<br>仅当 HSEEN 为 0 时,本位才可以执行写操作。<br>0:禁用 HSE 旁通模式<br>1:使能 HSE 旁通模式                                                                                                                                                                                     |

| 17   | HSESTB      | 外部晶体振荡电路(HSE)时钟稳定标志<br>由硬件置位,表明 HSE 振荡电路已工作稳定,可供使用。<br>0: HSE 振荡电路未稳定<br>1: HSE 振荡电路己稳定                                                                                                                                                                                   |

| 16   | HSEEN       | 外部高速晶体振荡电路(HSE)使能<br>由软件置位及清零。假如 HSE 用作系统时钟源或 PLL 时钟源,则本位不得清<br>零。当进入停机或待机模式时,硬件自动将本位清零。<br>0: 禁用外部 4~16MHz 晶体振荡电路<br>1: 使能外部 4~16MHz 晶体振荡电路                                                                                                                              |

| 15:8 | HSICAL[7:0] | 内部高速 RC 振荡电路校准值<br>此数值将在上电时自动加载。                                                                                                                                                                                                                                          |

| 7:3  | HSIADJ[4:0] | 内部高速 RC 振荡电路时钟调整值<br>此位域由软件进行设定。调整值将会加入校准值中,作为 RC 振荡电路的实际<br>校准值。用户应借助调整值将 HSI 调整至 8MHz±1%范围内。                                                                                                                                                                            |

| 2    | 保留          | 请保持其复位状态                                                                                                                                                                                                                                                                  |

| 1    | HSISTB      | 内部高速 RC 振荡电路(HSI)时钟稳定标志<br>由硬件置位,表明 HSI 振荡电路已工作稳定,可供使用。<br>0: HSI 振荡电路未稳定<br>1: HSI 振荡电路已稳定                                                                                                                                                                               |

| 0    | HSIEN       | 内部高速 RC 振荡电路(HSI)使能由软件置位及清零。假如 HSI 用作系统时钟源,则本位不得清零。当进入停机或待机模式时,硬件自动将本位置位。此外,若 HSECKM 置位,则当 HSE时钟发生阻塞、始终保持低电平或高电平时,硬件也会自动将本位置位。0: 禁用内部 8MHz RC 振荡电路1: 使能内部 8MHz RC 振荡电路                                                                                                    |

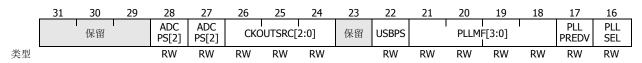

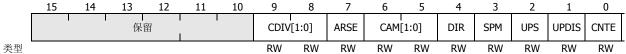

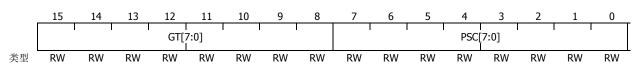

### 3.2 全局时钟配置寄存器(RCC\_GCFGR)

地址偏移: 0x04

复位值 : 0x0000 0000

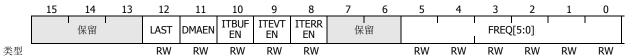

|    | 15    | 14     | 13 | 12       | 11 | 10 | 9       | 8  | 7   | 6     | 5      | 4  | 3    | 2     | 1    | 0    |

|----|-------|--------|----|----------|----|----|---------|----|-----|-------|--------|----|------|-------|------|------|

|    | ADCPS | 5[1:0] | AF | PBPS[2:0 | D] | AF | B1PS[2: | 0] |     | AHBPS | 5[3:0] |    | SCSS | [1:0] | SCS[ | 1:0] |

| 光刑 | RW    | RW     | RW | RW       | RW | RW | RW      | RW | RW/ | RW    | RW     | RW | R    | R     | RW   | RW   |

| 型 | RW    | KW | RW   | RW    | RW                        | RW                                           | KW                                           | KW                                | KW       | RW   | RW | RW           | К | К | RW  | RW |

|---|-------|----|------|-------|---------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------|----------|------|----|--------------|---|---|-----|----|

|   | 位/位域  |    | 名    | 称     | 描                         | 述                                            |                                              |                                   |          |      |    |              |   |   |     |    |

|   | 31:29 |    | 保    | 留     | 请                         | 保持其                                          | 复位状                                          | 状态                                |          |      |    |              |   |   |     |    |

|   | 28    |    | ADCF | PS[2] |                           | DCPS 智<br>见后述                                |                                              | 的第2位                              | <u>)</u> |      |    |              |   |   |     |    |

|   | 27    |    | PLLM | 1F[4] |                           | LMF 魯<br>见后述                                 |                                              | <b>ሳ第 4</b> 位                     | Ĭ.       |      |    |              |   |   |     |    |

|   | 26:24 |    | CKOU | TSRC  | 由<br>0x<br>10<br>10<br>11 | 软件置<br>x: 未认<br>0: 选<br>0: 选<br>0: 选<br>0: 选 | 用内部<br>用外部                                   | 青零。<br>钟源<br>时钟源<br>高速 <b>R</b> ( | 体振荡      | 电路(F |    | 为时钟》<br>5为时钟 |   |   |     |    |

|   | 23:22 |    | USE  | BPS   | 用<br>为<br>00<br>01<br>10  | 于配置<br>48MH<br>): CK_F<br>: CK_F             | ! USB  <br>z。如!<br>PLL/1.5<br>PLL<br>PLL/2.5 | 果 USB I                           | 预分频 🤊    |      |    | 置位或清<br>比位域不 |   |   | 的时钟 | 必须 |

| 位/位域  | 名称         | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21:18 | PLLMF[3:0] | PLL 倍频系数 结合前面的 PLLMF[4]组成 5 位的位域,由软件配置以定义 PLL 的倍频系数。000001:输入时钟×2 00001:输入时钟×4 00011:输入时钟×5 00100:输入时钟×6 00101:输入时钟×7 00110:输入时钟×8 00111:输入时钟×10 01001:输入时钟×11 01001:输入时钟×12 01011:输入时钟×13 01100:输入时钟×15 01110:输入时钟×16 01111:输入时钟×16 10100:输入时钟×17 10000:输入时钟×18 10010:输入时钟×18 10010:输入时钟×20 10100:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 10101:输入时钟×21 11010:输入时钟×21 11010:输入时钟×21 11010:输入时钟×21 11010:输入时钟×21 11010:输入时钟×21 11010:输入时钟×21 11011:输入时钟×21 11011:输入时钟×21 11011:输入时钟×21 11011:输入时钟×21 11011:输入时钟×21 11011:输入时钟×21 11011:输入时钟×31 11111:输入时钟×31 11111:输入时钟×31 |

| 17    | PLLPREDV   | HSE 作为 PLL 时钟源的预分频选择<br>当 HSE 作为 PLL 的时钟源时,本位决定 HSE 是否需要分频后再输入 PLL。由<br>软件置位或清零。<br>0: HSE 时钟直接输入 PLL<br>1: CK_HSE/2 输入 PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16    | PLLSEL     | PLL 时钟源选择<br>由软件置位或清零,决定 PLL 的时钟源。<br>0: CK_HSI/2 作为 PLL 的时钟源<br>1: 选用 HSE 作为 PLL 的时钟源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15:14 | ADCPS[1:0] | ADC 时钟预分频选择<br>结合前面的 ADCPS[2]组成 3 位的位域,由软件配置 ADC 时钟频率。<br>000: CK_APB2/2<br>001: CK_APB2/4<br>010: CK_APB2/6<br>011: CK_APB2/8<br>100: CK_APB2/2<br>101: CK_APB2/12<br>110: CK_APB2/16                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 位/位域  | 名称          | 描述                                                                                                                                                                                                                                              |

|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:11 | APB2PS[2:0] | APB2 时钟预分频系数选择<br>由软件配置 APB2 时钟预分频系数。<br>0xx: 直接使用 CK_AHB<br>100: CK_AHB/2<br>101: CK_AHB/4<br>110: CK_AHB/8<br>111: CK_AHB/16                                                                                                                  |

| 10:8  | APB1PS[2:0] | APB1 时钟预分频系数选择<br>由软件配置 APB1 时钟预分频系数。<br>0xx: 直接使用 CK_AHB<br>100: CK_AHB/2<br>101: CK_AHB/4<br>110: CK_AHB/8<br>111: CK_AHB/16<br>请注意: CK_APB2 输出时钟频率绝对不得超过 54MHz。                                                                              |

| 7:4   | AHBPS[3:0]  | AHB 时钟预分频系数选择<br>由软件配置 AHB 时钟的分频系数。<br>0xxx: 直接使用 CK_SYS<br>1000: CK_SYS/2<br>1001: CK_SYS/4<br>1010: CK_SYS/8<br>1011: CK_SYS/16<br>1100: CK_SYS/64<br>1101: CK_SYS/128<br>1110: CK_SYS/256<br>1111: CK_SYS/512                                |

| 3:2   | SCSS[1:0]   | 系统时钟切换状态<br>由硬件设置,表明系统时钟的当前时钟源。<br>00: CK_HSI<br>01: CK_HSE<br>10: CK_PLL<br>11: 保留                                                                                                                                                             |

| 1:0   | SCS[1:0]    | 系统时钟切换<br>由软件选择系统时钟的时钟源。由于改变 CK_SYS 是有原生延迟的,因此软件<br>必须读取 SCSS 位域来判断时钟切换过程是否已经完成。当退出停机模式或待<br>机模式时,系统自动将时钟切换至 HSI; 当选用 HSE 作为 CK_SYS 或 PLL 时<br>钟源时,若 HSE 时钟监控模块检测到时钟阻塞,系统也会自动将时钟切换至<br>HSI。<br>00: CK_HSI<br>01: CK_HSE<br>10: CK_PLL<br>11: 保留 |

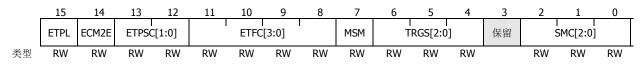

# 3.3 全局时钟中断寄存器(RCC\_GCIR)

地址偏移: 0x08

复位值 : 0x0000 0000

访问 : 无等待态,可按字(32位)、半字(16位)、字节(8位)访问

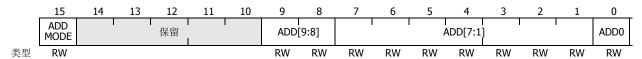

|    | 31 | 30 | 29 | 28           | 27           | 26           | 25           | 24           | 23   | 22 | 21 | 20          | 19          | 18          | 17          | 16          |

|----|----|----|----|--------------|--------------|--------------|--------------|--------------|------|----|----|-------------|-------------|-------------|-------------|-------------|

|    |    |    |    | 保            | 留            |              |              |              | СКМС | 保旨 | 留  | PLL<br>STBR | HSE<br>STBR | HSI<br>STBR | LSE<br>STBR | LSI<br>STBR |

| 类型 |    |    |    |              |              |              |              |              | W    |    |    | W           | W           | W           | W           | W           |

|    |    |    |    |              |              |              |              |              |      |    |    |             |             |             |             |             |

|    | 15 | 14 | 13 | 12           | 11           | 10           | 9            | 8            | 7    | 6  | 5  | 4           | 3           | 2           | 1           | 0           |

|    |    | 保留 |    | PLL<br>STBIE | HSE<br>STBIE | HSI<br>STBIE | LSE<br>STBIE | LSI<br>STBIE | CKMF | 保旨 | 初日 | PLL<br>STBF | HSE<br>STBF | HSI<br>STBF | LSE<br>STBF | LSI<br>STBF |

| 类型 |    |    |    | RW           | RW           | RW           | RW           | RW           | R    |    |    | R           | R           | R           | R           | R           |

| 位/位域  | 名称       | 描述                                                                           |

|-------|----------|------------------------------------------------------------------------------|

| 31:24 | 保留       | 请保持其复位状态                                                                     |

| 23    | CKMR     | HSE 时钟阻塞中断复位<br>软件对本位写 1,即可清零 CKMF 标志。<br>0:无意义<br>1:清零 CKMF 标志              |

| 22:21 | 保留       | 请保持其复位状态                                                                     |

| 20    | PLLSTBR  | PLL 稳定中断复位<br>软件对本位写 1,即可清零 PLLSTBF 标志。<br>0: 无意义<br>1: 清零 PLLSTBF 标志        |

| 19    | HSESTBR  | HSE 稳定中断复位<br>软件对本位写 1,即可清零 HSESTBF 标志。<br>0: 无意义<br>1: 清零 HSESTBF 标志        |

| 18    | HSISTBR  | HSI 稳定中断复位<br>软件对本位写 1,即可清零 HSISTBF 标志。<br>0: 无意义<br>1: 清零 HSISTBF 标志        |

| 17    | LSESTBR  | LSE 稳定中断复位<br>软件对本位写 1,即可清零 LSESTBF 标志。<br>0: 无意义<br>1: 清零 LSESTBF 标志        |

| 16    | LSISTBR  | LSI 稳定中断复位<br>软件对本位写 1,即可清零 LSISTBF 标志。<br>0: 无意义<br>1: 清零 LSISTBF 标志        |

| 15:13 | 保留       | 请保持其复位状态                                                                     |

| 12    | PLLSTBIE | PLL 稳定中断使能<br>由软件置位或清零,即可使能/禁用 PLL 稳定中断。<br>0: 禁用 PLL 稳定中断<br>1: 使能 PLL 稳定中断 |

| 11    | HSESTBIE | HSE 稳定中断使能<br>由软件置位或清零,即可使能/禁用 HSE 稳定中断。<br>0: 禁用 HSE 稳定中断<br>1: 使能 HSE 稳定中断 |

| 位/位域 | 名称       | 描述                                                                                                                             |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 10   | HSISTBIE | HSI 稳定中断使能<br>由软件置位或清零,即可使能/禁用 HSI 稳定中断。<br>0: 禁用 HSI 稳定中断<br>1: 使能 HSI 稳定中断                                                   |

| 9    | LSESTBIE | LSE 稳定中断使能<br>由软件置位或清零,即可使能/禁用 LSE 稳定中断。<br>0: 禁用 LSE 稳定中断<br>1: 使能 LSE 稳定中断                                                   |

| 8    | LSISTBIE | LSI 稳定中断使能<br>由软件置位或清零,即可使能/禁用 LSI 稳定中断。<br>0: 禁用 LSI 稳定中断<br>1: 使能 LSI 稳定中断                                                   |

| 7    | CKMF     | HSE 时钟阻塞中断标志<br>当 HSE 时钟发生阻塞时,硬件将本位置位。当软件对 CKMR 写 1 时,本位即<br>清零。<br>0: HSE 时钟工作正常<br>1: HSE 时钟阻塞                               |

| 6:5  | 保留       | 请保持其复位状态                                                                                                                       |

| 4    | PLLSTBF  | PLL 稳定中断标志<br>当 PLL 时钟稳定、并且 PLLSTBIE=1 时,硬件将本位置位。当软件对 PLLSTBR<br>写 1 时,本位即清零。<br>0: 未产生 PLL 稳定中断<br>1: 已产生 PLL 稳定中断            |

| 3    | HSESTBF  | HSE 稳定中断标志<br>当外部 4~16MHz 晶体振荡时钟稳定、并且 HSESTBIE=1 时,硬件将本位置<br>位。当软件对 HSESTBR 写 1 时,本位即清零。<br>0: 未产生 HSE 稳定中断<br>1: 已产生 HSE 稳定中断 |

| 2    | HSISTBF  | HSI 稳定中断标志<br>当内部 8MHz RC 振荡时钟稳定、并且 HSISTBIE=1 时,硬件将本位置位。当<br>软件对 HSISTBR 写 1 时,本位即清零。<br>0:未产生 HSI 稳定中断<br>1:已产生 HSI 稳定中断     |

| 1    | LSESTBF  | LSE 稳定中断标志<br>当外部 32768Hz 时钟稳定、并且 LSESTBIE=1 时,硬件将本位置位。当软件<br>对 LSESTBR 写 1 时,本位即清零。<br>0:未产生 LSE 稳定中断<br>1: 已产生 LSE 稳定中断      |

| 0    | LSISTBF  | LSI 稳定中断标志<br>当内部 32kHz 时钟稳定、并且 LSISTBIE=1 时,硬件将本位置位。当软件对<br>LSISTBR 写 1 时,本位即清零。<br>0:未产生 LSI 稳定中断<br>1:已产生 LSI 稳定中断          |

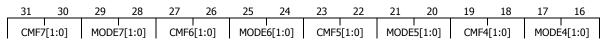

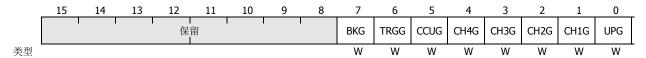

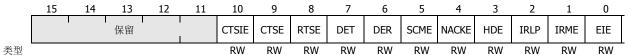

# 3.4 APB2 复位控制寄存器(RCC\_APB2RCR)

地址偏移: 0x0C

复位值 : 0x0000 0000

类型

|         | 15 | 14            | 13 | 12          | 11         | 10          | 9           | 8  | 7 | 6     | 5     | 4     | 3     | 2     | 1  | 0     |

|---------|----|---------------|----|-------------|------------|-------------|-------------|----|---|-------|-------|-------|-------|-------|----|-------|

|         | 保留 | USART1<br>RST | 保留 | SPI1<br>RST | TM1<br>RST | ADC2<br>RST | ADC1<br>RST | 保旨 | 智 | PERST | PDRST | PCRST | PBRST | PARST | 保留 | AFRST |

| <b></b> |    | RW            |    | RW          | RW         | RW          | RW          |    |   | RW    | RW    | RW    | RW    | RW    |    | RW    |

| 左王    | KVV KVV   | IXVV IXVV IXVV                                         | IXVV | IXVV | IXVV | IXVV | IXVV | IXVV |

|-------|-----------|--------------------------------------------------------|------|------|------|------|------|------|

| 位/位域  | 名称        | 描述                                                     |      |      |      |      |      |      |

| 31:15 | 保留        | 请保持其复位状态                                               |      |      |      |      |      |      |

| 14    | USART1RST | USART1 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 USART1         |      |      |      |      |      |      |

| 13    | 保留        | 请保持其复位状态                                               |      |      |      |      |      |      |

| 12    | SPI1RST   | SPI1 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 SPI1             |      |      |      |      |      |      |

| 11    | TM1RST    | 定时器 1 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位定时器 1            |      |      |      |      |      |      |

| 10    | ADC2RST   | ADC2 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 ADC2             |      |      |      |      |      |      |

| 9     | ADC1RST   | ADC1 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 ADC1             |      |      |      |      |      |      |

| 8:7   | 保留        | 请保持其复位状态                                               |      |      |      |      |      |      |

| 6     | PERST     | GPIO 端口 E 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 GPIO 端口 E   |      |      |      |      |      |      |

| 5     | PDRST     | GPIO 端口 D 复位<br>由软件置位或清零。<br>0:未复位<br>1:复位 GPIO 端口 D   |      |      |      |      |      |      |

| 4     | PCRST     | GPIO 端口 C 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 GPIO 端口 C |      |      |      |      |      |      |

| 位/位域 | 名称    | 描述                                                     |

|------|-------|--------------------------------------------------------|

| 3    | PBRST | GPIO 端口 B 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 GPIO 端口 B |

| 2    | PARST | GPIO 端口 A 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 GPIO 端口 A |

| 1    | 保留    | 请保持其复位状态                                               |

| 0    | AFRST | 备选功能 I/O 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位备选功能 I/O    |

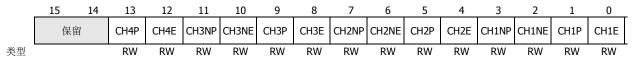

### 3.5 APB1 复位控制寄存器 (RCC\_APB1RCR)

地址偏移: 0x10

类型

复位值 : 0x0000 0000

SPI2 WWD TM4 TM3 TM2 保留 保留 保留 RST **GRST RST** RST RST RW RW RW RW RW

| 位/位域  | 名称     | 描述                                           |

|-------|--------|----------------------------------------------|

| 31:29 | 保留     | 请保持其复位状态                                     |

| 28    | PWRRST | 电源控制复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位电源控制单元 |

| 27    | BKPRST | 备电域接口复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位备电域接口 |

| 26    | 保留     | 请保持其复位状态                                     |

| 25    | CANRST | CAN 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 CAN   |

| 24    | 保留     | 请保持其复位状态                                     |

| 位/位域  | 名称        | 描述                                                                     |

|-------|-----------|------------------------------------------------------------------------|

| 23    | USBRST    | USB 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 USB                             |

| 22    | I2C2RST   | I <sup>2</sup> C2 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 I <sup>2</sup> C2 |

| 21    | I2C1RST   | I <sup>2</sup> C1 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 I <sup>2</sup> C1 |

| 20:19 | 保留        | 请保持其复位状态                                                               |

| 18    | USART3RST | USART3 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 USART3                       |

| 17    | USART2RST | USART2 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 USART2                       |

| 16:15 | 保留        | 请保持其复位状态                                                               |

| 14    | SPI2RST   | SPI2 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位 SPI2                           |

| 13:12 | 保留        | 请保持其复位状态                                                               |

| 11    | WWDGRST   | 窗口式看门狗复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位窗口式看门狗                         |

| 10:3  | 保留        | 请保持其复位状态                                                               |

| 2     | TM4RST    | 定时器 4 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位定时器 4                          |

| 1     | TM3RST    | 定时器 3 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位定时器 3                          |

| 0     | TM2RST    | 定时器 2 复位<br>由软件置位或清零。<br>0: 未复位<br>1: 复位定时器 2                          |

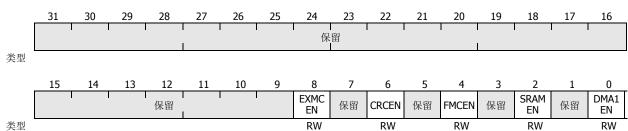

### 3.6 AHB 时钟控制寄存器(RCC\_AHBCCR)

地址偏移: 0x14

复位值 : 0x0000 0014

| 位/位域 | 名称     | 描述                                                                                         |

|------|--------|--------------------------------------------------------------------------------------------|

| 31:9 | 保留     | 请保持其复位状态                                                                                   |

| 8    | EXMCEN | EXMC 时钟使能<br>由软件置位或清零。<br>0: 禁用 EXMC 时钟<br>1: 使能 EXMC 时钟                                   |

| 7    | 保留     | 请保持其复位状态                                                                                   |

| 6    | CRCEN  | CRC 时钟使能<br>由软件置位或清零。<br>0: 禁用 CRC 时钟<br>1: 使能 CRC 时钟                                      |

| 5    | 保留     | 请保持其复位状态                                                                                   |

| 4    | FMCEN  | FLITF 时钟使能<br>由软件置位或清零,使能/禁用睡眠模式下的 FLITF 时钟。<br>0:睡眠模式下,禁用 FLITF 时钟<br>1:睡眠模式下,使能 FLITF 时钟 |

| 3    | 保留     | 请保持其复位状态                                                                                   |

| 2    | SRAMEN | SRAM 接口时钟使能<br>由软件置位或清零,使能/禁用睡眠模式下的 SRAM 接口时钟。<br>0:睡眠模式下,禁用 SRAM 时钟<br>1:睡眠模式下,使能 SRAM 时钟 |

| 1    | 保留     | 请保持其复位状态                                                                                   |

| 0    | DMA1EN | DMA1 时钟使能<br>由软件置位或清零。<br>0: 禁用 DMA1 时钟<br>1: 使能 DMA1 时钟                                   |

### 3.7 APB2 时钟控制寄存器 (RCC\_APB2CCR)

地址偏移: 0x18

复位值 : 0x0000 0000

类型

|    | 15 | 14            | 13 | 12         | 11    | 10         | 9          | 8  | 7 | 6    | 5    | 4    | 3    | 2    | 1  | 0    |   |

|----|----|---------------|----|------------|-------|------------|------------|----|---|------|------|------|------|------|----|------|---|

|    | 保留 | USART<br>1 EN | 保留 | SPI1<br>EN | TM1EN | ADC2<br>EN | ADC1<br>EN | 保旨 | 留 | PEEN | PDEN | PCEN | PBEN | PAEN | 保留 | AFEN | ĺ |

| 米刑 |    | R/W           |    | RW         | RW    | RW         | RW         |    |   | RW   | RW   | RW   | RW   | RW   |    | RW   | - |

| 大王 | IXVV | IXVV     | IXVV IXVV IXVV                                              | •                       | IXVV | IXVV | IXVV | IXVV | IXVV | IXVV |

|----|------|----------|-------------------------------------------------------------|-------------------------|------|------|------|------|------|------|

| 位/ | 位域   | 名称       | 描述                                                          |                         |      |      |      |      |      |      |

| 31 | :15  | 保留       | 请保持其复位                                                      | :状态                     |      |      |      |      |      |      |

| 1  | 4    | USART1EN | USART1 时钟<br>由软件置位或<br>0:禁用 USAF<br>1:使能 USAF               | 清零。<br><b>RT1</b> 时钟    |      |      |      |      |      |      |

| 1  | 3    | 保留       | 请保持其复位                                                      | 状态                      |      |      |      |      |      |      |

| 1  | 2    | SPI1EN   | SPI1 时钟使自由软件置位或<br>0:禁用 SPI1<br>1:使能 SPI1                   | 清零。<br>时钟               |      |      |      |      |      |      |

| 1  | 1    | TM1EN    | 定时器 1 时钟<br>由软件置位或<br>0:禁用定时器<br>1:使能定时器                    | 清零。<br>器 1 时钟           |      |      |      |      |      |      |

| 1  | 0    | ADC2EN   | ADC2 接口时 <sup>4</sup><br>由软件置位或<br>0: 禁用 ADC2<br>1: 使能 ADC2 | 清零。<br>2 接口时钟           |      |      |      |      |      |      |

| 9  | 9    | ADC1EN   | ADC1 接口时 <sup>4</sup><br>由软件置位或<br>0:禁用 ADC1<br>1:使能 ADC1   | 清零。<br>L 接口时钟           |      |      |      |      |      |      |

| 8  | :7   | 保留       | 请保持其复位                                                      | 状态                      |      |      |      |      |      |      |

| (  | 5    | PEEN     | GPIO 端口 E E<br>由软件置位或<br>0:禁用 GPIO<br>1:使能 GPIO             | 清零。<br>) 端口 E 时钟        |      |      |      |      |      |      |

| !  | 5    | PDEN     | GPIO 端口 D<br>由软件置位或<br>0:禁用 GPIO<br>1:使能 GPIO               | 清零。<br>) 端口 <b>D</b> 时钟 |      |      |      |      |      |      |

| •  | 4    | PCEN     | GPIO 端口 CI<br>由软件置位或<br>0:禁用 GPIO<br>1:使能 GPIO              | 清零。<br>  端口 C 时钟        |      |      |      |      |      |      |

| 位/位域 | 名称   | 描述                                                                      |

|------|------|-------------------------------------------------------------------------|

| 3    | PBEN | GPIO 端口 B 时钟使能<br>由软件置位或清零。<br>0: 禁用 GPIO 端口 B 时钟<br>1: 使能 GPIO 端口 B 时钟 |

| 2    | PAEN | GPIO 端口 A 时钟使能<br>由软件置位或清零。<br>0: 禁用 GPIO 端口 A 时钟<br>1: 使能 GPIO 端口 A 时钟 |

| 1    | 保留   | 请保持其复位状态                                                                |

| 0    | AFEN | 备选功能 I/O 时钟使能由软件置位或清零。 0: 禁用备选功能 I/O 时钟 1: 使能备选功能 I/O 时钟                |

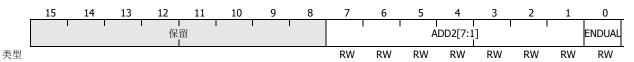

### 3.8 APB1 时钟控制寄存器(RCC\_APB1CCR)

地址偏移: 0x1C

复位值 : 0x0000 0000

保留

SPI2 EN

保留

WWD GEN

RW

TM4EN TM3EN TM2EN

类型

RW

RW

RW

RW

RW

| 位/位域  | 名称    | 描述                                                                   |

|-------|-------|----------------------------------------------------------------------|

| 31:29 | 保留    | 请保持其复位状态                                                             |

| 28    | PWREN | 电源接口时钟使能<br>由软件置位或清零。<br>0:禁用电源接口时钟<br>1:使能电源接口时钟                    |

| 27    | BKPEN | 备用域接口时钟使能由软件置位或清零。<br>0:禁用备用域接口时钟<br>1:使能备用域接口时钟                     |

| 26    | 保留    | 请保持其复位状态                                                             |

| 25    | CANEN | CAN 时钟使能         由软件置位或清零。         0: 禁用 CAN 时钟         1: 使能 CAN 时钟 |

| 24    | 保留    | 请保持其复位状态                                                             |

| 位/位域  | 名称       | 描述                                                                                              |

|-------|----------|-------------------------------------------------------------------------------------------------|

| 23    | USBEN    | USB 时钟使能<br>由软件置位或清零。<br>0: 禁用 USB 时钟<br>1: 使能 USB 时钟                                           |

| 22    | I2C2EN   | I <sup>2</sup> C2 时钟使能<br>由软件置位或清零。<br>0: 禁用 I <sup>2</sup> C2 时钟<br>1: 使能 I <sup>2</sup> C2 时钟 |

| 21    | I2C1EN   | I <sup>2</sup> C1 时钟使能<br>由软件置位或清零。<br>0: 禁用 I <sup>2</sup> C1 时钟<br>1: 使能 I <sup>2</sup> C1 时钟 |

| 20:19 | 保留       | 请保持其复位状态                                                                                        |

| 18    | USART3EN | USART3 时钟使能<br>由软件置位或清零。<br>0:禁用 USART3 时钟<br>1:使能 USART3 时钟                                    |

| 17    | USART2EN | USART2 时钟使能<br>由软件置位或清零。<br>0: 禁用 USART2 时钟<br>1: 使能 USART2 时钟                                  |

| 16:15 | 保留       | 请保持其复位状态                                                                                        |

| 14    | SPI2EN   | SPI2 时钟使能<br>由软件置位或清零。<br>0: 禁用 SPI2 时钟<br>1: 使能 SPI2 时钟                                        |

| 13:12 | 保留       | 请保持其复位状态                                                                                        |

| 11    | WWDGEN   | 窗口式看门狗时钟使能<br>由软件置位或清零。<br>0:禁用窗口式看门狗时钟<br>1:使能窗口式看门狗时钟                                         |

| 10:3  | 保留       | 请保持其复位状态                                                                                        |

| 2     | TM4EN    | 定时器 4 时钟使能<br>由软件置位或清零。<br>0: 禁用定时器 4 时钟<br>1: 使能定时器 4 时钟                                       |

| 1     | TM3EN    | 定时器 3 时钟使能<br>由软件置位或清零。<br>0:禁用定时器 3 时钟<br>1:使能定时器 3 时钟                                         |

| 0     | TM2EN    | 定时器 2 时钟使能<br>由软件置位或清零。<br>0: 禁用定时器 2 时钟<br>1: 使能定时器 2 时钟                                       |

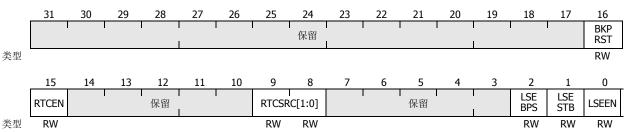

### 3.9 备电域控制寄存器(RCC\_BDCR)

地址偏移: 0x20

复位值 : 0x0000 0000 (由备电域复位命令复位)

**请注意**: 备电域控制寄存器(RCC\_BDCR)的 LSEEN、LSEBPS、RTCSRC、RTCEN 位仅在执行备 电域复位命令之后才会清零。只有当电源控制寄存器(PWR\_CR)的 DBP 置位的情况下,这些位 才可以修改。

|       |             |                                                                                         | <br> |  |

|-------|-------------|-----------------------------------------------------------------------------------------|------|--|

| 位/位域  | 名称          | 描述                                                                                      |      |  |

| 31:17 | 保留          | 请保持其复位状态                                                                                |      |  |

| 16    | BKPRST      | 备电域复位<br>由软件置位或清零。<br>0: 无意义<br>1: 复位备电域                                                |      |  |

| 15    | RTCEN       | RTC 时钟使能<br>由软件置位或清零。<br>0: 禁用 RTC 时钟<br>1: 使能 RTC 时钟                                   |      |  |

| 14:10 | 保留          | 请保持其复位状态                                                                                |      |  |

| 9:8   | RTCSRC[1:0] | RTC 时钟源选择<br>由软件配置 RTC 的时钟源。<br>00: 无时钟输入<br>01: CK_LSE<br>10: CK_LSI<br>11: CK_HSE/128 |      |  |

| 7:3   | 保留          | 请保持其复位状态                                                                                |      |  |

| 2     | LSEBPS      | LSE 旁通模式使能<br>由软件置位或清零。<br>0: 禁用 LSE 旁通模式<br>1: 使能 LSE 旁通模式                             |      |  |

| 1     | LSESTB      | 外部低速晶体振荡电路稳定<br>由硬件置位,表明 LSE 振荡电路已工作稳定,可供使用。<br>0: LSE 振荡电路未稳定<br>1: LSE 振荡电路已稳定        |      |  |

| 0     | LSEEN       | LSE 使能<br>由软件置位或清零。<br>0: 禁用 LSE<br>1: 使能 LSE                                           |      |  |

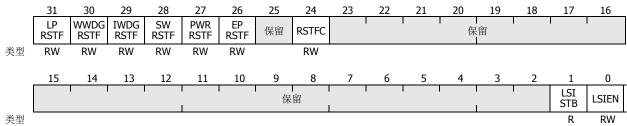

#### 全局控制/状态寄存器(RCC\_GCSR) 3.10

地址偏移: 0x24

复位值 : 0x0C00 0000 (其中复位类标志由电源复位清零,其它标志由系统复位清零)

| 位/位域 | 名称       | 描述                                                                                                          |

|------|----------|-------------------------------------------------------------------------------------------------------------|

| 31   | LPRSTF   | 低功耗复位标志<br>当停机模式/待机模式下产生复位时,由硬件置位。当软件向 RSTFC 写 1 时,本标志位清零。<br>0: 低功耗模式下未产生复位<br>1: 低功耗模式下产生了复位              |

| 30   | WWDGRSTF | 窗口式看门狗定时器复位标志<br>当窗口式看门狗定时器产生复位时,由硬件置位。当软件向 RSTFC 写 1 时,本标志位清零。<br>0:未产生窗口式看门狗定时器复位<br>1:已产生窗口式看门狗定时器复位     |

| 29   | IWDGRSTF | 独立式看门狗定时器复位标志<br>当独立式看门狗定时器产生复位时,由硬件置位。当软件向 RSTFC 写 1 时,<br>本标志位清零。<br>0:未产生独立式看门狗定时器复位<br>1:已产生独立式看门狗定时器复位 |

| 28   | SWRSTF   | 软件复位标志<br>当产生软件复位时,由硬件置位。当软件向 RSTFC 写 1 时,本标志位清零。<br>0:未产生软件复位<br>1:已产生软件复位                                 |

| 27   | PWRGRSTF | 电源复位标志<br>当产生电源复位时,由硬件置位。当软件向 RSTFC 写 1 时,本标志位清零。<br>0:未产生电源复位<br>1:已产生电源复位                                 |

| 26   | EPRSTF   | 外部管脚复位标志<br>当外部管脚产生复位时,由硬件置位。当软件向 RSTFC 写 1 时,本标志位清<br>零。<br>0:未产生外部管脚复位<br>1:已产生外部管脚复位                     |

| 25   | 保留       | 请保持其复位状态                                                                                                    |

| 位/位域 | 名称     | 描述                                                                                 |

|------|--------|------------------------------------------------------------------------------------|

| 24   | RSTFC  | 复位标志清除<br>软件对本位写 1,即可清零所有复位标志。<br>0:无意义<br>1:清零所有复位标志                              |

| 23:2 | 保留     | 请保持其复位状态                                                                           |

| 1    | LSISTB | 内部低速 RC 振荡电路稳定<br>由硬件置位,表明 LSI 振荡电路已工作稳定,可供使用。<br>0: LSI 振荡电路未稳定<br>1: LSI 振荡电路已稳定 |

| 0    | LSIEN  | LSI 使能<br>由软件置位或清零。<br>0: 禁用 LSI<br>1: 使能 LSI                                      |

# 第4章 通用 I/O(GPIO)及备选功能 I/O(AFIO)

### 1 GPIO

#### 1.1 简介

通用 I/O 接口包含 5 个通用的输入输出端口。每个端口包含 16 个独立的通用管脚,具备输入功能以及输出功能,因此,通用 I/O 接口最多可支持 80(16×5)根管脚。每个 GPIO 端口都有相关的控制寄存器和配置寄存器,以满足不同应用的要求。至于 GPIO 管脚的外部中断,在外部中断控制单元(External Interrupt Control Unit,简写为 EXTI)中有相关的控制寄存器和配置寄存器。

GPIO 端口与其它的备选功能(Alternative Function,简写为 AF)是管脚复用的,这样可以保证 封装管脚运用的最大灵活性。通过配置相应的寄存器,可将 GPIO 管脚用作备选功能,无需考虑 备选功能是输入还是输出。

每个 GPIO 管脚可通过软件配置为输出(推挽输出或开漏输出)功能、输入(有无上/下拉)功能或者外设的备选功能。大部分 GPIO 管脚是与数字备选功能或模拟备选功能复用的。除模拟输入脚外,其余的 GPIO 都具备大电流驱动能力。

#### 1.2 主要特点

- 输入/输出方向控制

- 输入管脚可配置弱上拉/下拉

- 输出管脚可配置为推挽或开漏

- 输出管脚的置位/复位控制

- 可用作外部中断,触发沿可设置(需结合 EXTI 配置寄存器)

- 可配置为模拟输入/输出

- 可配置为备选功能输入/输出

- 端口配置锁定

#### 1.3 功能描述

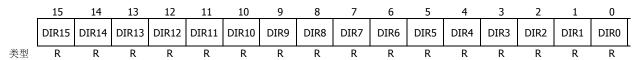

每个 GPIO 管脚都可由软件单独配置为输入或输出,并能在多种工作模式中进行选择。配置是通过两个 32 位配置寄存器(GPIOx\_CR1、GPIOx\_CR2)以及两个 32 位数据寄存器(GPIOx\_DIR、GPIOx\_DOR)。详见下表:

表 5 GPIO 端口配置位

| 配        | 置模式   | CMF1 | CMF0 | MODE1          | MODE0  | PxODR<br>寄存器 |

|----------|-------|------|------|----------------|--------|--------------|

|          | 模拟输入  | 0    | 0    |                | 无关     |              |

| <br>  输入 | 浮空输入  | U    | 1    | 0              | 无关     |              |

| <b> </b> | 弱下拉输入 | 1    | 0    | U              | 0      |              |

|          | 弱上拉输入 | 1    |      |                | 1      |              |

| 通用输出     | 推挽输出  | 0    | 0    | 00: 保留         | 0或1    |              |

| 週份制品     | 开漏输出  | U    | 1    | 01: 速度最高 10MHz |        | 0或1          |

| 备选功能     | 推挽输出  | 1    | 0    | 10: 速度最        | 高 2MHz | 无关           |

| 输出       | 开漏输出  | 1    | 1    | 11: 速度最        | 无关     |              |

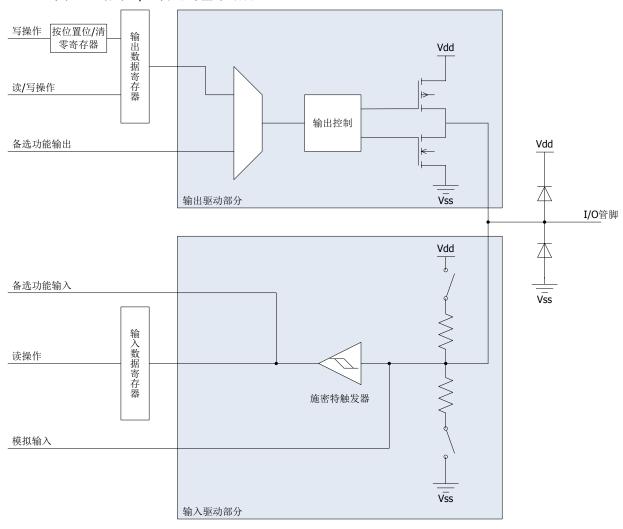

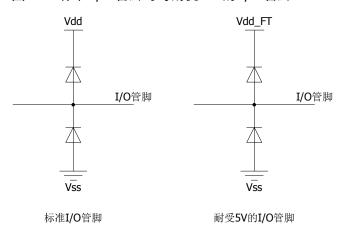

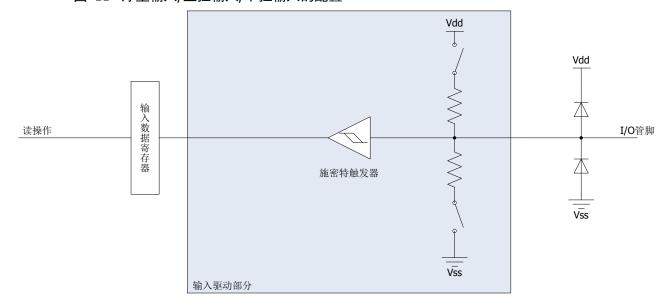

下图是 I/O 管脚的基本结构。

图 9 标准 I/O 管脚的基本结构

#### 图 10 标准 I/O 管脚与可耐受 5V 的 I/O 管脚

#### GPIO 管脚的默认配置

在复位期间和复位之后,备选功能并未激活,I/O 口皆配置为浮空输入模式。不过,与调试功能复用的管脚(PA15、PA14、PA13、PB4)在复位后是激活的:

PA15: JTDI 功能, 带上拉

PA14: JTCK 功能, 带下拉

PA13: JTMS 功能,带上拉

PB4: NJTRST 功能,带上拉

GPIO 管脚可以配置为输入管脚或输出管脚。当 GPIO 管脚配置为输入管脚时,外部管脚上的数据(电平)每个 APB2 时钟周期都会装载到数据输入寄存器(GPIO\_DIR)。所有 GPIO 管脚都具有内部弱上拉和弱下拉的选项。

当 GPIO 管脚配置为输出管脚时,用户可以配置该管脚的最大翻转速度,并且选择输出驱动的模式:推挽模式或开漏模式。数据输出寄存器(GPIO\_DOR)的值将会输出到 I/O 管脚上。

所有管脚均具有外部中断能力。要使用外部中断,则管脚必须配置为输入模式。当需要对 GPIO\_DOR 寄存器进行按位写操作时,不需要禁用中断,用户可以对位操作寄存器(GPIO\_BOR,或专用于清零的 GPIO\_BCR)的单个/多个位写'1',即可修改单个/多个管脚的输出,并且此过程仅需单个原子级的 APB2 写操作。此时其它位将不受影响。

#### 输入配置

当 GPIO 管脚配置为输入管脚时:

- 输入施密特触发器将被激活

- 可选择弱上拉以及弱下拉

- I/O 管脚上的数据(电平)每个 APB2 时钟周期都被采样并送入数据输入寄存器

- 输出缓冲被禁用

下图是 I/O 管脚配置为输入时的状态:

#### 图 11 浮空输入/上拉输入/下拉输入的配置

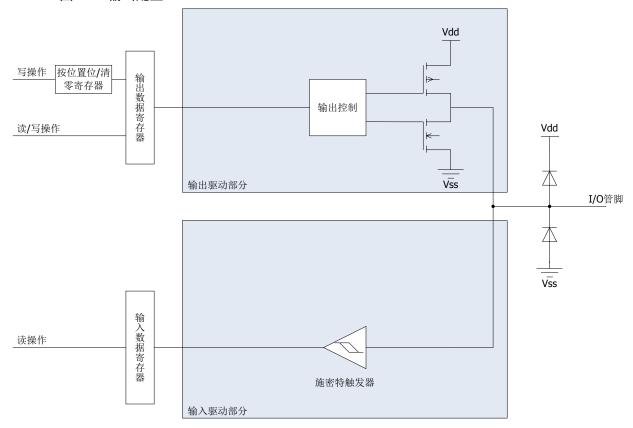

#### 输出配置

当 GPIO 管脚配置为输出管脚时:

- 输入施密特触发器将被激活

- 弱上拉以及弱下拉电阻被禁用

- 输出缓冲器被使能:

- 开漏模式:输出寄存器的"0"将使 NMOS 管导通,输出寄存器的"1"将使得管脚处于高阻状态。

- 推挽模式:输出寄存器的"0"将时 NMOS 管导通,输出寄存器的"1"将使 PMOS 管导通。

- 在推挽模式下,对数据输出寄存器的读操作,将返回其上次写入的值

- 在开漏模式下,对数据输入寄存器的读操作,将返回其 I/O 状态

下图为 I/O 管脚配置为输出时的状态:

#### 图 12 输出配置

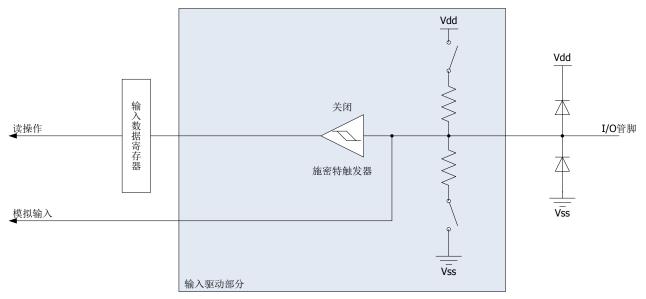

#### 模拟输入配置

当 GPIO 管脚配置为模拟输入管脚时:

- 弱上拉以及弱下拉电阻被禁用

- 输出缓冲器被禁用

- 输入的施密特触发器被禁用

- 对数据输入寄存器的读操作,始终返回"0"

下图为 I/O 管脚配置为高阻模拟输入时的状态:

#### 图 13 高阻模拟输入配置

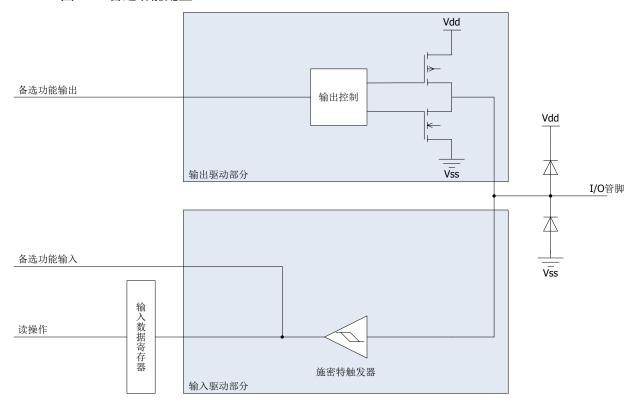

#### 备选功能 (AF) 配置

为了适合多种不同的器件封装,GPIO 支持由软件将一些备选功能映射到部分其它管脚上。对于 双向的备选功能,相应的端口必须配置为备选功能输出模式。在这种情况下,输入驱动部分将配 置为浮空输入模式。

当 GPIO 管脚配置为备选功能时:

- 输出缓冲器将开启为开漏或推挽模式

- 输出缓冲器由外设模块驱动

- 输入施密特触发器启用

- 弱上拉以及弱下拉电阻被禁用

- 每个 APB2 时钟周期采样 I/O 管脚上的数据(电平)并送入数据输入寄存器

- 在开漏模式下,对数据输入寄存器进行读操作,将返回 I/O 状态

- 在推挽模式下,对数据输出寄存器进行读操作,将返回上一次写入的值

下图是 I/O 管脚配置为备选功能时的状态:

图 14 备选功能配置

#### 针对器件外设的 GPIO 配置

以下诸表给出了针对器件各种外设的 GPIO 配置。

表 6 高级定时器 TM1

| TIM1/TIM8<br>管脚配置 | 功能配置        | GPIO 配置   |

|-------------------|-------------|-----------|

| TM1 CU[4.1]       | 输入捕获通道[4:1] | 浮空输入      |

| TM1_CH[4:1]       | 输出捕获通道[4:1] | 备选功能,推挽模式 |

| TM1_CH[3:1]N      | 互补输出通道[3:1] | 备选功能,推挽模式 |

| TM1_BKIN          | 紧急制动输入      | 浮空输入      |

| TM1_ETR           | 外部触发定时器输入   | 浮空输入      |

#### 表 7 通用定时器 TM2/3/4

| TM2/3/4<br>管脚配置 | 功能配置        | GPIO 配置   |

|-----------------|-------------|-----------|