# IT6604

Single-Link HDMI 1.4 Receiver with 3D Support

ITE TECH. INC.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 1/36

# **General Description**

The IT6604 is a single-link HDMI receiver, fully compatible with HDMI 1.3, compatible with HDMI 1.4a 3D and HDCP 1.4 compliance specification and also backward compatible to DVI 1.0 specifications. The IT6604 with its Deep Color capability (up to 36-bit) ensures robust reception of high-quality uncompressed video content, along with state-of-the-art uncompressed and compressed digital audio content such as DTS-HD and Dolby TrueHD in digital televisions and projectors. The IT6604 also supports all the primary 3D formats which are compliant with the HDMI 1.4a 3D specification.

Aside from the various video output formats supported, the IT6604 also receives and provides up to 8 channels of I<sup>2</sup>S digital audio outputs, with sampling rate up to 192kHz and sample size up to 24 bits, facilitating direct connection to industry-standard low-cost audio DACs. Also, an S/PDIF output is provided to support up to compressed audio of 192kHz frame rate. Super Audio Compact Disc (SACD) is supported at up to 8 channels and 88.2kHz through DSD (Direct Stream Digital ports) ports.

The High-Bit Rate (HBR) audio is also provided by the IT6604 in two interfaces: with the four I<sup>2</sup>S input ports or the S/PDIF input port. With both interfaces the highest possible HBR frame rate is supported at up to 768kHz.

Each IT6604 comes preprogrammed with an unique HDCP key, in compliance with the HDCP 1.4 standard so as to provide secure transmission of high-definition content. Users of the IT6604 need not purchase any HDCP keys or ROMs.

The IT6604 is pin compatible with the IT6603, the previous generation single-link HDMI 1.3 receiver.

## **Features**

- Single-link HDMI 1.4 receiver

- Pin compatible with IT6603

- Compliant with HDMI 1.3, HDMI 1.4a 3D, HDCP 1.4 and DVI 1.0 specifications

- Supporting link speeds of up to 2.25Gbps (link clock rate of 225MHz).

- Supporting all the primary 3D formats which are compliant with the HDMI 1.4a 3D specification.

- Supporting 3D video up to 1080P@50/59.95/60Hz, 1080P@23.98/24/29.97/30Hz, 1080i@50/59.94/60/Hz, 720P@23.98/24/29.97/30Hz, 720P@50/59.94/60Hz

- Supporting formats: Framing Packing, Side-by-Side (half), Top-and-Bottom.

- Video output interface supporting digital video standards such as:

- 24/30-bit RGB/YCbCr 4:4:4

www.ite.com.tw Sep-2010 Rev:0.9 2/36

## IT6604

- 16/20-bit YCbCr 4:2:2

- ◆ 8/10-bit YCbCr 4:2:2 (ITU BT-656)

- 24/30-bit double data rate interface (full bus width, pixel clock rate halved, clocked with both rising and falling edges)

- Input channel swap

- Bi-direction Color Space Conversion (CSC) between RGB and YCbCr color spaces with programmable coefficients.

- Up/down sampling between YCbCr 4:4:4 and YCbCr 4:2:2

- Dithering for conversion from 12-bit component to 10-bit/8-bit

- Digital audio output interface supporting

- up to four I<sup>2</sup>S interface supporting 8-channel audio, with sample rates of 32~192 kHz and sample sizes of 16~24 bits

- ◆ S/PDIF interface supporting PCM, Dolby Digital, DTS digital audio at up to 192kHz frame rate

- Optional support for 8-channel DSD audio up to 8 channels at 88.2kHz sample rate

- Support for high-bit-rate (HBR) audio such as DTS-HD and Dolby TrueHD through the four I<sup>2</sup>S interface or the S/PDIF interface, with frame rates as high as 768kHz

- automatic audio error detection for programmable soft mute, preventing annoying harsh output sound due to audio error or hot-unplug

- Auto-calibrated input termination impedance provides process-, voltage- and temperature-invariant matching to the input transmission lines.

- Integrated pre-programmed HDCP keys

- Intelligent, programmable power management

- 128-pin LQFP (14mm x 14mm) package

- RoHS Compliant ( 100% Green available )

# **Ordering Information**

| Model   | Temperature Range | Package Type | Green/Pb free Option |  |  |

|---------|-------------------|--------------|----------------------|--|--|

| IT6604E | 0~70              | 128-pin LQFP | Green                |  |  |

www.ite.com.tw Sep-2010 Rev:0.9 3/36

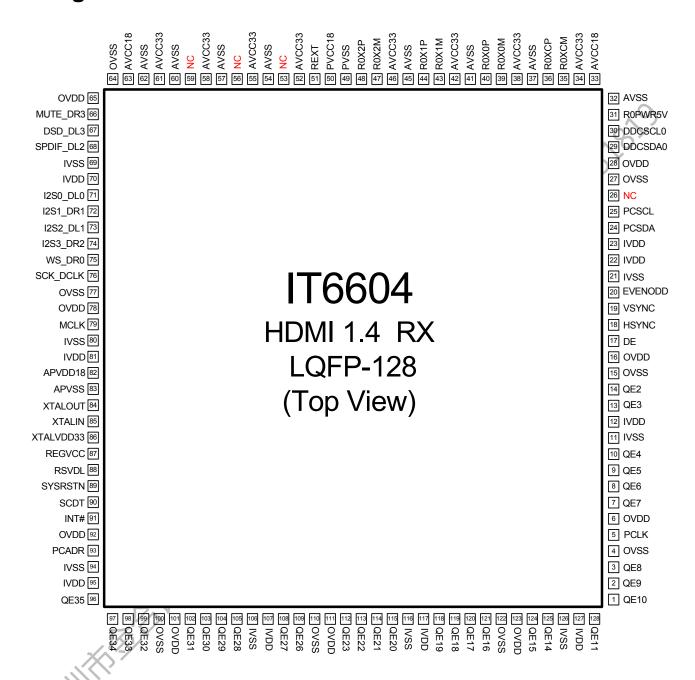

## **Pin Diagram**

Figure 1. IT6604 pin diagram

#### Note:

- 1. Pin51 must be connected with an external 500 $\Omega$  SMD resistor to ground. This resistor serves to calibrate the on-chip termination impedances of all four pairs of high-speed serial links.

- 2. Pins marked with NC should be left unconnected.

www.ite.com.tw Sep-2010 Rev:0.9 4/36

# **Pin Description**

# **Digital Video Onput Pins**

| Pin Name  | Direction | Description                                        | Туре  | Pin No.           |

|-----------|-----------|----------------------------------------------------|-------|-------------------|

| QE[35:26] | Output    | Digital Video Output Pins. Channel swap is         | LVTTL | 1-3, 7-10, 13-14, |

| QE[23:14] |           | supported through register setting.                |       | 96-99, 102-105,   |

| QE[11:2]  |           |                                                    |       | 108-109, 112-115, |

|           |           |                                                    |       | 118-121, 124-125, |

|           |           |                                                    |       | 128               |

| PCLK      | Output    | Output data clock. The backend controller should   | LVTTL | 5                 |

|           |           | use the rising edge of PCLK to strobe QE[35:2]     |       |                   |

| DE        | Output    | Data enable                                        | LVTTL | 17                |

| HSYNC     | Output    | Horizontal sync. signal                            | LVTTL | 18                |

| VSYNC     | Output    | Vertical sync. signal                              | LVTTL | 19                |

| EVENODD   | Output    | Indicates whether the current field is Even or Odd | LVTTL | 20                |

|           |           | for interlaced format                              |       |                   |

## **Digital Audio Onput Pins**

| Digital Addit | onput:    |                                                                     |       |         |

|---------------|-----------|---------------------------------------------------------------------|-------|---------|

| Pin Name      | Direction | Description                                                         | Type  | Pin No. |

| XTALIN        | Input     | Crystal clock input (for Audio PLL)                                 | LVTTL | 85      |

| XTALOUT       | Output    | Crystal clock output (for Audio PLL)                                | LVTTL | 84      |

| MCLK          | Output    | Audio master clock                                                  | LVTTL | 79      |

| SCK_DCLK      | Output    | I2S serial clock output, doubles as DSD clock                       | LVTTL | 76      |

| WS_DR0        | Output    | I2S word select output, doubles as DSD Serial Right CH0 data output | LVTTL | 75      |

| I2S0_DL0      | Output    | I2S serial data output, doubles as DSD Serial Left CH0 data output  | LVTTL | 71      |

| I2S1_DR1      | Output    | I2S serial data output, doubles as DSD Serial Right CH1 data output | LVTTL | 72      |

| I2S2_DL1      | Output    | I2S serial data output, doubles as DSD Serial Left CH2 data output  | LVTTL | 73      |

| I2S3_DR2      | Output    | I2S serial data output, doubles as DSD Serial Right CH2 data output | LVTTL | 74      |

| SPDIF_DL2     | Output    | S/PDIF audio output, doubles as DSD Serial Left CH2 data output     | LVTTL | 68      |

| MUTE_DR3      | Output    | Mute output, doubles as DSD Serial Right CH3 data output            | LVTTL | 66      |

| DSD_DL3       | Output    | DSD Serial Left CH3 data output                                     | LVTTL | 67      |

www.ite.com.tw Sep-2010 Rev:0.9 5/36

## **Programming Pins**

| Pin Name | Direction | Description                                                 | Туре    | Pin No.   |

|----------|-----------|-------------------------------------------------------------|---------|-----------|

| INT#     | Output    | Interrupt output. Default active-low (5V-tolerant)          | LVTTL   | 91        |

| SYSRSTN  | Input     | Hardware reset pin. Active LOW (5V-tolerant)                | Schmitt | 89        |

| DDCSCL0  | I/O       | DDC I2C Clock for HDMI Port 0 (5V-tolerant)                 | Schmitt | 30        |

| DDCSDA0  | I/O       | DDC I2C Data for HDMI Port 0 (5V-tolerant)                  | Schmitt | 29        |

| R0PWR5V  | Input     | TMDS transmitter detection for Port 0(5V-tolerant)          | LVTTL   | 31        |

| PCSCL    | Input     | Serial Programming Clock for chip programming (5V-tolerant) | Schmitt | 25        |

| PCSDA    | I/O       | Serial Programming Data for chip programming (5V-tolerant)  | Schmitt | 24        |

| PCADR    | Input     | Serial Programming device address select. Device address is | LVTTL   | 93        |

|          |           | 0x90 when PCADR is pulled low, 0x92 otherwise               |         |           |

| SCDT     | Output    | Indication for active HDMI signal at input port             | LVTTL   | 90        |

| RSVDL    |           | Must be left unconnected                                    |         | 88        |

| NC       |           | Must be left unconnected                                    |         | 26,53,56, |

|          |           | 450                                                         |         | 59,       |

# **HDMI** analog front-end interface pins

| Pin Name | Direction | Description                                                       | Туре   | Pin No. |

|----------|-----------|-------------------------------------------------------------------|--------|---------|

| R0X2P    | Analog    | HDMI Channel 2 positive input for HDMI Port 0                     | TMDS   | 48      |

| R0X2M    | Analog    | HDMI Channel 2 negative input for HDMI Port 0                     | TMDS   | 47      |

| R0X1P    | Analog    | HDMI Channel 1 positive input for HDMI Port 0                     | TMDS   | 44      |

| R0X1M    | Analog    | HDMI Channel 1 negative input for HDMI Port 0                     | TMDS   | 43      |

| R0X0P    | Analog    | HDMI Channel 0 positive input for HDMI Port 0                     | TMDS   | 40      |

| R0X0M    | Analog    | HDMI Channel 0 negative input for HDMI Port 0                     | TMDS   | 39      |

| R0XCP    | Analog _  | HDMI Clock Channel positive input for HDMI Port 0                 | TMDS   | 36      |

| R0XCM    | Analog    | HDMI Clock Channel negative input for HDMI Port 0                 | TMDS   | 35      |

| REXT     | Analog    | External resistor for setting termination impedance value. Should | Analog | 51      |

|          |           | be tied to GND via a 500Ω SMD resistor.                           |        |         |

www.ite.com.tw Sep-2010 Rev:0.9 6/36

#### **Power/Ground Pins**

| Pin Name  | Description                          | Туре     | Pin No.                 |

|-----------|--------------------------------------|----------|-------------------------|

| IVDD      | Digital logic power (1.8V)           | Power    | 12, 22, 23, 70, 81, 95, |

|           |                                      |          | 107, 117, 127           |

| IVSS      | Digital logic ground                 | Ground   | 11, 21, 69, 80,         |

|           |                                      |          | 94, 106, 116, 126       |

| OVDD      | I/O Pin power (3.3V)                 | Power    | 6, 16, 28, 65, 78,      |

|           |                                      |          | 92, 101, 111, 123       |

| OVSS      | I/O Pin ground                       | Ground   | 4,15, 27, 64, 77,       |

|           |                                      | _^^      | 100, 110, 122           |

| AVCC33    | HDMI analog frontend power (3.3V)    | Power    | 34, 38, 42, 46,         |

|           |                                      | <b>₩</b> | 52, 55, 58, 61          |

| AVCC18    | HDMI analog frontend power (1.8V)    | Power    | 33, 63                  |

| AVSS      | HDMI analog frontend ground          | Ground   | 32, 37, 41, 45,         |

|           |                                      |          | 54, 57, 60, 62          |

| PVCC18    | HDMI receiver PLL power (1.8V)       | Power    | 50                      |

| PVSS      | HDMI receiver PLL ground             | Ground   | 49                      |

| APVDD18   | HDMI audio PLL power (1.8V)          | Power    | 82                      |

| APVSS     | HDMI audio PLL ground                | Ground   | 83                      |

| XTALVDD33 | Power for crystal oscillator (3.3V)  | Power    | 86                      |

| REGVCC    | Regulator power (3.3V) for audio PLL | Power    | 87                      |

|           |                                      |          |                         |

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 7/36

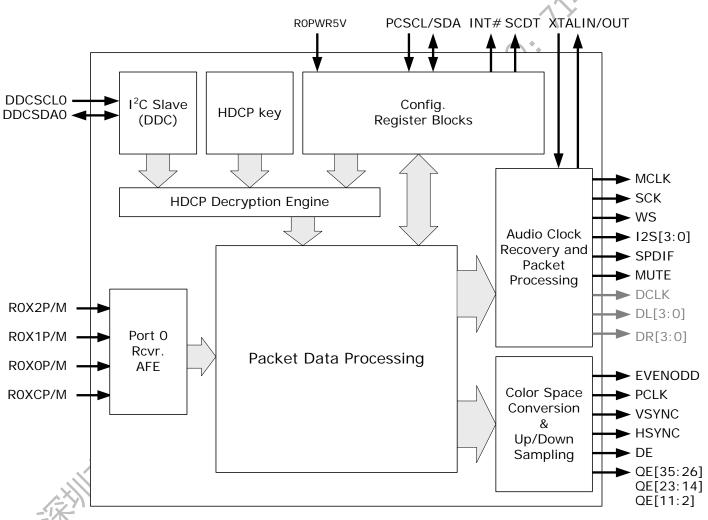

# **Functional Description**

The IT6604 is the 3nd generation HDMI receiver and provides complete solutions for HDMI v1.4 Sink systems, supporting reception and processing of Deep Color video and state-of-the-art digital audio such as DTS-HD and Dolby TrueHD. The IT6604 with its HDMI input ports supports color depths of 10 bits and 12 bits up to 1080p. Advanced processing algorithms are employed to optimize the performance of video processing such as color space conversion and up/down sampling. The following picture is the functional block digram of the IT6604, which describes clearly the data flow.

Figure 2. Functional block diagram of the IT6604

## Receiver Analog Frontend (Rcvr. AFE)

The integrated TMDS receiver analog frontend macros is capable of receiving and decoding HDMI data at up to 2.25Gbps (with a TMDS clock of 225MHz). Adaptive equalization is employed to support long cables. The system firmware has total control over this through register settings.

www.ite.com.tw Sep-2010 Rev:0.9 8/36

While not indicated in Figure 2, the HDMI PWR5V signal of the input is also monitored by the IT6604. The system controller could poll registers to confirm the existence of actually connected port.

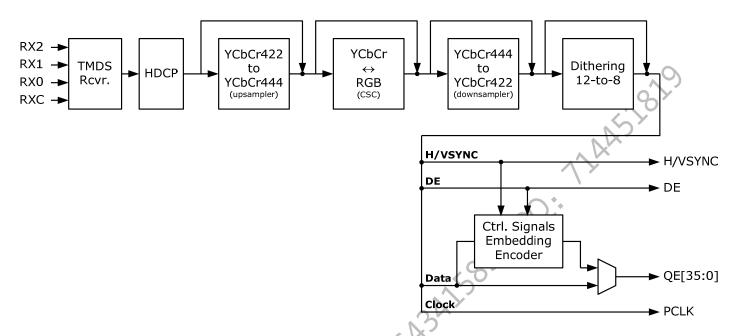

Figure 3. Video data processing flow of the IT6604

## **Video Data Processing Flow**

Figure 3 depicts the video data processing flow. For the purpose of retaining maximum flexibility, most of the block enablings and path bypassings are controlled through register programming. Please refer to IT6604 Programming Guide for detailed and precise descriptions.

As can be seen from Figure 3, the received and recovered HDMI raw data is first HDCP-decrypted. The extracted video data then go through various processing blocks, as described in the following paragraphs, before outputting the proper video format to the backend video controller.

The video processing including YCbCr up/down-sampling, color-space conversion and dithering. Depending on the selected input and output video formats, different processing blocks are either enabled or bypassed via register control. For the sake of flexibility, this is all done in software register programming. Therefore, extra care should be taken in keeping the selected output format and the corresponding video processing block selection. Please refer to the IT6604 Programming Guide for suggested register setting.

Designated as QE[35:2], the output video data could take on bus width of 8 bits to 30 bits, depending on the formats and color depths. The output interface could be configured through register setting to provide various data formats as listed in Table 1 in order to cater to different preferences of different

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 9/36

backend controllers.

Major video processings in the IT6604 are carried out in 14 bits per channel in order to minimize rounding errors and other computational residuals that occur during processing. General description of video processing blocks is as follows:

#### **HDCP engine (HDCP)**

The HDCP engine decrypts in incoming data. Preprogrammed HDCP keys are embedded in the IT6604. Users need not worry about the purchasing and management of the HDCP keys as Chip Advanced Technology will take care of them.

#### **Upsampling (YCbCr422 to YCbCr444)**

In cases where input HDMI video data are in YCbCr 4:2:2 format and output is selected as 4:4:4, this block is enabled to do the upsampling. Well-designed signal filtering is employed to avoid visible artifacts generated during upsampling.

#### **Bi-directional Color Space Conversion (YCbCr ↔ RGB)**

Many video decoders only offer YCbCr outputs, while DVI 1.0 supports only RGB color space. In order to offer full compatibility between various Source and Sink combination, this block offers bi-directional RGB ↔ YCbCr color space conversion (CSC). To provide maximum flexibility, the matrix coefficients of the CSC engine in the IT6604 are fully programmable. Users could elect to employ their preferred conversion formula.

#### Downsampling (YCbCr444 to YCbCr422)

In cases where input HDMI video data are in YCbCr 4:4:4 format and output is selected as YCbCr 4:2:2, this block is enabled to do the downsampling. Well-designed signal filtering is employed to avoid visible artifacts generated during downsampling.

#### Dithering (Dithering 12-to-10 or 12-to-8)

For outputing to the 10-bits / 8-bits-per-channel formats, decimation might be required depending on the exact input formats. This block performs the necessary dithering for decimation to prevent visible artifacts from appearing.

## Supported output Video Formats

Table 1 lists the output video formats supported by the IT6604. The listed Output Pixel Clock Frequency in MHz is the actual clock frequency at the output pin PCLK, regardless of the color depth. According to the HDMI Specification v1.3, the input TMDS clock frequency could be 1.25 times or 1.5 times that of the output PCLK frequency, depending on the color depth:

For 24-bit inputs, TMDS Clock frequency = 1 x PCLK frequency

For 30-bit inputs, TMDS Clock frequency = 1.25 x PCLK frequency

For 36-bit inputs, TMDS Clock frequency =  $1.5 \times PCLK$  frequency

The IT6604 also provides automatic video mode detection. The system controller can elect to check

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 10/36

out respective status registers to get the informations.

|       |             |       |          | (        | Output Pi | ixel Clock | Frequer | ncy (MHz | )     |       |      |  |

|-------|-------------|-------|----------|----------|-----------|------------|---------|----------|-------|-------|------|--|

| Color | Video       | Bus   | Hsync/   | 480i     | 480p      | XGA        | 720p    | 1080i    | SXGA  | 1080p | UXGA |  |

| Space | Format      | Width | Vsync    | 4001     | 460p      | AGA        | 720p    | 10001    | SAGA  | ТОООР | UNGA |  |

| RGB   | 4:4:4       | 24    | Congrete | 13.5     | 27        | 65         | 74.25   | 74.25    | 108   | 148.5 | 162  |  |

| RGB   | 4.4.4       | 30    | Separate | 13.5     | 27        | 65         | 74.25   | 74.25    | 108   | 148.5 |      |  |

|       | 4:4:4 24 30 | 24    | Congrete | 13.5     | 27        | 65         | 74.25   | 74.25    | 108   | 148.5 | 162  |  |

|       |             | 30    | Separate | 13.5     | 27        | 65         | 74.25   | 74.25    | 108   | 148.5 |      |  |

| YCbCr |             | 16/20 | Separate | 13.5     | 27        |            | 74.25   | 74.25    |       | 148.5 |      |  |

| TODO  | 4:2:2       | 10/20 | Embedded | 13.5     | 27        |            | 74.25   | 74.25    |       | 148.5 |      |  |

|       | 4.2.2       | 8/10  | Separate | 27       | 54        |            | 148.5   | 148.5    |       |       |      |  |

|       |             |       | 6/10     | Embedded | 27        | 54         |         | 148.5    | 148.5 |       |      |  |

Table 1. Output video formats supported by the IT6604

#### Notes:

- 1. Table cells that are left blanks are those format combinations that are not supported by the IT6604.

- 2. Output channel number is defined by the way the three color components (either R, G & B or Y, Cb & Cr) are arranged. Refer to Video Data Bus Mappings for better understanding.

- 3. Embedded sync signals are defined by CCIR-656 standard, using SAV/EAV sequences of FF, 00, 00, XY.

- 4. The lowest TMDS clock frequency specified by the HDMI standard is 25MHz for 640X480@60Hz.

## **Supported 3D Formats**

The IT6604 supports all the HDMI 1.4a 3D mandatory formats and all the primary 3D formats including

- 1920x1080P@50Hz -- Top-and-Bottom

- 1920x1080P@59.94/60Hz -- Top-and-Bottom

- ◆ 1920x1080P@29.97/30Hz -- Framing Packing, Top-and-Bottom

- ◆ 1920x1080P@23.98/24Hz -- Framing Packing, Side-by-Side (Half), Top-and-Bottom

- 1920x1080i@50Hz Frame Packing, Side-by-Side (Half)

- 1920x1080i@59.94/60Hz Frame Packing, Side-by-Side (Half)

- ♦ 1280x 720P@29.97/30Hz -- Framing Packing

- ◆ 1280x 720P@23.98/24Hz -- Framing Packing

- ◆ 1280x 720P@50Hz -- Framing Packing, Side-by-Side (Half), Top-and-Bottom

- ♦ 1280x 720P@59.94/60Hz -- Framing Packing, Side-by-Side (Half), Top-and-Bottom

## **Audio Clock Recovery and Data Processing**

The audio processing block in the HDMI Sink is crucial to the system performance since human hearing is susceptive to audio imperfection. The IT6604 prides itself in outstanding audio recovery performances. In addition, the audio clock recovery PLL uses an external crystal reference so as to provide stable and reliable audio clocks for all audio output formats.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 11/36

The IT6604 supports all audio formats and interfaces specified by the HDMI Specification v1.3 through  $I^2S$ , S/PDIF and optional one-bit audio outputs. The one-bit audio outputs take on the pins used by  $I^2S$  outputs, so only one between the two could be activated at a time.

#### I<sup>2</sup>S

Four I<sup>2</sup>S outputs are provided to support 8-channel uncompressed audio data at up to 192kHz sample rate. A coherent multiple (master) clock MCLK is generated at pin 79 to facilitate proper functions of mainstream backend audio DAC ICs. The supported multiplied factor and sample frequency as well as the resultant MCLK frequencies are summarized in Table 2.

| Multiple of audio | Audio sample frequency |         |        |         |        |           |           |  |  |

|-------------------|------------------------|---------|--------|---------|--------|-----------|-----------|--|--|

| sample frequency  | 32kHz                  | 44.1kHz | 48kHz  | 88.2kHz | 96kHz  | 176.4kHz  | 192kHz    |  |  |

| 128               | 4.096                  | 5.645   | 6.144  | 11.290  | 12.288 | 22.579    | 24.576    |  |  |

| 256               | 8.192                  | 11.290  | 12.288 | 22.579  | 24.576 | 45.158    | 49.152    |  |  |

| 384               | 12.288                 | 16.934  | 18.432 | 33.869  | 36.864 | 67.738    | 73.728    |  |  |

| 512               | 16.384                 | 22.579  | 24.576 | 45.158  | 49.152 | 90.317    | 98.304    |  |  |

| 640               | 20.480                 | 28.224  | 30.720 | 56.448  | 61.440 | (112.896) | (122.880) |  |  |

| 768               | 24.576                 | 33.868  | 36.864 | 67.738  | 73.728 | (135.475) | (147.456) |  |  |

| 896               | 28.672                 | 39.514  | 43.008 | 79.027  | 86.016 | (158.054) | (172.032) |  |  |

| 1024              | 32.768                 | 45.158  | 49.152 | 90.316  | 98.304 | (180.634) | (196.608) |  |  |

Table 2. Output MCLK frequencies (MHz) supported by the IT6604

#### Notes:

The MCLK frequencies in parenthesis are MCLK frequencies over 100MHz. These frequencies are implemented

in the IT6604 and could be output through register setting as well. However, the I/O circuit of the MCLK pin does

not guarantee to be operating at such a high frequency under normal operation conditions. In addition, few audio

backend ICs such as DACs support such high MCLK frequencies. Therefore, using the MCLKs in parenthesis is

strongly discouraged.

#### S/PDIF

The S/PDIF output provides 2-channel uncompressed PCM data (IEC 60958) or compressed multi-channel data (IEC 61937) at up to 192kHz. By default the clock of S/PDIF is carried within the datastream itself via coding. The IT6604 also supplies coherent MCLK in cases of S/PDIF output to help ease the implementation with certain audio processing ICs.

### One-Bit Audio (DSD/SACD)

Direct stream digital (DSD) audio is an one-bit audio format which is prescribed by Super Audio CD (SACD) to provide superiore audio hearing experiences. Based on the register setting of the system

www.ite.com.tw Sep-2010 Rev:0.9 12/36

### IT6604

controller, the IT6604 outputs DSD audio optionally through existing I<sup>2</sup>S output pins. A total of 8 data outputs are provided for right channels and left channels. Refer to Pin Description on page 5 for detailed port-to-pin mapping.

#### **High-Bit-Rate Audio (HBR)**

High-Bit-Rate Audio is also new to the HDMI standard. It is called upon by high-end audio system such as DTS-HD and Dolby TrueHD. No specific interface is defined by the HBR standard. The IT6604 supports HBR audio in two ways. One is to employ the four I<sup>2</sup>S outputs simultaneously, where the original streaming DSD audio is broken into four parallel data streams. The other is to use the S/PDIF output port. The data rate in the later case is as high as 98.304Mbps. A coherent MCLK is generated by the IT6604 for the backend audio processors.

#### **Smart Audio Error Detection**

Some previous HDMI Sink products were reported to generate unbearably harsh sounds during hot-plug/unplug as well as unspecified audio error. Like its predecessor IT6603, the IT6604 prides itself for detecting all kinds of audio error and soft-mutes the audio accordingly, therefore preventing unpleasant noise from outputting.

## **Interrupt Generation**

To provide automatic format setting, hot plug/unplug handling and error handling, the system micro-controller should monitor the interrupt signal output at Pin 91 (INT#). The IT6604 generates an interrupt signal whenever events involving the following signals or situations occur:

- 1. A status change of incoming 5V power signals at pin 31 (corresponding to plug/unplug)

- 2. Stable video is acquired (SCDT at pin 90 is asserted)

- 3. Events of audio errors and/or audio mute

- 4. Events of ECC errors

- 5. Video mode change

Without software intervention the hardware of the IT6604 should be able to output some sort of displayable video data. However, this video could be in the wrong format or color space. Also, hardware alone is not sufficient in handling the exception events listed above. The micro-controller must monitor the INT# signal carefully and poll the corresponding registers for optimum operation.

# **Configuration and Function Control**

The IT6604 comes with three serial programming ports: one for interfacing with micro-controller, the other two allowing access by HDMI Sources through the two DDC channels of the HDMI links.

The serial programming interface for interfacing the micro-controller is a slave interface, comprising

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 13/36

## IT6604

PCSCL (Pin 25) and PCSDA (Pin 24). The micro-controller uses this interface to monitor all the statuses and control all the functions. Two device addresses are available, depending on the input logic level of PCADR (Pin 93). If PCADR is pulled high by the user, the device address is 0x92. If pulled low, 0x90.

The DDC I<sup>2</sup>C interface is present at DDCSCL0 (Pin 30) & DDCSDA0 (Pin 29). With the interfaces, the IT6604 responds to the access of HDMI Sources via the DDC channels. HDMI Sources use the interfaces to perform HDCP authentication with the IT6604.

All serial programming interfaces conform to standard I<sup>2</sup>C transactions and operate at up to 100kHz.

Sep-2010 Rev:0.9 14/36 www.ite.com.tw

# **Electrical Specifications**

## **Absolute Maximum Ratings**

| Symbol           | Parameter                       | Min. | Тур                   | Max      | Unit |

|------------------|---------------------------------|------|-----------------------|----------|------|

| IVDD             | Core logic supply voltage       | -0.3 |                       | 2.5      | V    |

| OVDD             | I/O pins supply voltage         | -0.3 |                       | 4.0      | V    |

| AVCC33           | HDMI analog frontend power      | -0.3 |                       | 4.0      | V    |

| AVCC18           | HDMI analog frontend power      | -0.3 |                       | 2.5      | V    |

| PVCC18           | HDMI receiver PLL power         | -0.3 |                       | 2.5      | V    |

| APVDD18          | HDMI audio PLL power            | -0.3 | 1                     | 2.5      | V    |

| XTALVDD33        | Power for crystal oscillator    | -0.3 |                       | 4.0      | V    |

| REGVCC           | Power for regulator             | -0.3 | $\mathcal{O}_{\cdot}$ | 4.0      | V    |

| VI               | Input voltage                   | -0.3 | L                     | OVDD+0.3 | V    |

| Vo               | Output voltage                  | 0.3  |                       | OVDD+0.3 | V    |

| TJ               | Junction Temperature            | 50   |                       | 125      | °C   |

| T <sub>STG</sub> | Storage Temperature             | -65  |                       | 150      | °C   |

| ESD_HB           | Human body mode ESD sensitivity | 2000 |                       |          | V    |

| ESD_MM           | Machine mode ESD sensitivity    | 200  |                       |          | ٧    |

#### Notes:

## **Functional Operation Conditions**

| Symbol               | Parameter                               | Min.  | Тур | Max   | Unit      |

|----------------------|-----------------------------------------|-------|-----|-------|-----------|

| IVDD                 | Core logic supply voltage               | 1.6   | 1.8 | 2.0   | V         |

| OVDD                 | I/O pins supply voltage                 | 2.97  | 3.3 | 3.63  | V         |

| AVCC33               | HDMI analog frontend power <sup>2</sup> | 3.135 | 3.3 | 3.465 | V         |

| AVCC18               | HDMI analog frontend power              | 1.6   | 1.8 | 2.0   | V         |

| PVCC18               | HDMI receiver PLL power                 | 1.6   | 1.8 | 2.0   | V         |

| APVDD18              | HDMI audio PLL power                    | 1.6   | 1.8 | 2.0   | V         |

| XTALVDD33            | Power for crystal oscillator            | 3.0   | 3.3 | 3.6   | V         |

| REGVCC               | Power for regulator                     | 3.0   | 3.3 | 3.6   | V         |

| V <sub>CCNOISE</sub> | Supply noise                            |       |     | 100   | $mV_{pp}$ |

| T <sub>A</sub>       | Ambient temperature                     | 0     | 25  | 70    | °C        |

| $\Theta_{ja}$        | Junction to ambient thermal resistance  |       |     |       | °C/W      |

#### Notes:

- 1. AVCC33, AVCC18, PVCC18 and APVDD18 should be regulated.

- 2. AVCC33 supplies the termination voltage. Therefore the range is specified by the HDMI Standard.

www.ite.com.tw Sep-2010 Rev:0.9 15/36

<sup>1.</sup> Stresses above those listed under Absolute Maximum Ratings might result in permanent damage to the device.

### **Operation Supply Current Specification**

| Symbol                  | Parameter                                                   | PCLK         | Тур | Max  | Unit |

|-------------------------|-------------------------------------------------------------|--------------|-----|------|------|

| I <sub>IVDD_OP</sub>    | IVDD current under normal operation                         | 27MHz        | 38  | 42   | mA   |

|                         |                                                             | 74.25MHz     | 86  | 95   | mA   |

|                         |                                                             | 148.5MHz     | 147 | 162  | mA   |

|                         |                                                             | 222.75MHz    | 185 | 204  | mA   |

| I <sub>OVDD_OP</sub>    | OVDD current under normal operation                         | 27MHz        | 6   | 7.   | mA   |

|                         | (with 20pF capacitive output loading)                       | 74.25MHz     | 18  | 20   | mA   |

|                         |                                                             | 148.5MHz     | 26  | 29   | mA   |

|                         |                                                             | 222.75MHz    | 29  | 32   | mA   |

| I <sub>AVCC18_OP</sub>  | AVCC18 current under normal operation                       | 27MHz        | 49  | 54   | mA   |

|                         | (with input Vdiff= 750 mV)                                  | 74.25MHz     | 64  | 71   | mA   |

|                         |                                                             | 148.5MHz     | 79  | 88   | mA   |

|                         |                                                             | 222.75MHz    | 97  | 105  | mA   |

| I <sub>AVCC33_OP</sub>  | AVCC33 current under normal operation                       | 27MHz        | 83  | 89   | mA   |

|                         | (with input Vdiff= 750 mV)                                  | 74.25MHz     | 83  | 89   | mA   |

|                         | (a)                                                         | 148.5MHz     | 83  | 89   | mA   |

|                         | 260                                                         | 222.75MHz    | 83  | 89   | mA   |

| I <sub>PVCC18_OP</sub>  | PVCC18 current under normal operation                       | 27MHz        | 5   | 5    | mA   |

|                         |                                                             | 74.25MHz     | 13  | 14   | mA   |

|                         |                                                             | 148.5MHz     | 22  | 24   | mA   |

|                         |                                                             | 222.75MHz    | 32  | 35   | mA   |

| I <sub>APVDD18_OP</sub> | APVDD18 current under normal operation                      | 27MHz        | 6   | 6    | mA   |

|                         |                                                             | 74.25MHz     | 6   | 6    | mA   |

|                         | 5-X-X-X-X-X-X-X-X-X-X-X-X-X-X-X-X-X-X-X                     | 148.5MHz     | 6   | 6    | mA   |

|                         |                                                             | 222.75MHz    | 6   | 6    | mA   |

| I <sub>XTALVDD33</sub>  | XTALVDD33 current under normal operation                    | (all speeds) | 1   | 1    | mA   |

| I <sub>REGVCC</sub>     | REGVCC current under normal operation                       | (all speeds) | 0   | 0    | mA   |

| PW <sub>TOTAL_OP</sub>  | Total power consumption under normal operation <sup>3</sup> | 27MHz        | 473 | 561  | mW   |

|                         |                                                             | 74.25MHz     | 641 | 764  | mW   |

| = 1                     |                                                             | 148.5MHz     | 820 | 983  | mW   |

|                         |                                                             | 222.75MHz    | 949 | 1132 | mW   |

#### Notes:

- Typ: OVDD=AVCC33=XTALVDD33=REGVCC=3.3V, IVDD=AVCC18=PVCC18=APVDD18=1.8V Max: OVDD=AVCC33= XTALVDD33=REGVCC=3.6V, IVDD=AVCC18=PVCC18=APVDD18=1.98V

- 2. PCLK=27MHz: 480p with 48kHz/8-channel audio,

- PCLK=74.25MHz: 1080i with 192kHz/8-channel audio,

- PCLK=148.5MHz: 1080p with 192kHz/8-channel audio,

- PCLK=222.75MHz: 1080p@36-bit Deep Color with 192kHz/8-channel audio

- 3. PW<sub>TOTAL OP</sub> are calculated by multiplying the supply currents with their corresponding supply voltage and summing up all the items.

www.ite.com.tw Sep-2010 Rev:0.9 16/36

### 4. DC Electrical Specification

Under functional operation conditions

| Symbol            | Parameter                                                     | Pin Type | Conditions                 | Min. | Тур | Max  | Unit |

|-------------------|---------------------------------------------------------------|----------|----------------------------|------|-----|------|------|

| $V_{IH}$          | Input high voltage <sup>1</sup>                               | LVTTL    |                            | 2.0  |     |      | V    |

| V <sub>IL</sub>   | Input low voltage <sup>1</sup>                                | LVTTL    |                            |      |     | 0.8  | V    |

| V <sub>T</sub>    | Switching threshold <sup>1</sup>                              | LVTTL    |                            |      | 1.5 |      | V    |

| V <sub>T-</sub>   | Schmitt trigger negative going threshold voltage <sup>1</sup> | Schmitt  |                            | 0.8  | 1.1 | 30   | V    |

| V <sub>T+</sub>   | Schmitt trigger positive going threshold voltage <sup>1</sup> | Schmitt  |                            |      | 1.6 | 2.0  | V    |

| V <sub>OL</sub>   | Output low voltage <sup>1</sup>                               | LVTTL    | I <sub>OL</sub> =2~16mA    | 1    | >   | 0.4  |      |

| V <sub>OH</sub>   | Output high voltage <sup>1</sup>                              | LVTTL    | I <sub>OH</sub> =-2~-16mA  | 2.4  |     |      |      |

| I <sub>IN</sub>   | Input leakage current <sup>1</sup>                            | all      | V <sub>IN</sub> =5.5V or 0 |      | ±5  |      | μΑ   |

| I <sub>OZ</sub>   | Tri-state output leakage current <sup>1</sup>                 | all      | V <sub>IN</sub> =5.5V or 0 |      | ±10 |      | μΑ   |

| I <sub>OL</sub>   | Serial programming output sink current <sup>2</sup>           | Schmitt  | V <sub>OUT</sub> =0.2V     | 4    |     | 16   | mA   |

| $V_{\text{diff}}$ | TMDS input differential swing <sup>3</sup>                    | TMDS     | $R_{EXT}$ =500 $\Omega$    | 150  |     | 1200 | mV   |

#### Notes:

- 1. Guaranteed by I/O design.

- 2. The serial programming output ports are not real open-drain drivers. Sink current is guaranteed by I/O design under the condition of driving the output pin with 0.2V. In a real I<sup>2</sup>C environment, multiple devices and pull-up resistors could be present on the same bus, rendering the effective pull-up resistance much lower than that specified by the I<sup>2</sup>C Standard. When set at maximum current, the serial programming output ports of the IT6604 are capable of pulling down an effective pull-up resistance as low as 500Ω connected to 5V termination voltage to the standard I<sup>2</sup>C V<sub>IL</sub>. When experiencing insufficient low level problem, try setting the current level to higher than default. Refer to IT6604 Programming Guide for proper register setting.

- 3. Limits defined by HDMI 1.4 standard

#### **Audio AC Timing Specification**

Under functional operation conditions

| Symbol               | Parameter                                     | Conditions       | Min. | Тур | Max  | Unit |

|----------------------|-----------------------------------------------|------------------|------|-----|------|------|

| F <sub>S_I2S</sub>   | I <sup>2</sup> S sample rate                  | Up to 8 channels | 32   |     | 192  | kHz  |

| F <sub>S_SPDIF</sub> | S/PDIF sample rate                            | 2 channels       | 32   |     | 192  | kHz  |

| F <sub>S_DSD</sub>   | DSD sample rate                               | Up to 8 channels |      |     | 96   | kHz  |

| F <sub>XTAL</sub>    | External audio crystal frequency <sup>1</sup> | ±300ppm accuracy | 24   | 27  | 28.5 | MHz  |

#### Notes:

1. The IT6604 is designed to work in default with a 27MHz crystal for audio functions. Crystals of other frequencies within the designated functional range mandate certain register programming for proper functioning.

www.ite.com.tw Sep-2010 Rev:0.9 17/36

### **Video AC Timing Specification**

Under functional operation conditions

| Symbol             | Parameter                                    | Conditions          | Min. | Тур | Max   | Unit |

|--------------------|----------------------------------------------|---------------------|------|-----|-------|------|

| T <sub>pixel</sub> | PCLK pixel clock period <sup>1</sup>         | Single-edged        |      |     | 40    | ns   |

| F <sub>pixel</sub> | PCLK pixel clock frequency <sup>1</sup>      | clocking            | 25   |     | 225   | MHz  |

| T <sub>CDE</sub>   | PCLK dual-edged clock period <sup>2</sup>    | Dual added alcoking | 8.88 |     | 40    | ns   |

| F <sub>CDE</sub>   | PCLK dual-edged clock frequency <sup>2</sup> | Dual-edged clocking | 25   |     | 112.5 | MHz  |

| T <sub>PDUTY</sub> | PCLK clock duty cycle                        |                     | 40%  |     | 60%   |      |

#### Notes:

- 1. Fpixel is the inverse of Tpixel. Operating frequency range is given here while the actual video clock frequency should comply with all video timing standards. Refer to Table 1 for supported video timings and corresponding pixel frequencies.

- 2. 12-bit dual-edged clocking is supported up to 74.5MHz of PCLK frequency, which covers 720p/1080i.

- ancy, aching et 3. All setup time and hold time specifications are with respect to the latching edge of PCLK selected by the user through register programming.

Sep-2010 Rev:0.9 18/36 www.ite.com.tw

# **Video Data Bus Mappings**

The IT6604 supports various output data mappings and formats, including those with embedded control signals only. Corresponding register setting is to be taken care of for any chosen input data mappings. Refer to IT6604 Programming Guide for detailed instruction.

| Color Space | Video Format | Bus Width         | H/Vsync            | Clocking         | Table |  |  |  |

|-------------|--------------|-------------------|--------------------|------------------|-------|--|--|--|

| DCD         | 4.4.4        | 24/30             | Seperate           | 1X               | 4     |  |  |  |

| RGB         | 4:4:4        | 24/30             | Seperate           | 0.5X, Dual-edged | 4     |  |  |  |

|             | 4:4:4        | 24/30             | Seperate           | 1X               | 4     |  |  |  |

|             | 4.4.4        | 24/30             | Seperate           | 0.5X, Dual-edged | 4     |  |  |  |

| YCbCr       |              | 16/20             |                    | 1X               | 5     |  |  |  |

| 10001       | 4:2:2        | 10/20             | Embedded           | 0 <sub>1X</sub>  | 6     |  |  |  |

|             |              | 8/10              | Seperate           | 2X               | 8     |  |  |  |

|             |              | 0/10              | Embedded           | 2X               | 7     |  |  |  |

|             | Table 3. C   | Output video form | at supported by tl | ne IT6604        |       |  |  |  |

| 1860A.3     |              |                   |                    |                  |       |  |  |  |

Table 3. Output video format supported by the IT6604

Sep-2010 Rev:0.9 19/36 www.ite.com.tw

## RGB 4:4:4 and YCbCr 4:4:4 with Separate Syncs

|          | RO     | GB .   | YC     | bCr    |

|----------|--------|--------|--------|--------|

| Pin Name | 30-bit | 24-bit | 30-bit | 24-bit |

| QE2      | В0     | NC     | Cb0    | NC     |

| QE3      | B1     | NC     | Cb1    | NC     |

| QE4      | B2     | В0     | Cb2    | Cb0    |

| QE5      | В3     | B1     | Cb3    | Cb1    |

| QE6      | B4     | B2     | Cb4    | Cb2    |

| QE7      | B5     | B3     | Cb5    | Cb3    |

| QE8      | B6     | B4     | Cb6    | Cb4    |

| QE9      | B7     | B5     | Cb7    | Cb5    |

| QE10     | B8     | B6     | Cb8    | Cb6    |

| QE11     | B9     | B7     | Cb9    | Cb7    |

| QE14     | G0     | NC     | Y0     | CAC.   |

| QE15     | G1     | NC     | Y1     | UNC    |

| QE16     | G2     | G0     | Y2 📞   | Y0     |

| QE17     | G3     | G1     | Y3     | Y1     |

| QE18     | G4     | G2     | Y4     | Y2     |

| QE19     | G5     | G3     | Y5     | Y3     |

| QE20     | G6     | G4     | Y6     | Y4     |

| QE21     | G7     | G5     | Y7     | Y5     |

| QE22     | G8     | G6     | Y8     | Y6     |

| QE23     | G9     | G7     | Y9     | Y7     |

| QE26     | R0     | NC     | Cr0    | NC     |

| QE27     | R1 //  | ) NC   | Cr1    | NC     |

| QE28     | R2     | R0     | Cr2    | Cr0    |

| QE29     | R3     | R1     | Cr3    | Cr1    |

| QE30     | R4     | R2     | Cr4    | Cr2    |

| QE31     | R5     | R3     | Cr5    | Cr3    |

| QE32     | R6     | R4     | Cr6    | Cr4    |

| QE33     | R7     | R5     | Cr7    | Cr5    |

| QE34     | R8     | R6     | Cr8    | Cr6    |

| QE35     | R9     | R7     | Cr9    | Cr7    |

| HSYNC    | HSYNC  | HSYNC  | HSYNC  | HSYNC  |

| VSYNC    | VSYNC  | VSYNC  | VSYNC  | VSYNC  |

| DE       | DE     | DE     | DE     | DE     |

Table 4. RGB & YCbCr 4:4:4 Mappings

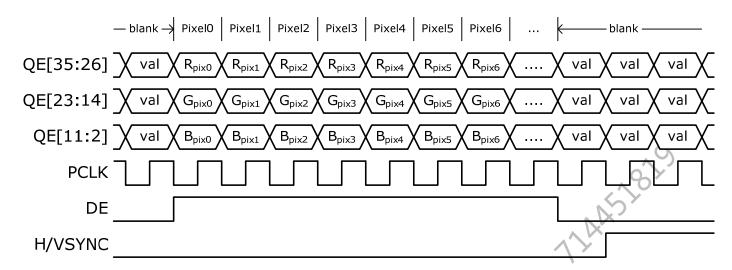

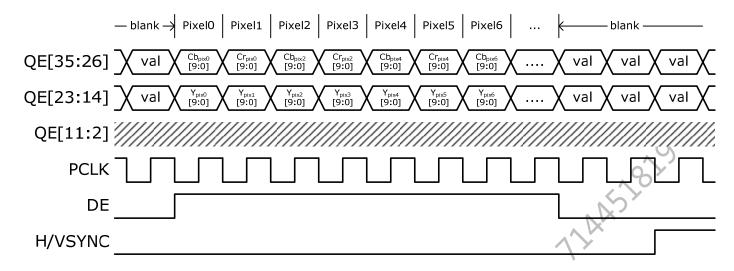

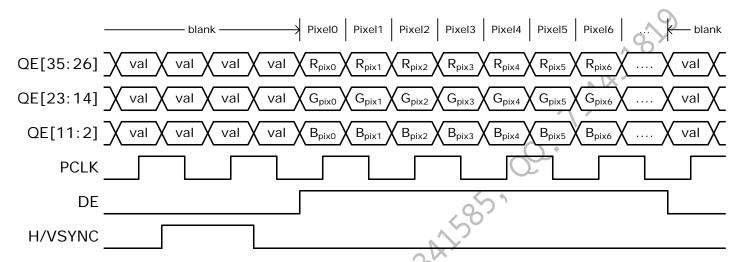

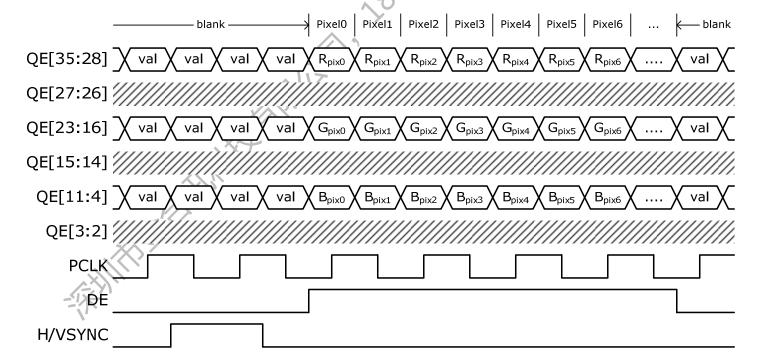

These are the simpliest formats, with a complete definition of every pixel in each clock period. Timing examples of 30-bit RGB 4:4:4 is depicted in Figure 4 respectively.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 20/36

Figure 4. 30-bit RGB 4:4:4 Timing Diagram

Sep-2010 Rev:0.9 21/36 www.ite.com.tw

## YCbCr 4:2:2 with Separate Syncs

|          | 20-      | -bit       | 16       | -bit       |

|----------|----------|------------|----------|------------|

| Pin Name | Pixel#2N | Pixel#2N+1 | Pixel#2N | Pixel#2N+1 |

| QE2      | NC       | NC         | NC       | NC         |

| QE3      | NC       | NC         | NC       | NC         |

| QE4      | NC       | NC         | NC       | NC         |

| QE5      | NC       | NC         | NC       | NC         |

| QE6      | NC       | NC         | NC       | NC         |

| QE7      | NC       | NC         | NC       | NC         |

| QE8      | NC       | NC         | NC       | NC 1       |

| QE9      | NC       | NC         | NC       | NC _       |

| QE10     | NC       | NC         | NC       | NC \       |

| QE11     | NC       | NC         | NC       | NÇ         |

| QE14     | Y0       | Y0         | NC       | CAC.       |

| QE15     | Y1       | Y1         | NC       | UNC        |

| QE16     | Y2       | Y2         | Y0 <     | Y0         |

| QE17     | Y3       | Y3         | Y19      | Y1         |

| QE18     | Y4       | Y4         | Y2       | Y2         |

| QE19     | Y5       | Y5         | Y3       | Y3         |

| QE20     | Y6       | Y6 \       | Y4       | Y4         |

| QE21     | Y7       | Y7 0       | Y5       | Y5         |

| QE22     | Y8       | Y8         | Y6       | Y6         |

| QE23     | Y9       | Y9         | Y7       | Y7         |

| QE26     | Cb0      | Cr0        | NC       | NC         |

| QE27     | Cb1      | Cr1        | NC       | NC         |

| QE28     | Cb2      | Cr2        | Cb0      | Cr0        |

| QE29     | Cb3      | Cr3        | Cb1      | Cr1        |

| QE30     | Cb4      | Cr4        | Cb2      | Cr2        |

| QE31     | Cb5      | Cr5        | Cb3      | Cr3        |

| QE32     | Cb6      | Cr6        | Cb4      | Cr4        |

| QE33     | Cb7      | Cr7        | Cb5      | Cr5        |

| QE34     | Cb8      | Cr8        | Cb6      | Cr6        |

| QE35     | Cb9      | Cr9        | Cb7      | Cr7        |

| HSYNC    | HSYNC    | HSYNC      | HSYNC    | HSYNC      |

| VSYNC    | VSYNC    | VSYNC      | VSYNC    | VSYNC      |

| DE       | DE       | DE         | DE       | DE         |

Table 5. Mappings of YCbCr 4:2:2 with separate syncs

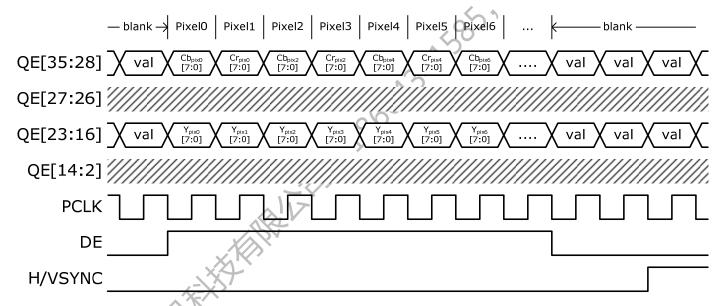

YCbCr 4:2:2 format does not have one complete pixel for every clock period. Luminace channel (Y) is given for every pixel, while the two chroma channels are given alternatively on every other clock period. The average bit amount of Y is twice that of Cb or Cr. Depending on the bus width, each component could take on different lengths. The DE period should contain an even number of clock periods. Figure 5 gives a timing example of 20-bit YCbCr 4:2:2.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 22/36

Figure 5. 20-bit YCbCr 4:2:2 with separate syncs

Figure 6. 16-bit YCbCr 4:2:2 with separate syncs

Sep-2010 Rev:0.9 23/36

## YCbCr 4:2:2 with Embedded Syncs

|          | 20-      | -bit       | 16       | -bit       |

|----------|----------|------------|----------|------------|

| Pin Name | Pixel#2N | Pixel#2N+1 | Pixel#2N | Pixel#2N+1 |

| QE2      | NC       | NC         | NC       | NC         |

| QE3      | NC       | NC         | NC       | NC         |

| QE4      | NC       | NC         | NC       | NC         |

| QE5      | NC       | NC         | NC       | NC         |

| QE6      | NC       | NC         | NC       | NC         |

| QE7      | NC       | NC         | NC       | NC         |

| QE8      | NC       | NC         | NC       | NC         |

| QE9      | NC       | NC         | NC       | NC _       |

| QE10     | NC       | NC         | NC       | NC'        |

| QE11     | NC       | NC         | NC       | NÇ         |

| QE14     | Y0       | Y0         | NC       | Cyc.       |

| QE15     | Y1       | Y1         | NC       | UNC        |

| QE16     | Y2       | Y2         | Y0 📞     | Y0         |

| QE17     | Y3       | Y3         | Y19      | Y1         |

| QE18     | Y4       | Y4         | Y2       | Y2         |

| QE19     | Y5       | Y5         | Y3       | Y3         |

| QE20     | Y6       | Y6 \       | Y4       | Y4         |

| QE21     | Y7       | Y7 0       | Y5       | Y5         |

| QE22     | Y8       | Y8         | Y6       | Y6         |

| QE23     | Y9       | Y9         | Y7       | Y7         |

| QE26     | Cb0      | Cr0        | NC       | NC         |

| QE27     | Cb1      | Cr1        | NC       | NC         |

| QE28     | Cb2      | Cr2        | Cb0      | Cr0        |

| QE29     | Cb3      | Cr3        | Cb1      | Cr1        |

| QE30     | Cb4      | Cr4        | Cb2      | Cr2        |

| QE31     | Cb5      | Cr5        | Cb3      | Cr3        |

| QE32     | Cb6      | Cr6        | Cb4      | Cr4        |

| QE33     | Cb7      | Cr7        | Cb5      | Cr5        |

| QE34     | Cb8      | Cr8        | Cb6      | Cr6        |

| QE35     | Cb9      | Cr9        | Cb7      | Cr7        |

| HSYNC    | embedded | embedded   | embedded | embedded   |

| VSYNC    | embedded | embedded   | embedded | embedded   |

| DE       | embedded | embedded   | embedded | embedded   |

Table 6. Mappings of YCbCr 4:2:2 with embedded syncs

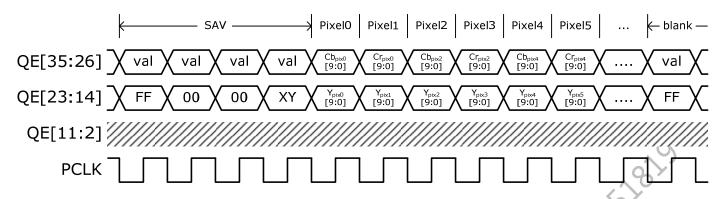

Similar to YCbCr 4:2:2 with Separate Sync. The only difference is that the syncs are now non-explicit, i.e. embedded. Bus width could be 16-bit, 20-bit. Figure 7 gives a timing example of 20-bit YCbCr 4:2:2 and Figure 8 that of 16-bit. Note that while "embedded syncs" implies that neither DE nor H/VSYNC are required, the IT6604 optionally output these signals via proper register setting to ease the design for some backend processors.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 24/36

Figure 7. 20-bit YCbCr 4:2:2 with embedded syncs

Figure 8. 16-bit YCbCr 4:2:2 with embedded syncs

Sep-2010 Rev:0.9 25/36

#### **CCIR-656 Format**

|          | 10-bit   |           | 8-bit    |           |  |

|----------|----------|-----------|----------|-----------|--|

| Pin Name | PCLK#2N  | PCLK#2N+1 | PCLK#2N  | PCLK#2N+1 |  |

| QE2      | NC       | NC        | NC       | NC        |  |

| QE3      | NC       | NC        | NC       | NC        |  |

| QE4      | NC       | NC        | NC       | NC        |  |

| QE5      | NC       | NC        | NC       | NC        |  |

| QE6      | NC       | NC        | NC       | NC        |  |

| QE7      | NC       | NC        | NC       | NC <      |  |

| QE8      | NC       | NC        | NC       | NC X      |  |

| QE9      | NC       | NC        | NC       | NEX       |  |

| QE10     | NC       | NC        | NC       | WC y      |  |

| QE11     | NC       | NC        | NC       | → NC      |  |

| QE14     | C0       | Y0        | NC C     | Q NC      |  |

| QE15     | C1       | Y1        | NC       | ) NC      |  |

| QE16     | C2       | Y2        | C0       | Y0        |  |

| QE17     | C3       | Y3        | (Ch)     | Y1        |  |

| QE18     | C4       | Y4        | C2       | Y2        |  |

| QE19     | C5       | Y5        | C3       | Y3        |  |

| QE20     | C6       | Y6        | C4       | Y4        |  |

| QE21     | C7       | Y7 (0     | C5       | Y5        |  |

| QE22     | C8       | Y8        | C6       | Y6        |  |

| QE23     | C9       | Y9        | C7       | Y7        |  |

| QE26     | NC       | NC        | NC       | NC        |  |

| QE27     | NC 4     | NC NC     | NC       | NC        |  |

| QE28     | NC 11-   | NC        | NC       | NC        |  |

| QE29     | NSQLV    | NC        | NC       | NC        |  |

| QE30     | 140      | NC        | NC       | NC        |  |

| QE31     | XXX      | NC        | NC       | NC        |  |

| QE32     | NC       | NC        | NC       | NC        |  |

| QE33     | NC NC    | NC        | NC       | NC        |  |

| QE34     | NC       | NC        | NC       | NC        |  |

| QE35     | NC       | NC        | NC       | NC        |  |

| HSYNC    | embedded | embedded  | embedded | embedded  |  |

| VSYNC    | embedded | embedded  | embedded | embedded  |  |

| DE       | embedded | embedded  | embedded | embedded  |  |

**Table 7. Mappings of CCIR-656**

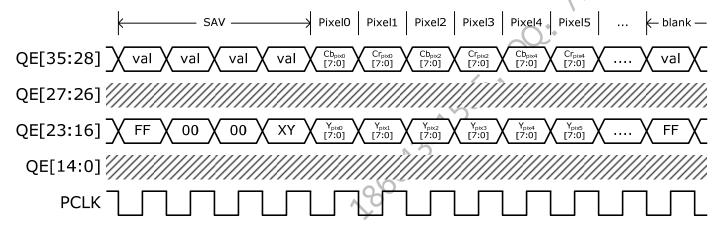

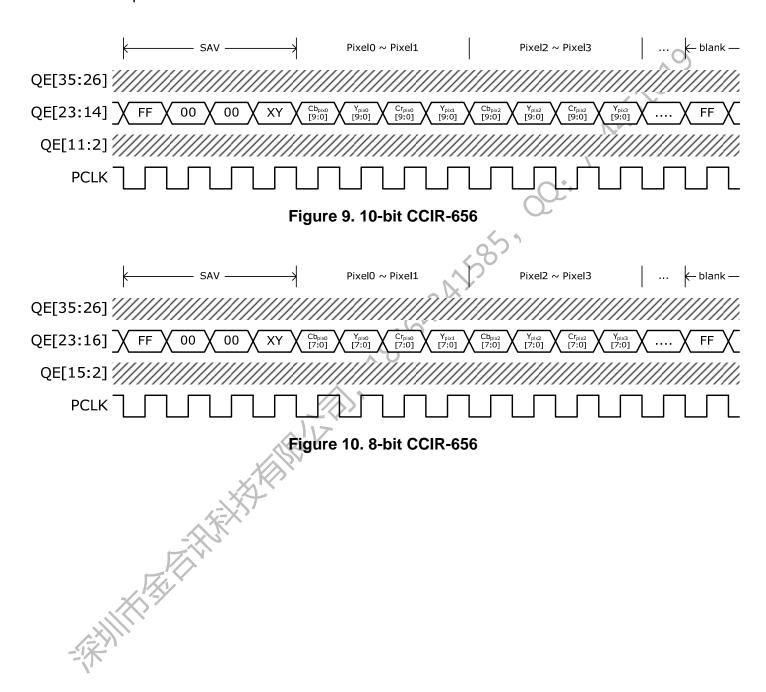

The CCIR-656 format is yet another variation of the YCbCr formats. The bus width is further reduced by half compared from the previous YCbCr 4:2:2 formats, to either 8-bit or 10-bit. To compensate for the halving of data bus, PCLK frequency is doubled. With the double-rate output clock, luminance channel (Y) and chroma channels (Cb or Cr) are alternated. The syncs signals are embedded in the Y-channel. Normally this format is used only for 480i, 480p, 576i and 576p. The IT6604 supports CCIR-656 format of up to 720p or 1080i, with the doubled-rate clock running at 148.5MHz. CCIR-656

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 26/36

format supports embedded syncs only. Figure 9 and Figure 10 give examples of 10-bit and 8-bit CCIR-656 respectively. Note that while "embedded syncs" implies that neither DE nor H/VSYNC are required, the IT6604 optionally output these signals via proper register setting to ease the design for some backend processors.

www.ite.com.tw Sep-2010 Rev:0.9 27/36

## CCIR-656 + separate syncs

|          | 10-     | -bit      | 8-bit   |           |  |

|----------|---------|-----------|---------|-----------|--|

| Pin Name | PCLK#2N | PCLK#2N+1 | PCLK#2N | PCLK#2N+1 |  |

| QE2      | NC      | NC        | NC      | NC        |  |

| QE3      | NC      | NC        | NC      | NC        |  |

| QE4      | NC      | NC        | NC      | NC        |  |

| QE5      | NC      | NC        | NC      | NC        |  |

| QE6      | NC      | NC        | NC      | NC        |  |

| QE7      | NC      | NC        | NC      | NC <      |  |

| QE8      | NC      | NC        | NC      | NC X      |  |

| QE9      | NC      | NC        | NC      | NE        |  |

| QE10     | NC      | NC        | NC      | WC >      |  |

| QE11     | NC      | NC        | NC      | NC NC     |  |

| QE14     | C0      | Y0        | NC      | O NC      |  |

| QE15     | C1      | Y1        | NC      | NC        |  |

| QE16     | C2      | Y2        | C0      | Y0        |  |

| QE17     | C3      | Y3        | G       | Y1        |  |

| QE18     | C4      | Y4        | C2      | Y2        |  |

| QE19     | C5      | Y5        | C3      | Y3        |  |

| QE20     | C6      | Y6        | C4      | Y4        |  |

| QE21     | C7      | Y7 (0     | C5      | Y5        |  |

| QE22     | C8      | Y8        | C6      | Y6        |  |

| QE23     | C9      | Y9        | C7      | Y7        |  |

| QE26     | NC      | ∧ NC      | NC      | NC        |  |

| QE27     | NC /    | NC NC     | NC      | NC        |  |

| QE28     | NC 113  | NC        | NC      | NC        |  |

| QE29     | NECLLY  | NC        | NC      | NC        |  |

| QE30     | 1500    | NC        | NC      | NC        |  |

| QE31     | XXX     | NC        | NC      | NC        |  |

| QE32     | NC      | NC        | NC      | NC        |  |

| QE33     | X' NC   | NC        | NC      | NC        |  |

| QE34     | NC      | NC        | NC      | NC        |  |

| QE35     | NC      | NC        | NC      | NC        |  |

| HSYNC    | HSYNC   | HSYNC     | HSYNC   | HSYNC     |  |

| VSYNC    | VSYNC   | VSYNC     | VSYNC   | VSYNC     |  |

| DE       | DE      | DE        | DE      | DE        |  |

Table 8. Mappings of CCIR-656 + separate syncs

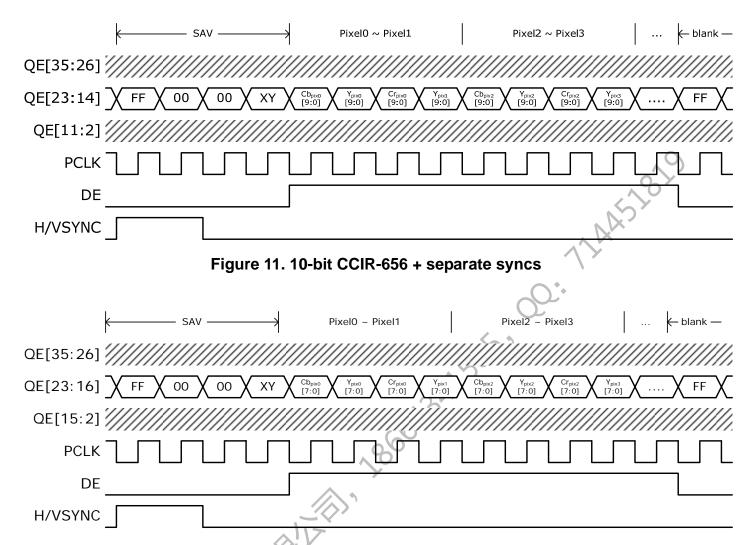

This format is not specified by CCIR-656. It's simply the previously mentioned CCIR-656 format plus separate syncs. Examples of this mode are given in Figure 11 and Figure 12.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 28/36

Figure 12. 8-bit CCIR-656 + separate syncs

Sep-2010 Rev:0.9 29/36

## RGB 4:4:4 and YCbCr 4:4:4 Triggered with 0.5X PCLK at Dual Edges

The bus mapping in this format is the same as that of RGB 4:4:4 and YCbCr 4:4:4 with Separate Syncs. The only difference is that the output video clock (PCLK) is now halved in frequency. The data are in turn to be latched in with both the rising and falling edges of the 0.5X PCLK.

Figure 13. 30-bit RGB 4:4:4 dual-edges triggered with 0.5X PCLK

Figure 14. 24-bit RGB 4:4:4 dual-edges triggered with 0.5X PCLK

www.ite.com.tw Sep-2010 Rev:0.9 30/36

# **System Design Consideration**

The IT6604 is a very high-speed interface chip. It receives TMDS differential signals at as high as 2.25Gbps and output TTL signals at up to 148.5MHz with 30-bit data bus. At such high speeds any PCB design imperfection could lead to compromised signal integrity and hence degraded performance. To get the optimum performance the system designers sould follow the guideline below when designing the application circuits and PCB layout.

- 1. Pin 50 (PVCC18) and Pin 49 (PVSS) should be supplied with clean power: ferrite-decoupled and capacitively-bypassed, since they supply the power for the receiver PLL, which is a crucial block in terms of receiving quality. Excess power noise might degrade the system performance.

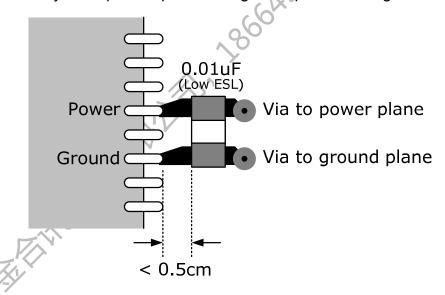

- 2. It is highly recommended that all power pins are decoupled to ground pins via capacitors of 0.01uF and 0.1uF. Low-ESL capacitors are prefered. Generally these capacitors should be placed on the same side of the PCB with the IT6604 and as close to the pins as possible, preferably within 0.5cm from the pins. It is also recommended that the power and ground traces run relatively short distances and are connected directly to respective power and ground planes through via holes.

Figure 15. Layout example for decoupling capacitors.

- 3. The IT6604 supports 30-bit output bus running at as high as 148.5MHz. To maintain signal integrity and lower EMI, the following guidelines should be followed:

- A. Employ **4-layer PCB** design, where a ground or power plane is directly placed under the signal buses at middle layes. The ground and power planes underneath these buses should be continuous in order to provide a solid return path for EM-wave introduced currents.

- B. Whenever possible, keep all TTL signal traces on the same layer with the IT6604 and the

www.ite.com.tw Sep-2010 Rev:0.9 31/36

backend scalers.

- C. TTL output traces to the scaler should be kept as short as possible

- D.  $33\Omega$  resistors could be placed in series to the output pins. This slow down the signal rising edges, reduces current spikes and lower the reflections.

- E. The PCLK signal should be kept away from other signal traces to avoid crosstalk interference. A general guideline is 2X the dielectric thickness. For example, if the dielectric layer between the signal layer and the immediate power/ground layer is 7 mil, then the PCLK trace should be kept at least 14 mil away from all other signal traces.

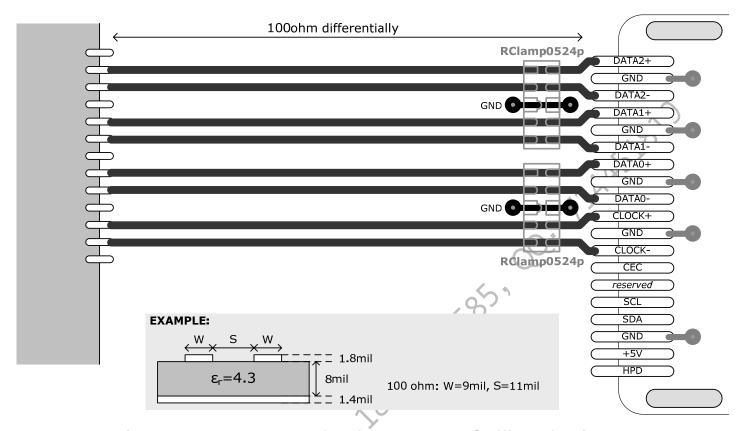

- 4. The characteristic impedance of all differential PCB traces should be kept at  $100\Omega$  all the way from the HDMI connector to the IT6604. This is crucial to the system performance at high speeds. When layouting these differential transmission lines, the following guidelines should be followed:

- A. The signals traces should be on the outside layers (TOP layer or BOTTOM layer) while beneath it there should be a continuous ground plane in order to maintain the so-called micro-strip transmission line structure, giving stable and well-defined characteristic impedances.

- B. Carefully choose the width and spacing of the differential transmission lines as their characteristic impedance depends on various parameters of the PCB: trace width, trace spacing, copper thickness, dielectric constant, dielectric thickness, etc. Careful 3D EM simulation is the best way to derive a correct dimension that enables a nominal  $100\Omega$  differential impedance.

- C. Cornering, through holes, crossing and any irregular signal routing should be minimized so as to prevent from disrupting the EM field and creating discontinuity in characteristic impedance.

- D. The IT6604 should be placed as close to the HDMI connector as possible. If the distance between the chip and the connector is under 2 cm, the reflections could be kept small even if the PCB traces do not have an  $100\Omega$  characteristic impedance. The extra signal attenuation contributed by the PCB traces could be minimized, too.

- 5. Special care should be taken when adding discrete ESD devices to all differential PCB traces (RX2P/M, RX1P/M, RX0P/M, RXCP/M). The IT6604 is designed to provide ESD protection for up to 2kV at these pins, which is good enough to prevent damages during assembly. To meet the system EMC specification, external discrete ESD diodes might be added. But note that adding discrete ESD diodes inevitably add capacitive loads, therefore degrade the electrical performance at high speeds. If not chosen carefully, these diodes coupled with less-than-optimal layout would prevent the system from passing the SINK TMDS-Differential Impedance test in the HDMI Compliance Test (Test ID 8-8). One should only use low-capacitance ESD diode to protect these high-speed pins. Commercially available devices such as Semtech's RClamp0524p that take into consideration of all aspects of designing and protecting high-speed transmission lines are recommended. (http://www.semtech.com/

www.ite.com.tw Sep-2010 Rev:0.9 32/36

products/product-detail.jsp?navId=H0,C2,C222,P3028).

Figure 16. Layout example for high-speed TMDS differential signals

6. By default Pin 51 (REXT) should be connected to ground via a  $500\Omega/1\%$  precision SMD resistor to provide for receiver termination calibration. If this pin is to be left open, be sure to set the **bit 6** of register **0x6A** to **'1'** in order to disable the termination calibration. Disabling the termination calibration would leave the value of termination impedance subject to process, supply voltage and temperature variation, sometimes rendering it out of specification and degrading the performance. Therefore it is highly recommended that this calibration function is left turned-on and a  $500\Omega/1\%$  resistor is connected between Pin 51 and ground. The resistor should be placed as close to the IT6604 as possible.

www.ite.com.tw Sep-2010 Rev:0.9 33/36

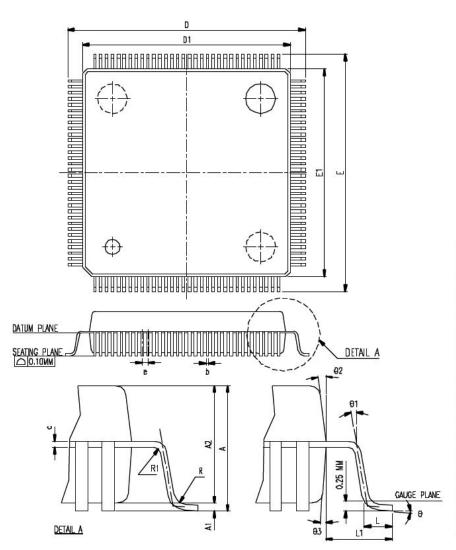

# **Package Dimensions**

| CATOU      | DIME | nsion in | 1 MM | DIME        | NSION IN    | INCH  |  |

|------------|------|----------|------|-------------|-------------|-------|--|

| SYMBOL     | MIN. | NOM.     | MAX. | MIN.        | NOM.        | MAX.  |  |

| Α          |      |          | 1.60 |             |             | D.063 |  |

| <b>A</b> 1 | 0.05 |          | 0.15 | D.001       | 9           | 0.006 |  |

| A2         | 1 35 | 1 40     | 1 45 | D 053       | D 055       | D 057 |  |

| b          | 0.13 | 0.16     | 0.19 | 0.005       | 0.006       | 0.007 |  |

| c          | 0.09 |          | 0.16 | O.DD4       |             | 0.006 |  |

| е          | 0    | 40 BASK  | C    | 0           | .016 BAS    | IC    |  |

| D          | 1    | 6.00 BAS | SIC  | 0           | 0.630 BASIC |       |  |

| D1         | 1    | 4.DD BAS | SIC  | D           | D.551 BASIC |       |  |

| Ε          | 1    | 6.00 BAS | SIC  | D.630 BASIC |             |       |  |

| E1         | 1    | 4.DD BAS | SIC  | D.551 BASIC |             |       |  |

| L          | 0.45 | 0.60     | 0.75 | 0.018       | 0.024       | 0.030 |  |

| L1         |      | 1.00 REF |      | 0 039 REF.  |             |       |  |

| R1         | 80.0 |          |      | 0.003       |             |       |  |

| R          | 80.0 |          | 0.20 | 0.003       |             | 0.008 |  |

| θ          | 0    | 3.5      | 7    | 0           | 35          | 7     |  |

| <b>8</b> 1 | 0    |          |      | 0           | 2           |       |  |

| 02         | 11   | 12       | 13   | 11          | 12          | 13    |  |

| 63         | -11  | 12       | 13   | 11          | 12          | 13    |  |

Figure 17. 128-pin LQFP Package Dimensions

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 34/36

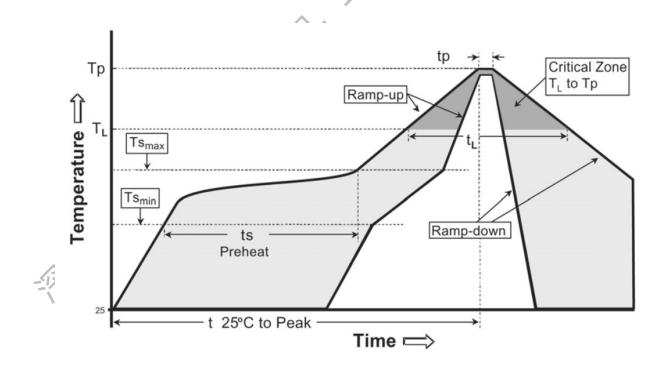

# **Classification Reflow Profiles**

| Reflow Profile                                    | Pb-Free Assembly |

|---------------------------------------------------|------------------|

| Average Ramp-Up Rate (Ts <sub>max</sub> to Tp)    | 3°C/second max.  |

| Preheat                                           |                  |

| -Temperature Min(Ts <sub>min</sub> )              | 150℃             |

| -Temperature Max(Ts <sub>max</sub> )              | 200℃             |

| -Time(ts <sub>min</sub> to ts ts <sub>max</sub> ) | 60-180 seconds   |

| Time maintained above:                            | 217°C            |

| -Temperature(T <sub>L</sub> )                     |                  |

| -Time(t <sub>L</sub> )                            | 60-150 seconds   |

| Peak Temperature(Tp)                              | 260 +0 /-5℃      |

| Time within 5 ℃ of actual Peak                    | 20,40 accords    |

| Temperature(tp)                                   | 20-40 seconds    |

| Ramp-Down Rate                                    | 6°C/second max.  |

| Time 25°C to Peak Temperature                     | 8 minutes max.   |

Note: All Temperature refer to topside of the package, measured on the package body surface.

<u>www.ite.com.tw</u> Sep-2010 Rev:0.9 35/36

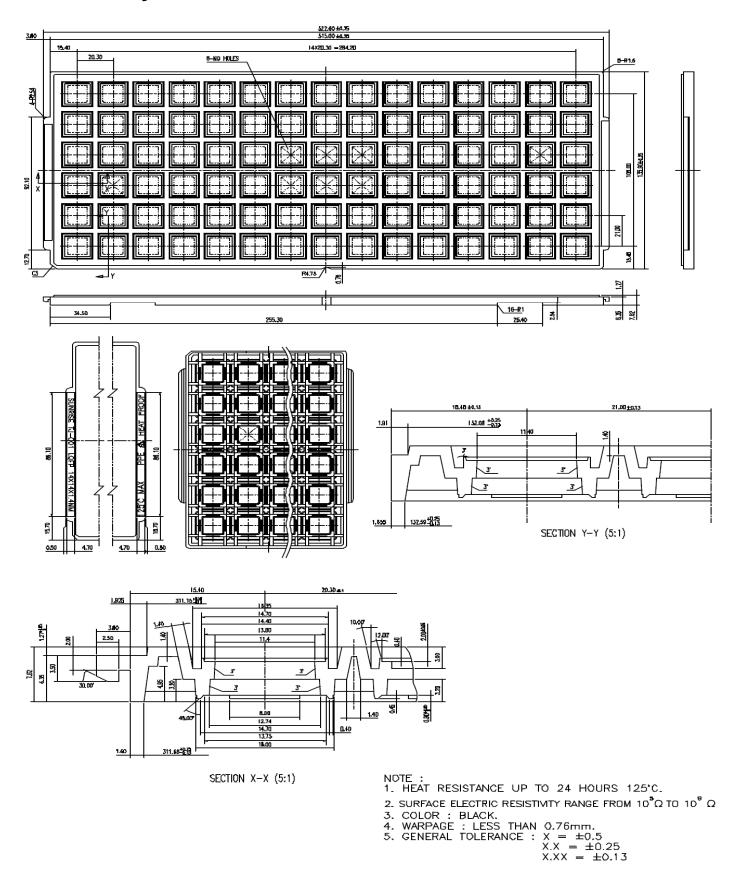

# **Carrier Tray Dimensions**

Sep-2010 Rev:0.9 36/36