# SPICE Circuit Simulations for the HCNR200 and HCNR201 Analog Optocouplers

**Application Note 5545**

By Jamshed Namdar Khan, Optocoupler Applications Engineer, Isolation Products Division, Avago Technologies

#### Introduction

The purpose of this application note is to showcase the ability of PSpice software to accurately predict and simulate the behavior of Avago's HCNR200 and HCNR201 analog optocouplers using the PSpice macro models provided by Avago Technologies. SPICE (Simulation Program with Integrated Circuit Emphasis) is now considered to be an indispensible tool for analog circuit designers.

Good macro models should accurately predict circuit performance with respect to the respective analog optocoupler data sheet parameters or specifications. PSpice or SPICE (henceforth, SPICE) simulations are an integral and indispensible part of any design engineers inventory of tools for a successful design project. Circuit simulations help to get an initial design concept off the ground and eventually allow one to tweak and optimize the prototype circuit for best possible circuit performance. The greatest benefit of circuit simulations is to verify and refine a design before building actual hardware or performing bench testing. Simulations minimize the time spent in the prototype testing phase and the associated expense.

#### Why Simulate?

Whatever circuit simulations may be able to perform or deliver for you, one thing they definitely would not be able to do is to actually design a circuit for you. Thus, let us first enumerate what is it that allures the designer to perform circuit simulations.

The primary impetus and thrust for circuit simulations is to minimize the time it takes to predict the performance of contemplated or proposed circuit designs. Compared to actually building and evaluating equivalent circuits for prototype testing, the time it takes to evaluate such circuits using SPICE is minuscule by comparison. In addition, these circuit simulations can be run countless times at various temperatures, biasing conditions, and component values and their tolerances in a fraction of the time it would take to breadboard and evaluate on the bench. When performing optocoupler SPICE simulations, it should be understood from the very outset that to the software does not simulate two fundamental aspects of optocouplers. Designers use optocouplers for two primary reasons: Insulation and Isolation. SPICE software does not model either of these two key or primary optocoupler features:

a. Insulation: This refers to the property of an optocoupler to provide high voltage breakdown protection across its optically designed insulation barrier between the two sides or two grounds. This parameter is defined in the data sheet as Viso (insulation withstand voltage). This is certified through optocoupler standards such as UL1577. In addition, the working voltage is defined as Viorm and is certified through the International Optocoupler safety standard such as the IEC 60747-5-5. The Viso specification is a one minute (min) momentary or transient insulation withstand rating. For example, under the UL1577 standard, the Viso rating of Avago optocouplers ranges from 2500 Vrms/min to 7500 Vrms/min and depends on the package type selected for the optocoupler. The working voltage, Viorm, is the continuous voltage that can be applied across the optocoupler insulation barrier forever, and Avago optocouplers are certified between 560 Vpeak to 1768 Vpeak, and again the specification depends on the package type selected. Unlike the Viso (UL rating) which is based on a gross leakage or breakdown test, the working voltage (Viorm) or transient overvoltage (Viotm) ratings, as specified by the IEC 60747-5-5, is based on partial discharge testing. As mentioned, SPICE does not simulate insulation breakdown levels or partial discharge inception voltages for optocouplers.

b. Isolation: This refers to the property of optocouplers to reject electrical noise between its two optically isolated grounds. This parameter is generally specified in the optocoupler data sheet as CMR (common-mode rejection). This parameter is quantified as the maximum rate of change of voltage across the two sides that can be tolerated without the optocoupler misbehaving or showing sensitivity or output glitches. Usually this rate of change (dV/dt) specification is indicated in terms of maximum kV/µsec that the optocoupler will tolerate without glitching and remain in its correct logic state. The higher the CMR capability of an optocoupler, the higher is its ability to reject electrical noise between its two isolated sides or grounds. SPICE also does not simulate the isolation or noise rejection properties of optocouplers.

If this is true that SPICE software does not simulate the two primary and fundamental properties and functions of optocouplers, namely insulation and isolation, then why would one reasonably want to use SPICE software to analyze the circuits that incorporate optocouplers models within them? The answer is simple enough: SPICE does successfully simulate many other DC or AC parameters or properties of optocouplers such as:

- 1. Input-output propagation delays

- 2. Current transfer ratios (CTR)

- 3. Transfer gain

- 4. Bandwidth or frequency response

- 5. Power dissipations

Thus, SPICE circuit simulations using optocoupler macro models have many advantages. This certainly means that gaining some insight using these optocoupler macro models is much better than getting no insight at all.

Most SPICE vendors also include model libraries of various electrical components such as:

- 1. Operational amplifiers (opamps)

- 2. Voltage regulators

- 3. Timers

- 4. IGBTs and MOSFETs

The models of components offered by model libraries are almost limitless and too large to enumerate all. These components or their models can be configured in the circuits to be designed or examined. This allows useful circuit simulations and analysis of complex circuits using optocouplers or their macro models and other useful integrated circuits. Thus, the objective of this application note is twofold:

A. Perform circuit simulation using optocoupler SPICE macro-models (that are offered by Avago Technologies), and substantiate their key data sheet performance parameters

B. Perform circuit simulations using optocoupler SPICE macro models in more complex circuits using other integrated circuit device models to predict circuit behavior and performance equivalent to the bread-board and bench test level.

#### Some Advantages and Limitations of Simulation

Simulations, if performed skillfully and with the knowledge of the strengths and limitations of the software employed, can be very useful in gaining insight and predicting behavior of a design concept.

For example, circuit simulations can be used to:

- Test Novel Design Ideas: A designer is only limited by his or her imagination when coming up with novel or innovative ideas to test using circuit simulation software. That is even before a soldering iron is contemplated for breadboard, initial circuit simulations are normally used to debug an initial design idea

- 2. Save Precious Time: No need to spend a week to breadboard a circuit, only to discover that the initial circuit concept has no gain or bandwidth or simply does not perform

- 3. Predict Circuit Performance: Simulations also help to predict how robust a circuit design concept is as temperature or component tolerances vary. Or to determine if the circuit is stable across all operating voltages, frequencies, or temperature.

- 4. Make Useful Current, Voltage, and Power Measurements: Making actual voltage and current and power measurements on a breadboard may be cumbersome if not impossible. The simulation software can perform such measurements in no time at all.

- 5. Limitations of PSpice One needs to realize that the models and software are only as good as the assumptions made in their conceptions. These models are not perfect. Also, there may be some properties of these components that cannot be easily modeled. In addition to the insulation and isolation properties of Optocouplers discussed earlier, other parameters that may not be modeled at all may include latch up sensitivity, power supply sensitivity, breakdown voltages, noise sensitivity, or overshoot, etc.

In addition, SPICE may not predict the various component failure modes. Also, many simulations are based on simplified models that only provide an overall approximate macroscopic response, and may not accurately predict subtle or complex behavior.

Thus, in the final analysis, after a circuit is first theoretically analyzed using the circuit simulation software, only the performance of the actual bread-boarded prototype circuit provides the final verification and peace of mind that the circuit will in fact work as conceived.

### Model Types: Macro models versus Micro models

One can use SPICE to simulate circuits either using the macro models or using the micro models. A micro model analysis is based on the transistor level model of an IC chip. This model is based on the actual processing dependent parameters of all the active and passive devices that compose an IC component or a device. The micro models are the most accurate way to perform SPICE simulations.

A macro model on the other hand, is a less precise way to perform simulations of the devices. The model is conceived and developed to reflect an overall macro response of device as opposed to the device component level analysis of the device. It may not model all the parameters accurately, but may emphasize or highlight only the key and significant overall response. However, a carefully developed macro model may give enough detail and accurate response, that it may be sufficient for most practical simulation purposes. The SPICE simulations attempted in this application note are all based on the optocoupler macro models provided by Avago Technologies.

## HCNR200 or HCNR201 Analog Optocoupler PSpice Circuit Simulations

#### 1. HCNR200 or HCNR201 Transmitter Circuit

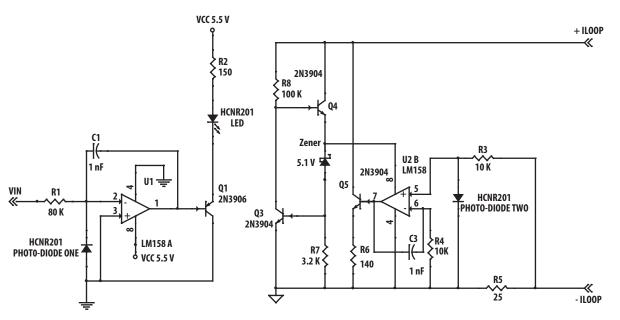

The design equations for the 4 mA to 20 mA HCNR200 based transmitter circuit shown in Figure 1 can be readily derived as follows. The circuit is designed such that when:

$V_{IN} = 0.8 \text{ V}, I_{LOOP} = 4 \text{ mA}$  $V_{IN} = 4.0 \text{ V}, I_{LOOP} = 20 \text{ mA}$

The transfer function design equations are:

$I_{PD1} = V_{IN} / R1$

Thus, when V\_{IN}= 0.8 V, I\_{PD1}= 0.8 V/R1 = 0.8 V/ 80 k  $\Omega$  = 10  $\mu A$

$V_{IN} = 4V$ ,  $I_{PD1} = 4V / R1 = 4V / 80 k\Omega = 50 \mu A$

$V_{IN} = 4 V$ ,  $1_{PD1} = 4 V/R1 = 4 V/80 K\Omega = 50 \mu A$

Design Equations: (ILOOP / VIN) = K3(R5+R3) / (R5 \* R1)

Note: The two OP-AMPS shown are two separate LM158, and NOT two channels in a single DUAL package, otherwise the LOOP side and input side will not be properly Isolated.

Figure 1. HCNR200 or HCNR201 4 mA to 20 mA transmitter circuit

From the HCNR201 data sheet, the typical transfer gain  $K3 = I_{PD2} / I_{PD1} = 1.0$ . The photo-diode IPD2 is formed by the current divider circuit formed by resistors R5 and R3:

$I_{PD2} = I_{LOOP} * (R5 / R5 + R3)$

Since K3 =  $I_{PD2}/I_{PD1} = 1.0$

$I_{PD2} = K3 * I_{PD1}$

But,  $I_{PD1} = V_{IN} / R1$

$I_{PD2} = K3 * (V_{IN} / R1)$

Substituting:

$K3 * (V_{IN}/R1) = I_{LOOP} * (R5 / R5 + R3)$

Solving for ILOOP:

$I_{LOOP} / V_{IN} = K3^* (R5 + R3) / (R5 * R1)$

Since the transfer function, K3, is typically 1 (from the data sheet), this can be simplified to:

$I_{LOOP} / V_{IN} = (R5 + R3) / (R5 * R1)$

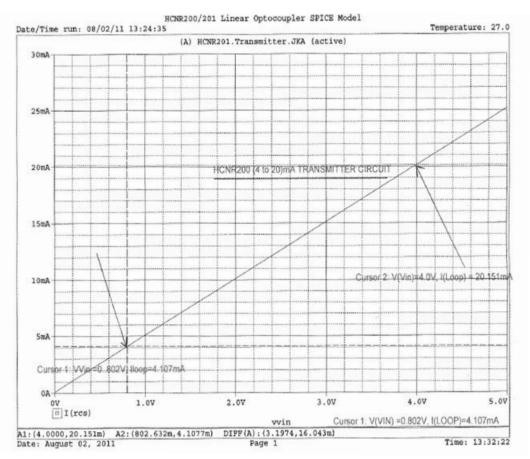

Let us now look at the SPICE simulation results and see what we obtain for the DC transfer function.

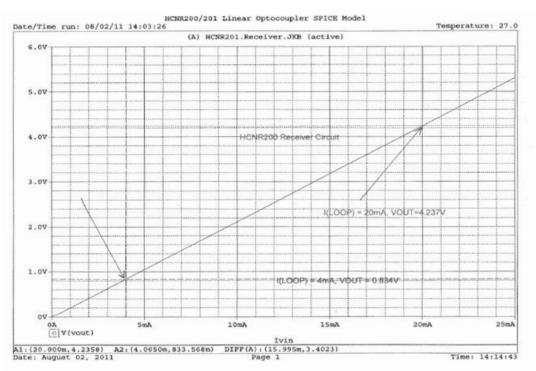

Figure 2. SPICE simulation DC results for a 4 to 20 mA HCNR201/HCNR201transmitter circuit

The SPICE simulations show the following results:

| Parameter                        | Predicted Results | SPICE Results | % Error |

|----------------------------------|-------------------|---------------|---------|

| $I_{LOOP}$ when $V_{IN} = 0.8 V$ | 4 mA              | 4.1 mA        | 2.5%    |

| $I_{LOOP}$ when $V_{IN} = 4 V$   | 20 mA             | 20.15 mA      | 0.75%   |

Designers normally consider that if the SPICE results are within 5% to 10% of the predicted results this means that the circuit SPICE model or macro-model circuit simulations are excellent and represent the actual circuit or device performance exceptionally well.

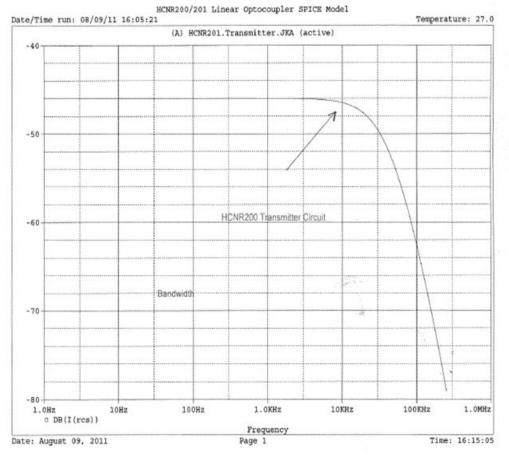

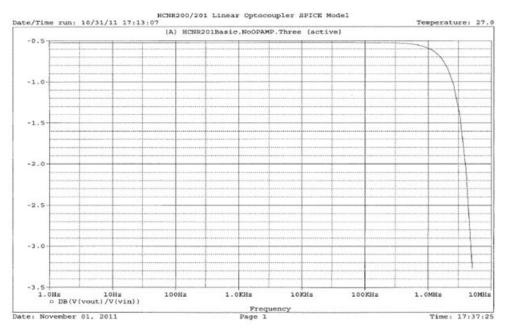

Determining the dynamic or AC response of a circuit requires looking at the input-output frequency response, and the key objective is to establish the output bandwidth and the phase margin of the circuit.

The bandwidth response of the transmitter circuit is shown in Figure 3. The 3 dB bandwidth of the circuit is close to 10 kHz. This agrees quite well with the 10 kHz typical bandwidth specified for opamp based analog circuits indicated in the Avago HCNR200 data sheet.

Figure 3. SPICE simulation of AC bandwidth for the 4 mA to 20 mA transmitter circuit

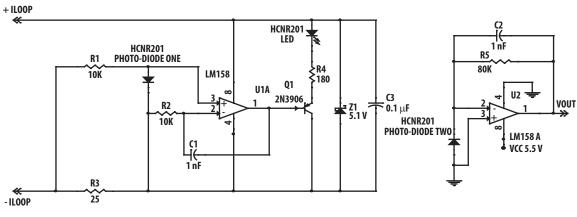

#### 2. HCNR200 or HCNR201 Receiver Circuit

Using SPICE, first establish DC performance for the circuit shown in Figure 4.

Design Equations: Vout/ILOOP = K3 \* (R5 \* R3)/(R3 + R1)

Note: The two OP-AMPS shown are two separate LM158, and NOT two channels in a single DUAL package, otherwise the LOOP side and input side will not be properly Isolated.

#### Figure 4. HCNR200 4 mA to 20 mA current loop receiver

Figure 5. SPICE simulation of DC results for the 4 mA to 20 mA receiver circuit

The transfer function for the receiver circuit can be established by observing the following relationships:

$I_{PD1} = I_{LOOP} * (R3 / (R3 + R1))$ K3 = Transfer Gain =  $I_{PD2} / I_{PD1}$ V<sub>OUT</sub> =  $I_{PD2} * R5$

Solving the above equations leads us to the transfer function:

$I_{PD2} = V_{OUT} / R5$

Since  $I_{PD2} = I_{PD1} * K3$ :

$V_{OUT} / R5 = K3 * I_{LOOP} * (R3 / (R3 + R1) or$

$V_{OUT} / I_{LOOP} = K3 * (R3 * R5) / (R3 + R1)$

The resistor values shown for the receiver circuit of Figure 4 are scaled such that when the loop current is 4 mA the output voltage is 0.8 V. When the loop current is 20 mA the output voltage is 4 V. This assumes that K3 (transfer gain) equals 1, which is typically the case as indicated in the data sheet for the HCNR200.

Checking with the SPICE results of Figure 5, we obtain the following results:

| Parameter                                 | Predicted Results | SPICE Results | % Error |

|-------------------------------------------|-------------------|---------------|---------|

| $V_{OUT}$ when $I_{LOOP} = 4 \text{ mA}$  | 0.8 V             | 0.834 V       | 4.25%   |

| $V_{OUT}$ when $I_{LOOP} = 20 \text{ mA}$ | 4.0 V             | 4.237 V       | 5.93%   |

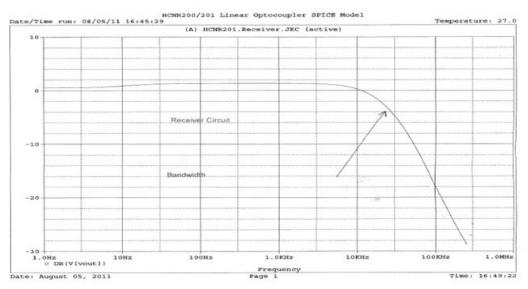

The dynamic or AC response of a circuit requires looking at the input frequency response, and the key objective is to establish the output bandwidth and phase margin of the circuit.

The -3 dB bandwidth of the receiver circuit shown in Figure 6 is close to 10 kHz. This agrees quite well with the 10 kHz typical bandwidth specified for the opamp based analog circuits indicated in the HCNR200 data sheet.

Figure 6. SPICE Simulation of AC bandwidth for the 4 mA to 20 mA receiver circuit

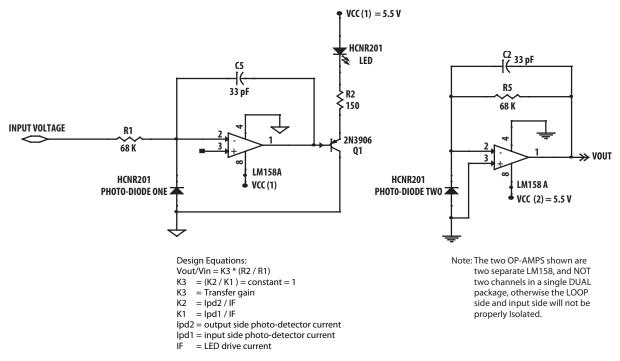

#### 3. HCNR200 or HCNR201 High-Speed Low-Cost Analog Isolator Circuit

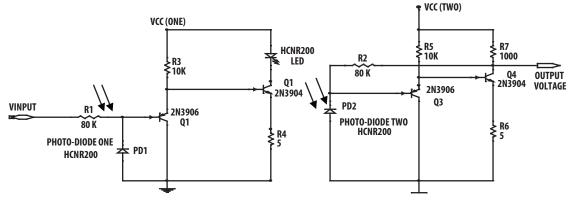

Figure 7. HCNR200 or HCNR201 high-speed low-cost analog isolator

The circuit shown in Figure 7 is a high-speed low-cost circuit designed for use in the feedback path of switch-mode power supplies. This application requires good bandwidth, low cost and stable gain but does not require very high accuracy. This circuit is a good example of how a designer can trade off accuracy to achieve improvements in bandwidth and cost. The circuit has a bandwidth of about 1.5 MHz with stable gain characteristics and requires few external components.

Although it may not appear so at first glance, the circuit in Figure 7 is essentially the same as the circuit in Figure 10. The input side operational amplifier, A1, is comprised of Q1, Q2, R3 and R4. The output side operational amplifier, A2, is comprised of Q3, Q4, R5, R6 and R7. The circuit operates in the same manner as well; the only difference is the performance of amplifiers A1 and A2. The lower gains, higher input currents and higher offset voltages affect the accuracy of the circuit but not the way it operates. Because the basic circuit operation has not changed, the circuit still has good gain stability. The use of discrete transistors instead of operational amplifiers allowed the design to trade off accuracy to achieve good bandwidth and gain stability at low cost.

To get into a little more detail about the circuit, R1 is selected to achieve an LED current of about 7 mA to10 mA at the nominal input operating voltage according to the following equation:

$$I_F = (V_{IN}/R1)/K1$$

K1(i.e.,  $I_{PD1}/I_F$ ) of the optocoupler is typically about 0.5%. R2 is then selected to achieve the desired output voltage according to the equation:

$V_{OUT}/V_{IN} = R2/R1$

The purpose of R4 and R6 is to improve the dynamic response and stability of the input and output circuits by lowering the local loop gains. R3 and R5 are selected to provide enough current to drive the bases of Q2 and Q4. R7 is selected so that Q4 operates at about the same collector current as Q2.

Figure 8. HCNR200/HCNR201 high-speed low-cost analog isolator: uni-polar DC response

Now, let's take a look at the calculated or theoretical response with that predicted by SPICE using the HCNR200 macro model SPICE model for the high-speed low-cost circuit shown in Figure 7:

| Parameter           | Predicted Results | SPICE Results | % Error |

|---------------------|-------------------|---------------|---------|

| Vout at Vin = 1.0 V | 1.0 V             | 0.919 V       | -8.1%   |

| Vout at Vin = 4.0 V | 4.0 V             | 3.75 V        | -6.25%  |

This high-speed low-cost circuit is a good example of how designers can trade-off accuracy to achieve a bandwidth of 1.5 MHz. The SPICE results are still within 10% nominal considered by most designers as fairly good simulation results as compared to the predicted or theoretical result.

The bandwidth for the high-speed low-cost analog isolator is now 1.5 MHz. However, this high bandwidth has been achieved at the cost of lower accuracy.

Figure 9. HCNR200 high-speed low-cost analog isolator: bandwidth response

### 4. HCNR200 or HCNR201 Uni-polar Operational Amplifier based Analog Isolation Circuit

For a higher accuracy uni-polar circuit, we will now consider the operational amplifier based circuit shown in Figure 10.

Figure 10. HCNR200 or HCNR201 uni-polar higher accuracy analog circuit

The two operational amplifiers shown in Figure 10 are two separate LM158 packages and not two channels in a single dual package, otherwise galvanic insulation is not present as the grounds and Vcc are shared between the two operational amplifiers of the dual package. The operational amplifier always tries to maintain the same inputs voltages at its two inputs in a linear feedback close loop connection. Thus, the input side operational amplifier always tries to place zero volts across the photodiode 1, PD1.

When Vin = 0 V, there is no photodiode 1 current,  $I_{PD1}$ , and photodiode 2 current,  $I_{PD2}$ , is also zero. This is because  $I_{PD2} = K3 \times I_{PD1}$ , where the transfer gain K3 is indicated in the data sheet by:

$K3 = I_{PD2}/I_{PD1} = 1$

If some positive polarity voltage is applied at the input, the operational amplifier output would tend to swing to the negative rail (in this case the ground voltage) causing the LED current to flow. The  $I_{PD1}$  is now externally set by  $V_{IN}$  and R1 ( $I_{PD1} = V_{IN}/R1$ ). The operational amplifier will limit the LED current,  $I_{F}$ , to an appropriate value required to establish the externally set  $I_{PD1}$ . The maximum full scale LED current is designed to keep it under the absolute maximum rating of 25 mA. Since the operational amplifier is connected in a stable negative feedback servo loop it also maintains the same voltages across its two inputs, in this case 0 V. The output voltage is just  $I_{PD2} \ge R2$ . Thus, to establish the transfer function following equations can be written:

$I_{PD1} = V_{IN}/R_1$  (input photo-diode current)

K3 =  $I_{PD2}/I_{PD1}$  = 1, where the transfer gain, K3, is indicated in the data sheet

$I_{PD2} = K3 \times I_{PD1}$

$V_{OUT} = I_{PD2} \times R5$

Solving the above equations readily yields the linear transfer function as:

$V_{OUT}/V_{IN} = K3 \times R5/R1$

Typically, the transfer gain, K3 = 1, is 5% accurate for the HCNR201 and 15% for the HCNR200. The input photo gain is represented by the K1 parameter in the data sheet and is defined as  $I_{PD1}/I_F$ . The data sheet for the HCNR201 lists this input current transfer ratio as 0.25% to 0.75% for the HCNR200 and 0.36% to 0.72% for the HCNR201. As indicated in the data sheet, for best linearity the photo-diode current is set between 5 nA to 50  $\mu$ A. This implies that the Vin and R1 combination at the input should constrain the externally set maximum photodetector current at 50  $\mu$ A. However, higher photodetector currents up to 100  $\mu$ A can be easily set at higher LED currents close to 25 mA.

In order to protect the LED such that in a fault condition where the input-side operational amplifier has its output switched all the way to a low state or ground, the resistor R2 should be picked such that the full scale LED current – as set by R2 – does not exceed the absolute maximum LED current of 25 mA, as indicated under the absolute maximum conditions listed in the HCNR200 data sheet.

This full scale LED current under a fault condition is now calculated as:

$I_F$  (full scale) = [ $V_{CC1} - V_F$  (LED) –  $V_{BE}$  (PNP) –  $V_{SAT}$  (opamp) ] / R2

HCNR200 V<sub>F</sub> (typical) = 1.6 V (see data sheet)

$V_{BE}$  (PNP) = 0.6 V

VSAT (op-amp) = 0.2 V (typical)

Assuming, an input side VCC1 = 5.5 V, R2 is calculated as 124  $\Omega$

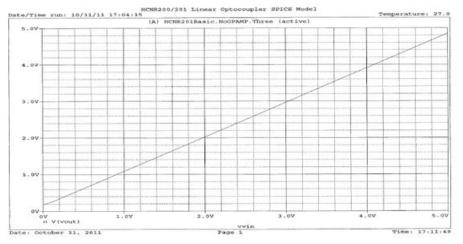

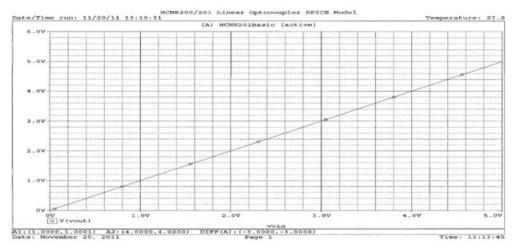

Figure 11. SPICE simulation DC results for the high linearity uni-polar circuit

For the high linearity uni-polar basic circuit with a PNP LED drive current stage shown in Figure 10, SPICE simulation results were:

| Parameter           | Predicted Results | SPICE Results | % Error |

|---------------------|-------------------|---------------|---------|

| Vout at Vin = 1.0 V | 1.0 V             | 1.0 V         | 0%      |

| Vout at Vin = 4.0 V | 4.0 V             | 4.0 V         | 0%      |

These results indicate that the higher accuracy circuit, shown in Figure 10, can be built using the HCNR200 or HCNR201 with linearity results that are excellent. The macro model is able to distinguish between the accuracy results of the low accuracy circuit shown in Figure 7 and the high accuracy circuit shown in Figure 10.

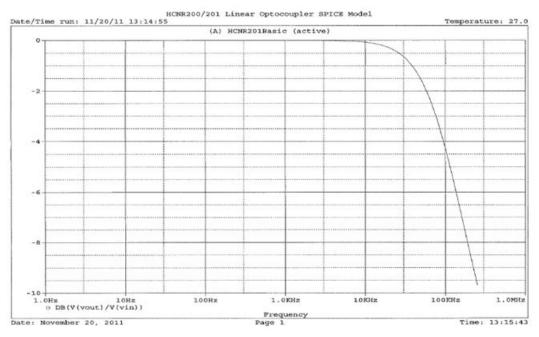

The AC bandwidth results for the higher accuracy circuit of Figure 10 indicates that the higher accuracy obtained by using the servo feedback loop operational amplifiers considerably reduces the 3 dB bandwidth to close to 15 kHz, as identified in the data sheet for the HCNR200.

Figure 12. SPICE simulation of AC bandwidth: high linearity uni-polar circuit (Figure 10)

## 5. HCNR200 or HCNR201 Bi-polar Input Analog Isolation Amplifier Circuit

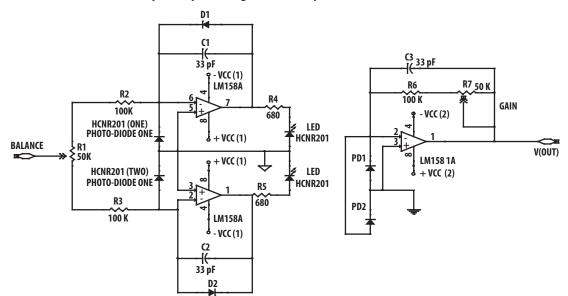

Figure 13. HCNR200 or HCNR20: bi-polar input analog circuit

Using similar concepts as developed for the positive-polarity input voltage analog amplifier discussed before, it is quite straight forward to develop a bipolarity input voltage analog amplifier. Figure 13 shows the bipolar input voltage analog circuit using the HCNR200 or HCNR201 in the servo feedback loop.

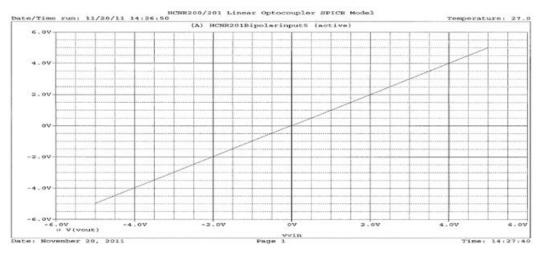

This bipolar input voltage circuit uses two HCNR200 or HCNR201 optocouplers. The top half of the circuit, consisting of PD1, R1, DA, C1, R4 and optocoupler 1 (OC1) LED, is for the positive input voltages. The lower half of the circuit, consisting of optocoupler 2 (OC2) PD1, R2, BB and R5 and optocoupler 2 (OC2) LED, is for the negative input voltages. The diodes D1 and D2 help reduce crossover distortion by keeping both amplifiers active during both positive and negative portions of the input signal. Balance control R1 at the input can be used to adjust the relative gain for the positive and negative input voltages. The gain control R7 can be used to adjust the overall transfer gain of the amplifier. The capacitors C1, C2, and C3 are the compensation capacitors for stability. Figure 14 shows the DC response of the Figure 13 bi-polar input voltage analog circuit. The SPICE simulations show the following performance:

| Parameter            | Predicted Results | SPICE Results | % Error |

|----------------------|-------------------|---------------|---------|

| Vout when Vin = -4 V | -4 V              | -3.974 V      | +0.65%  |

| Vout when Vin = +4 V | +4 V              | +4.003 V      | -0.08%  |

This again indicates that the HCNR200 or HCNR201 macro model accurately predicts the theoretical or calculated behavior of the HCNR200 circuit, when two HCNR200/HCNR201 isolators are configured to deliver bi-polar voltages at the inputs.

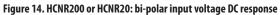

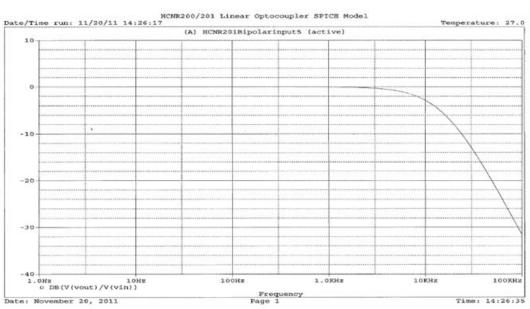

The AC bandwidth response of the bi-polar input voltage circuit shown in Figure 15 indicates, that as previously discussed for the uni-polar input voltage case, these high linearity circuits using operational amplifiers along with the HCNR200 indicate a typical bandwidth better than 10 kHz. This again corroborates the 10 kHz shown as the typical bandwidth in the HCNR200 data sheet.

Figure 15. HCNR200 or HCNR201: bi-polar input AC bandwidth response

# Conclusion

In this application note we have considered SPICE circuit simulations using the HCNR200 or HCNR201 analog optocoupler macro models. The SPICE circuit simulations performed for various circuit configurations using the HCNR200 and HCNR201 analog optocouplers confirm that the SPICE macro models that Avago Technologies supplies are able to successfully demonstrate the key analog optocoupler device parameters, such as the AC or DC response. In other words, the simulations corroborate the performance and capability as specified in the HCNR200 and HCNR201 data sheets.

In addition, these models not only replicate the key device parameters, as indicated in the data sheet, but also faithfully demonstrate and predict the overall circuit performance in relatively complex circuit topologies. Designers can with confidence use the optocoupler SPICE macro models provided by Avago Technologies for their complex circuit simulations and application requirements.

# **Bibliography**

- 1. Paul W. Tuinenga, "SPICE: A Guide to Circuit Simulations and Analysis Using PSpice" Third Edition, Prentice Hall, 1988

- 2. John Keowan, "MicroSim PSpice and Circuit Analysis" Third Edition, Prentice Hall, 1988

- 3. Andre Vladimirescu, "The SPICE Book" John Wiley & Sons, Inc., 1994

- 4. Muhammad H. Rashid and Hasan M. Rashid, "Spice for Power Electronics and Electric Power" CRC Press, Taylor and Francis Group, 2006

- 5. James G. Gottling "Hands On PSpice" Houghton Mifflin Company, 1995

Note: Avago Technologies' optocoupler SPICE macro models are available at: http://www.avagotech.com/ pages/optocouplers\_plastic/spicemodels/

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2012 Avago Technologies. All rights reserved. AV02-3334EN - January 13, 2012