CC3120

SWAS034 - FEBRUARY 2017

# CC3120 SimpleLink™ Wi-Fi® Wireless Network Processor, Internet-of-Things Solution for MCU Applications

# **Device Overview**

#### **Features**

- CC3120R SimpleLink™ Wi-Fi® Consists of a Wireless Network Processor (NWP) and Power-Management Subsystems

- Featuring Wi-Fi Internet-on-a chip™ Dedicated ARM® Cortex®-M3 Microcontroller Unit (MCU) Completely Offloads Wi-Fi and Internet Protocols from the Application MCU

- · Wi-Fi Modes:

- 802.11b/g/n Station

- 802.11b/g Access Point (AP) Supports up to Four Stations

- Wi-Fi Direct<sup>®</sup> Client/Group Owner

- WPA2 Personal and Enterprise Security: WEP, WPA/WPA2 PSK, WPA2 Enterprise (802.1x)

- IPv4 and IPv6 TCP/IP Stack

- Industry-Standard BSD Socket Application Programming Interfaces (APIs)

- 16 Simultaneous TCP or UDP Sockets

- 6 Simultaneous TLS and SSL Sockets

- · IP Addressing: Static IP, LLA, DHCPv4, and DHCPv6 With Duplicate Address Detection (DAD)

- SimpleLink Connection Manager for Autonomous and Fast Wi-Fi Connections

- Flexible Wi-Fi Provisioning With SmartConfig™ Technology, AP Mode, and WPS2 Options

- RESTful API Support Using Internal HTTP Server

- Wide Set of Security Features

- Hardware Features

- Separate Execution Environments

- Device Identity

- Networking security

- Personal and Enterprise Wi-Fi Security

- Secure Sockets (SSLv3, TLS1.0/1.1/TLS1.2)

- HTTPS Server

- Trusted Root-Certificate Catalog

- TI Root-of-Trust Public key

- Software IP protection

- Secure Key Storage

- File System Security

- Software Tamper Detection

- Cloning Protection

- Embedded Network Applications Running on the **Dedicated NWP**

- HTTP/HTTPS Web Server With Dynamic User Callbacks

- mDNS, DNS-SD, DHCP Server

- Recovery Mechanism—Can Recover to Factory Defaults or to a Complete Factory Image

- Wi-Fi TX Power

- 18.0 dBm @ 1 DSSS

- 14.5 dBm @ 54 OFDM

- Wi-Fi RX Sensitivity

- 96.0 dBm @ 1 DSSS

- 74.5 dBm @ 54 OFDM

- Application Throughput

- UDP: 16 Mbps

- TCP: 13 Mbps

- Power-Management Subsystem

- Integrated DC-DC Converters Support a Wide Range of Supply Voltage:

- VBAT Wide-Voltage Mode: 2.1 V to 3.6 V

- VIO is Always Tied With VBAT

- Preregulated 1.85-V Mode

- Advanced Low-Power Modes

- Shutdown: 1 µA

- Hibernate: 4.5 μA

- Low-Power Deep Sleep (LPDS): 115 μA

- RX Traffic: 59 mA @ 54 OFDM

- TX Traffic: 229 mA @ 54 OFDM, Maximum

- Idle Connected (MCU in LPDS): 690 μA @ DTIM = 1

- Clock Source

- 40.0-MHz Crystal With Internal Oscillator

- 32.768-kHz Crystal or External RTC

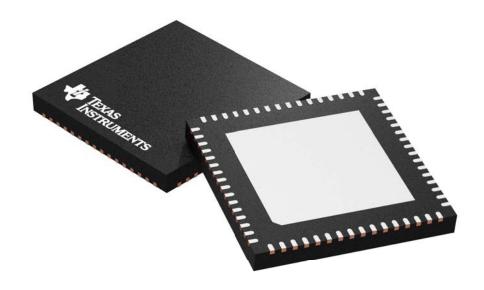

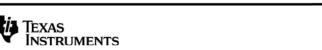

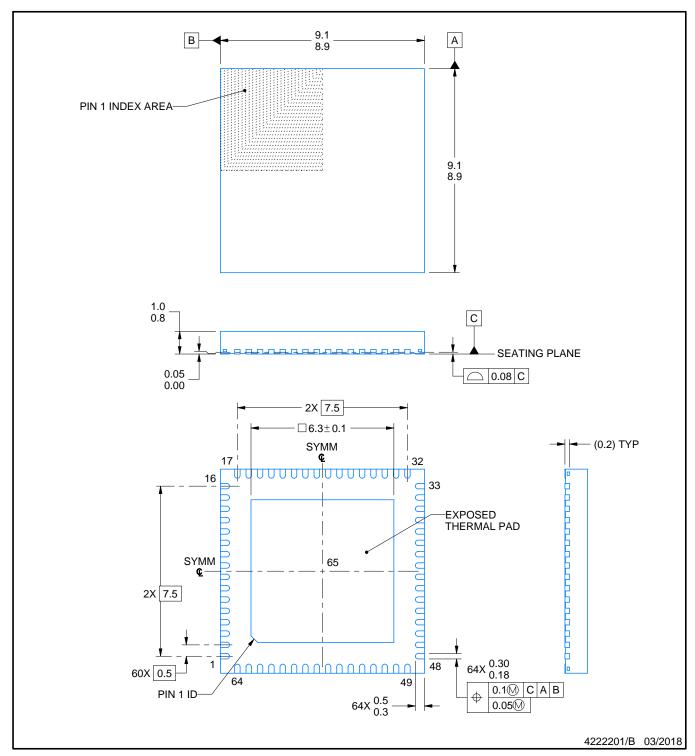

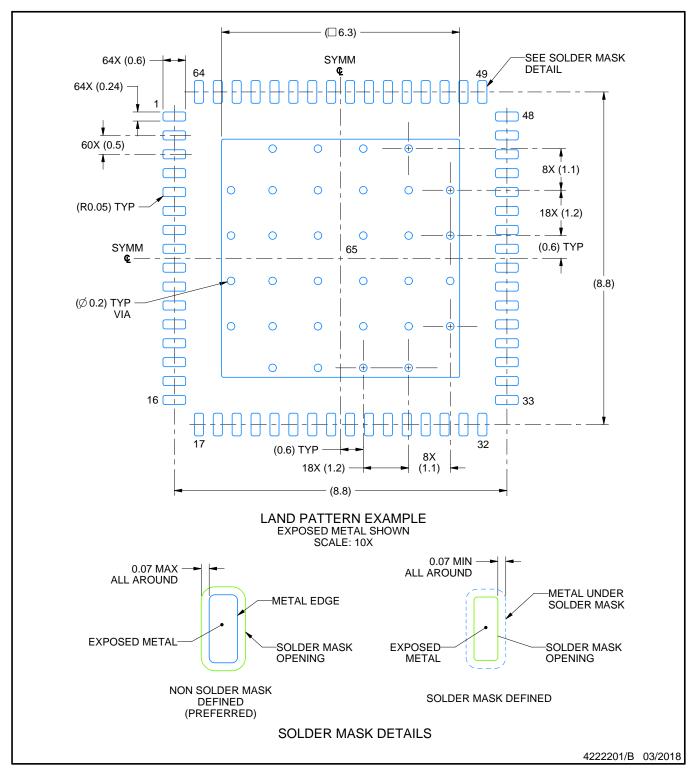

- RGK Package

- 64-Pin, 9-mm x 9-mm Very Thin Quad Flat Nonleaded (VQFN) Package, 0.5-mm Pitch

- · Operating Temperature

- Ambient Temperature Range: –40°C to +85°C

- **Device Supports SimpleLink Developers Ecosystem**

# TEXAS INSTRUMENTS

#### 1.2 Applications

- For Internet-of-Things (IoT) applications, such as:

- Cloud Connectivity

- Internet Gateway

- Home and Building Automation

- Appliances

- Access Control

- Security Systems

- Smart Energy

- Industrial Control

- Smart Plug and Metering

- Wireless Audio

- IP Network Sensor Nodes

- Asset Tracking

- Medical Devices

# 1.3 Description

The CC3120R device is part of the SimpleLink™ microcontroller (MCU) platform which consists of Wi-Fi, Bluetooth® low energy, Sub-1 GHz and host MCUs, which all share a common, easy-to-use development environment with a single core software development kit (SDK) and rich tool set. A one-time integration of the SimpleLink platform enables you to add any combination of the portfolio's devices into your design, allowing 100 percent code reuse when your design requirements change. For more information, visit Overview for SimpleLink™ solutions.

Connect any microcontroller (MCU) to the Internet of Things (IoT) cloud with the CC3120R device from Texas Instruments<sup>™</sup>. The Wi-Fi<sup>®</sup> Alliance CERTIFIED<sup>®</sup> CC3120R device is part of the second generation of the SimpleLink<sup>™</sup> Wi-Fi family that dramatically simplifies the implementation of low-power Internet connectivity.

The CC3120R has all of the Wi-Fi and Internet protocols implemented in the ROM, which runs from the dedicated on-chip ARM<sup>®</sup> network processor and significantly offloads the host MCU and simplifies the system integration.

The CC3120R Wi-Fi Internet-on-a chip™ device contains a dedicated ARM MCU that offloads many of the networking activities from the host MCU. This subsystem includes an 802.11b/g/n radio, baseband, and MAC with a powerful crypto engine for fast, secure Internet connections with 256-bit encryption. The CC3120R device supports station, AP, and Wi-Fi direct modes. The device also supports WPA2 personal and enterprise security. The device includes embedded TCP/IP and TLS/SSL stacks, an HTTP server, and multiple Internet protocols. The CC3120R device supports a variety of Wi-Fi provisioning methods, including HTTP based on AP mode, SmartConfig™ technology, and WPS2.0.

As part of TI's SimpleLink Wi-Fi family second generation, the CC3120R device introduces the new features and enhanced capabilities, such as the following:

IPv6

Enhanced Wi-Fi provisioning

Enhanced power consumption

Wi-Fi AP connection with up to four stations

More concurrently opened BSD sockets; up to 16 BSD sockets, of which 6 are secure

HTTPS support

RESTful API support

Asymmetric keys crypto library

The CC3120R device is delivered with a slim and user-friendly host driver to simplify the integration and development of networking applications. The host driver can easily be ported to most platforms and operating systems (OS). The driver is written in strict ANSI-C (C89) and requires minimal platform adaptation layer (porting layer). The driver has a small memory footprint and can run on 8-, 16-, or 32-bit microcontrollers with any clock speed (no performance or real-time dependency).

The CC3120R device comes in an easy-to-layout VQFN package and is delivered as a complete platform solution, including various tools and software, sample applications, user and programming guides,

reference designs, and the TI E2E™ support community. The CC3120R device is part of the SimpleLink MCU Ecosystem.

# Device Information<sup>(1)</sup>

| PART NUMBER      | PACKAGE   | BODY SIZE         |

|------------------|-----------|-------------------|

| CC3120RNMARGKT/R | VQFN (64) | 9.00 mm × 9.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# 1.4 Functional Block Diagrams

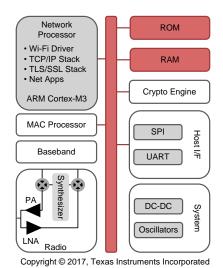

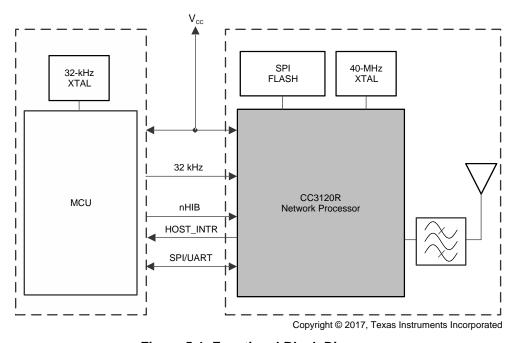

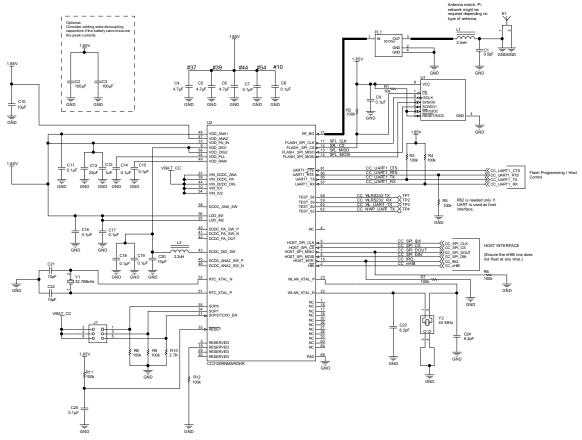

Figure 1-1 shows the CC3120R hardware overview.

Figure 1-1. CC3120R Hardware Overview

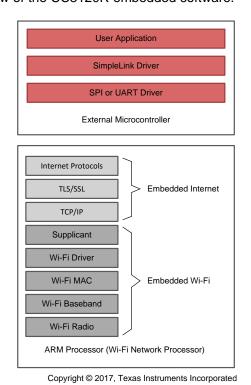

Figure 1-2 shows an overview of the CC3120R embedded software.

Figure 1-2. CC3120R Software Overview

**ISTRUMENTS**

# **Table of Contents**

| 1 | Devi | ce Overview <u>1</u>                        |   | 4.13 | Timing and Switching Characteristics    | . 18           |

|---|------|---------------------------------------------|---|------|-----------------------------------------|----------------|

|   | 1.1  | Features 1                                  |   | 4.14 | External Interfaces                     | 26             |

|   | 1.2  | Applications 2                              |   | 4.15 | Host UART                               | . 28           |

|   | 1.3  | Description                                 | 5 | Deta | illed Description                       | 30             |

|   | 1.4  | Functional Block Diagrams 4                 |   | 5.1  | Overview                                | 30             |

| 2 | Revi | sion History <u>5</u>                       |   | 5.2  | Functional Block Diagram                | 30             |

| 3 | Term | ninal Configuration and Functions           |   | 5.3  | Device Features                         | 31             |

|   | 3.1  | Pin Diagram 6                               |   | 5.4  | Power-Management Subsystem              | 36             |

|   | 3.2  | Pin Attributes                              |   | 5.5  | Low-Power Operating Modes               | 37             |

|   | 3.3  | Connections for Unused Pins 9               |   | 5.6  | Memory                                  | 38             |

| 4 | Spec | cifications <u>10</u>                       |   | 5.7  | Restoring Factory Default Configuration | 39             |

|   | 4.1  | Absolute Maximum Ratings 10                 | 6 | Appl | lications, Implementation, and Layout   | 40             |

|   | 4.2  | ESD Ratings <u>10</u>                       |   | 6.1  | Application Information                 | 40             |

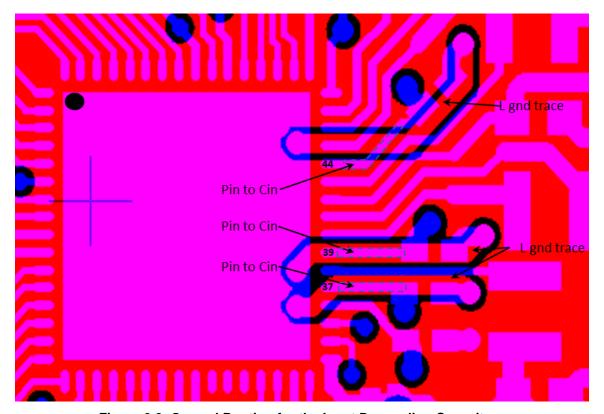

|   | 4.3  | Power-On Hours                              |   | 6.2  | PCB Layout Guidelines                   | 45             |

|   | 4.4  | Recommended Operating Conditions 10         | 7 | Devi | ce and Documentation Support            | 48             |

|   | 4.5  | Current Consumption Summary 11              |   | 7.1  | Tools and Software                      | 48             |

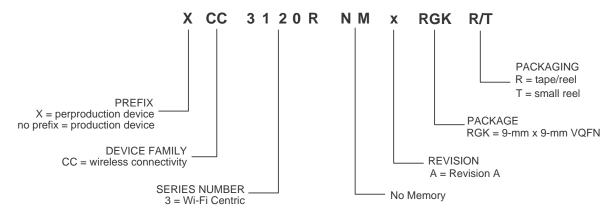

|   | 4.6  | TX Power and IBAT versus TX Power Level     |   | 7.2  | Device Nomenclature                     | 49             |

|   |      | Settings                                    |   | 7.3  | Documentation Support                   | 49             |

|   | 4.7  | Brownout and Blackout Conditions 14         |   | 7.4  | Community Resources                     | 50             |

|   | 4.8  | Electrical Characteristics (3.3 V, 25°C) 15 |   | 7.5  | Trademarks                              | 5 <sup>1</sup> |

|   | 4.9  | WLAN Receiver Characteristics <u>16</u>     |   | 7.6  | Electrostatic Discharge Caution         | 5 <sup>1</sup> |

|   | 4.10 | WLAN Transmitter Characteristics <u>16</u>  |   | 7.7  | Export Control Notice                   |                |

|   | 4.11 | WLAN Filter Requirements                    |   | 7.8  | Glossary                                |                |

|   | 4.12 | Thermal Resistance Characteristics for RGK  | 8 | Mec  | hanical, Packaging, and Orderable       | _              |

|   |      | Package <u>17</u>                           |   |      | mation                                  | 52             |

# 2 Revision History

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| February 2017 | SWAS034* | Initial Release |

# 3 Terminal Configuration and Functions

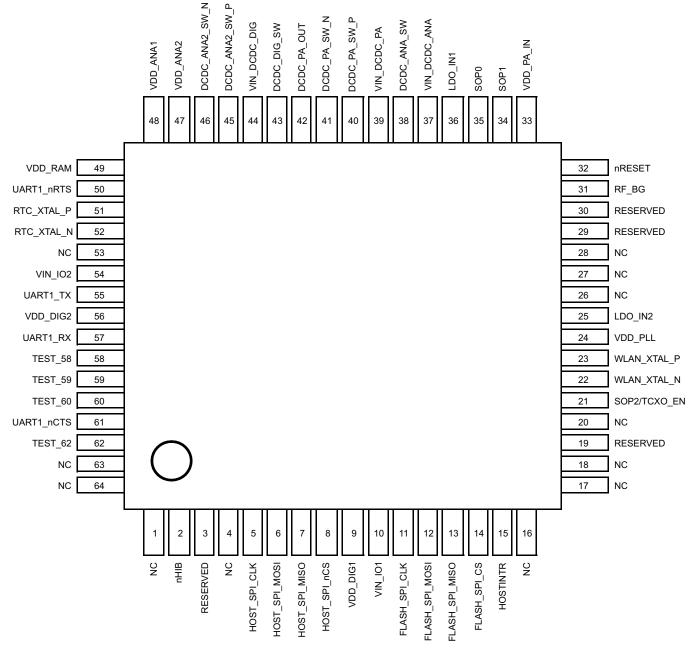

# 3.1 Pin Diagram

Figure 3-1 shows pin assignments for the 64-pin VQFN package.

Figure 3-1. VQFN 64-Pin Assignments Top View

# 3.2 Pin Attributes

Table 3-1 describes the CC3120R pins.

#### **NOTE**

If an external device drives a positive voltage to signal pads when the CC3120R device is not powered, DC current is drawn from the other device. If the drive strength of the external device is adequate, an unintentional wakeup and boot of the CC3120R device can occur. To prevent current draw, TI recommends one of the following:

- All devices interfaced to the CC3120R device must be powered from the same power rail as the CC3120R device.

- Use level shifters between the CC3120R device and any external devices fed from other independent rails.

- The nRESET pin of the CC3120R device must be held low until the VBAT supply to the device is driven and stable.

Table 3-1. Pin Attributes

| PIN | DEFAULT FUNCTION | STATE AT RESET<br>AND HIBERNATE | I/O TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                       |

|-----|------------------|---------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | nHIB             | Hi-Z                            | ı                       | Hibernate signal input to the NWP subsystem (active low). This is connected to the MCU GPIO. If the GPIO from the MCU can float while the MCU enters low power, consider adding a pullup resistor on the board to avoid floating. |

| 3   | Reserved         | Hi-Z                            | _                       | Reserved for future use                                                                                                                                                                                                           |

| 5   | HOST_SPI_CLK     | Hi-Z                            | 1                       | Host interface SPI clock                                                                                                                                                                                                          |

| 6   | HOST_SPI_MOSI    | Hi-Z                            | 1                       | Host interface SPI data input                                                                                                                                                                                                     |

| 7   | HOST_SPI_MISO    | Hi-Z                            | 0                       | Host interface SPI data output                                                                                                                                                                                                    |

| 8   | HOST_SPI_nCS     | Hi-Z                            | 1                       | Host interface SPI chip select (active low)                                                                                                                                                                                       |

| 9   | VDD_DIG1         | Hi-Z                            | Power                   | Digital core supply (1.2 V)                                                                                                                                                                                                       |

| 10  | VIN_IO1          | Hi-Z                            | Power                   | I/O supply                                                                                                                                                                                                                        |

| 11  | FLASH_SPI_CLK    | Hi-Z                            | 0                       | Serial flash interface: SPI clock                                                                                                                                                                                                 |

| 12  | FLASH_SPI_MOSI   | Hi-Z                            | 0                       | Serial flash interface: SPI data out                                                                                                                                                                                              |

| 13  | FLASH _SPI_MISO  | Hi-Z                            | I                       | Serial flash interface: SPI data in (active high)                                                                                                                                                                                 |

| 14  | FLASH _SPI_CS    | Hi-Z                            | 0                       | Serial flash interface: SPI chip select (active low)                                                                                                                                                                              |

| 15  | HOST_INTR        | Hi-Z                            | 0                       | Interrupt output (active high)                                                                                                                                                                                                    |

| 19  | Reserved         | Hi-Z                            | _                       | Connect a 100-k $\Omega$ pulldown resistor to ground.                                                                                                                                                                             |

| 21  | SOP2/TCXO_EN     | Hi-Z                            | 0                       | Controls restore to default mode. Enable signal for external TCXO. Add a 10-k $\Omega$ pulldown resistor to ground.                                                                                                               |

| 22  | WLAN_XTAL_N      | Hi-Z                            | Analog                  | Connect the WLAN 40-MHz XTAL here.                                                                                                                                                                                                |

| 23  | WLAN_XTAL_P      | Hi-Z                            | Analog                  | Connect the WLAN 40-MHz XTAL here.                                                                                                                                                                                                |

| 24  | VDD_PLL          | Hi-Z                            | Power                   | Internal PLL power supply (1.4 V nominal)                                                                                                                                                                                         |

| 25  | LDO_IN2          | Hi-Z                            | Power                   | Input to internal LDO                                                                                                                                                                                                             |

| 29  | Decembed         | Hi-Z                            |                         | Decembed for future use                                                                                                                                                                                                           |

| 30  | Reserved         | ΠΙ-Δ                            | 0                       | Reserved for future use                                                                                                                                                                                                           |

| 31  | RF_BG            | Hi-Z                            | RF                      | 2.4-GHz RF TX, RX                                                                                                                                                                                                                 |

| 32  | nRESET           | Hi-Z                            | I                       | RESET input for the device. Active low input. Use RC circuit (100 k $\parallel$ 0.1 $\mu$ F) for power on reset (POR).                                                                                                            |

<sup>(1)</sup> I = Input

O = Output RF = radio frequency

I/O = bidirectional

# Table 3-1. Pin Attributes (continued)

| PIN | DEFAULT FUNCTION | STATE AT RESET<br>AND HIBERNATE | I/O TYPE <sup>(1)</sup> | DESCRIPTION                                                                                        |

|-----|------------------|---------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|

| 33  | VDD_PA_IN        | Hi-Z                            | Power                   | Power supply for the RF power amplifier (PA)                                                       |

| 34  | SOP1             | Hi-Z                            | _                       | Controls restore to default mode. Add 100-kΩ pulldown to ground. Factory default function.         |

| 35  | SOP0             | Hi-Z                            | -                       | Controls restore to default mode. Add 100-k $\Omega$ pulldown to ground. Factory default function. |

| 36  | LDO_IN1          | Hi-Z                            | Power                   | Input to internal LDO                                                                              |

| 37  | VIN_DCDC_ANA     | Hi-Z                            | Power                   | Power supply for the DC-DC converter for analog section                                            |

| 38  | DCDC_ANA_SW      | Hi-Z                            | Power                   | Analog DC-DC converter switch output                                                               |

| 39  | VIN_DCDC_PA      | Hi-Z                            | Power                   | PA DC-DC converter input supply                                                                    |

| 40  | DCDC_PA_SW_P     | Hi-Z                            | Power                   | PA DC-DC converter switch output +ve                                                               |

| 41  | DCDC_PA_SW_N     | Hi-Z                            | Power                   | PA DC-DC converter switch output -ve                                                               |

| 42  | DCDC_PA_OUT      | Hi-Z                            | Power                   | PA DC-DC converter output. Connect the output capacitor for DC-DC here.                            |

| 43  | DCDC_DIG_SW      | Hi-Z                            | Power                   | Digital DC-DC converter switch output                                                              |

| 44  | VIN_DCDC_DIG     | Hi-Z                            | Power                   | Power supply input for the digital DC-DC converter                                                 |

| 45  | DCDC_ANA2_SW_P   | Hi-Z                            | Power                   | Analog2 DC-DC converter switch output +ve                                                          |

| 46  | DCDC_ANA2_SW_N   | Hi-Z                            | Power                   | Analog2 DC-DC converter switch output -ve                                                          |

| 47  | VDD_ANA2         | Hi-Z                            | Power                   | Analog2 power supply input                                                                         |

| 48  | VDD_ANA1         | Hi-Z                            | Power                   | Analog1 power supply input                                                                         |

| 49  | VDD_RAM          | Hi-Z                            | Power                   | Power supply for the internal RAM                                                                  |

| 50  | UART1_nRTS       | Hi-Z                            | 0                       | UART host interface (active low)                                                                   |

| 51  | RTC_XTAL_P       | Hi-Z                            | Analog                  | 32.768-kHz XTAL_P or external CMOS level clock input                                               |

| 52  | RTC_XTAL_N       | Hi-Z                            | Analog                  | 32.768-kHz XTAL_N or 100-kΩ external pullup for external clock                                     |

| 54  | VIN_IO2          | Hi-Z                            | Power                   | I/O power supply. Same as battery voltage.                                                         |

| 55  | UART1_TX         | Hi-Z                            | 0                       | UART host interface. Connect to test point on prototype for flash programming.                     |

| 56  | VDD_DIG2         | Hi-Z                            | Power                   | Digital power supply (1.2 V)                                                                       |

| 57  | UART1_RX         | Hi-Z                            | I                       | UART host interface; connect to test point on prototype for flash programming.                     |

| 58  | TEST_58          |                                 | -                       | Test signal; connect to an external test point.                                                    |

| 59  | TEST_59          |                                 | _                       | Test signal; connect to an external test point.                                                    |

| 60  | TEST_60          | Hi-Z                            | 0                       | Test signal; connect to an external test point.                                                    |

| 61  | UART1_nCTS       | Hi-Z                            | I                       | UART host interface (active low)                                                                   |

| 62  | TEST_62          | Hi-Z                            | 0                       | Test signal; connect to an external test point.                                                    |

| 65  | GND              |                                 | Power                   | Ground tab used as thermal and electrical ground                                                   |

#### **Connections for Unused Pins** 3.3

All unused pins must be left as no connect (NC) pins. Table 3-2 provides a list of NC pins.

**Table 3-2. Connections for Unused Pins**

| PIN | DEFAULT FUNCTION | STATE AT RESET<br>AND HIBERNATE | I/O TYPE <sup>(1)</sup> | DESCRIPTION                |

|-----|------------------|---------------------------------|-------------------------|----------------------------|

| 1   | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 4   | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 16  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 17  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 18  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 20  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 26  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 27  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 28  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 26  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 27  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 28  | NC               | WLAN analog                     | -                       | Unused; leave unconnected. |

| 53  | NC               | WLAN analog                     | _                       | Unused; leave unconnected. |

| 63  | NC               | WLAN analog                     | _                       | Unused; leave unconnected. |

| 64  | NC               | WLAN analog                     | _                       | Unused; leave unconnected. |

I = Input O = Output RF = radio frequency I/O = bidirectional

# **Specifications**

All measurements are referenced at the device pins, unless otherwise indicated. All specifications are over process and voltage, unless otherwise indicated.

#### 4.1 **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)

| 3 1                                   |                      |             |                       |      |

|---------------------------------------|----------------------|-------------|-----------------------|------|

|                                       |                      | MIN         | MAX                   | UNIT |

| VBAT and VIO                          | Pins: 37, 39, 44     | -0.5        | 3.8                   | V    |

| VIO - VBAT (differential)             | Pins: 10, 54         |             | 0.0                   | V    |

| Digital inputs                        |                      | -0.5        | V <sub>IO</sub> + 0.5 | V    |

| RF pins                               |                      | -0.5        | 2.1                   | V    |

| Analog pins, XTAL                     | Pins: 22, 23, 51, 52 | -0.5        | 2.1                   | V    |

| Operating temperature, T <sub>A</sub> |                      | -40         | 85                    | °C   |

| Storage temperature, T <sub>stq</sub> |                      | <b>–</b> 55 | 125                   | °C   |

#### **ESD Ratings** 4.2

|                  |                         |                                                                                | VALUE | UNIT |

|------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| .,               | Flactrootatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | \/   |

| V <sub>ESD</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### Power-On Hours

#### NOTE

This information is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI semiconductor products.

| CONDITIONS                               | РОН    |

|------------------------------------------|--------|

| T <sub>A</sub> up to 85°C <sup>(1)</sup> | 87,600 |

The TX duty cycle (power amplifier ON time) is assumed to be 10% of the device POH. Of the remaining 90% of the time, the device can be in any other state.

#### 4.4 **Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                      | <b>U</b> (        | ,                                     |         |     |     |           |

|----------------------|-------------------|---------------------------------------|---------|-----|-----|-----------|

|                      |                   |                                       | MIN     | TYP | MAX | UNIT      |

| VBAT, VIO            | Pins: 10, 37, 39, | Direct battery connection (3)         | 2.1 (4) | 3.3 | 3.6 | \/        |

| (shorted to VBAT)    | 44, 54            | Preregulated 1.85 V <sup>(5)(6)</sup> |         |     |     | V         |

| Ambient thermal slew |                   |                                       | -20     |     | 20  | °C/minute |

Operating temperature is limited by crystal frequency variation.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

When operating at an ambient temperature of over 75°C, the transmit duty cycle must remain below 50% to avoid the auto-protect feature of the power amplifier. If the auto-protect feature triggers, the device takes a maximum of 60 seconds to restart the transmission.

To ensure WLAN performance, ripple on the 2.1- to 3.3-V supply must be less than ±300 mV.

The minimum voltage specified includes the ripple on the supply voltage and all other transient dips. The brownout condition is also 2.1 V, and care must be taken when operating at the minimum specified voltage.

To ensure WLAN performance, ripple on the 1.85-V supply must be less than 2% (±40 mV).

<sup>(6)</sup> TI recommends keeping VBAT above 1.85 V. For lower voltages, use a boost converter.

# 4.5 Current Consumption Summary

$T_A = 25^{\circ}C, V_{BAT} = 3.6 V$

| PARAMETER                                  | TE            | ST CONDITIONS <sup>(1)</sup> (2) | MIN TY | P MAX | UNIT |

|--------------------------------------------|---------------|----------------------------------|--------|-------|------|

|                                            | 4 DCCC        | TX power level = 0               | 27:    | 2     |      |

|                                            | 1 DSSS        | TX power level = 4               | 188    | 3     |      |

| TV                                         | COEDM         | TX power level = 0               | 24     | 3     | A    |

| TX                                         | 6 OFDM        | TX power level = 4               | 179    | 9     | mA   |

|                                            | E4 OFDM       | TX power level = 0               | 223    | 3     |      |

|                                            | 54 OFDM       | TX power level = 4               | 160    | )     |      |

| RX <sup>(3)</sup>                          | 1 DSSS        |                                  | 55     | 3     | A    |

| KX <sup>(-)</sup>                          | 54 OFDM       |                                  | 55     | 3     | mA   |

| Idle connected <sup>(4)</sup>              |               |                                  | 69     | )     |      |

| LPDS                                       |               |                                  | 11:    | 5     | μA   |

| Hibernate <sup>(5)</sup>                   |               |                                  |        | 4     |      |

| Peak calibration current <sup>(6)(3)</sup> | VBAT = 3.3 V  |                                  | 450    | )     |      |

|                                            | VBAT = 2.1 V  |                                  | 679    | )     | mA   |

|                                            | VBAT = 1.85 V |                                  | 70     | )     |      |

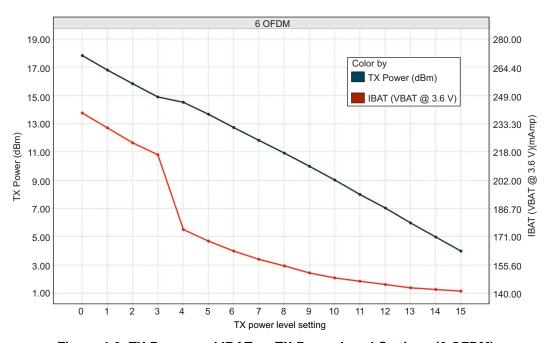

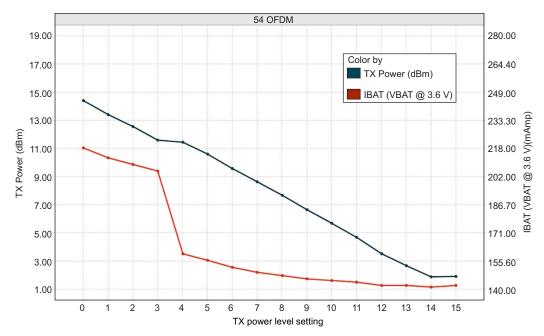

<sup>(1)</sup> TX power level = 0 implies maximum power (see Figure 4-1, Figure 4-2, and Figure 4-3). TX power level = 4 implies output power backed off approximately 4 dB.

<sup>(2)</sup> The CC3120R system is a constant power-source system. The active current numbers scale based on the VBAT voltage supplied.

<sup>(3)</sup> The RX current is measured with a 1-Mbps throughput rate.

<sup>(4)</sup> DTIM = 1

<sup>(5)</sup> For the 1.85-V mode, the hibernate current is higher by 50 μA across all operating modes because of leakage into the PA and analog power inputs.

<sup>(6)</sup> The complete calibration can take up to 17 mJ of energy from the battery over a time of 24 ms. In default mode, calibration is performed sparingly, and typically occurs when re-enabling the NWP and when the temperature has changed by more than 20°C. There are two additional calibration modes that may be used to reduced or completely eliminate the calibration event. For further details, see CC3120, CC3220 SimpleLink™ Wi-Fi® and IoT Network Processor Programmer's Guide.

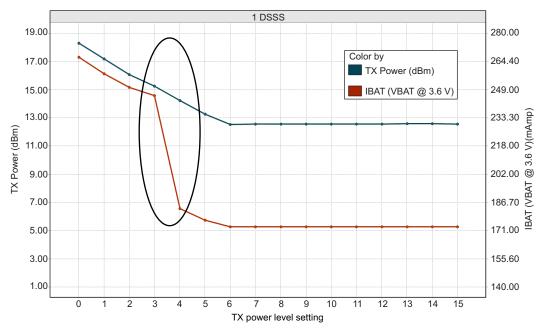

# 4.6 TX Power and IBAT versus TX Power Level Settings

Figure 4-1, Figure 4-2, and Figure 4-3 show TX Power and IBAT versus TX power level settings for modulations of 1 DSSS, 6 OFDM, and 54 OFDM, respectively.

In Figure 4-1, the area enclosed in the circle represents a significant reduction in current during transition from TX power level 3 to level 4. In the case of lower range requirements (14-dBm output power), TI recommends using TX power level 4 to reduce the current.

Figure 4-1. TX Power and IBAT vs TX Power Level Settings (1 DSSS)

Figure 4-2. TX Power and IBAT vs TX Power Level Settings (6 OFDM)

Figure 4-3. TX Power and IBAT vs TX Power Level Settings (54 OFDM)

# TEXAS INSTRUMENTS

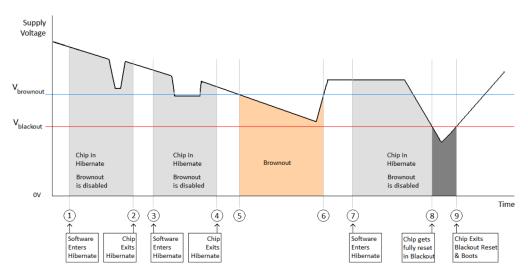

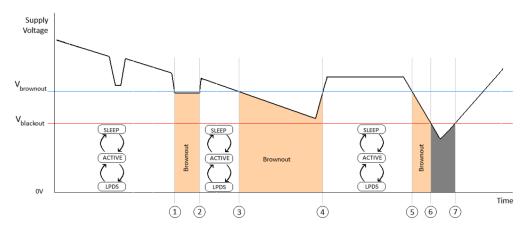

## 4.7 Brownout and Blackout Conditions

The device enters a brownout condition when the input voltage drops below  $V_{brownout}$  (see Figure 4-4 and Figure 4-5). This condition must be considered during design of the power supply routing, especially when operating from a battery. High-current operations, such as a TX packet or any external activity (not necessarily related directly to networking) can cause a drop in the supply voltage, potentially triggering a brownout condition. The resistance includes the internal resistance of the battery, the contact resistance of the battery holder (four contacts for 2x AA batteries), and the wiring and PCB routing resistance.

#### **NOTE**

When the device is in HIBERNATE state, brownout is not detected. Only blackout is in effect during HIBERNATE state.

Figure 4-4. Brownout and Blackout Levels (1 of 2)

Figure 4-5. Brownout and Blackout Levels (2 of 2)

In the brownout condition, all sections of the device (including the 32-kHz RTC) shut down except for the Hibernate module, which remains on. The current in this state can reach approximately 400  $\mu$ A. The

blackout condition is equivalent to a hardware reset event in which all states within the device are lost.

Table 4-1 lists the brownout and blackout voltage levels.

Table 4-1. Brownout and Blackout Voltage Levels

| CONDITION             | VOLTAGE LEVEL | UNIT |

|-----------------------|---------------|------|

| V <sub>brownout</sub> | 2.1           | V    |

| V <sub>blackout</sub> | 1.67          | V    |

# 4.8 Electrical Characteristics (3.3 V, 25°C)

| GI IO           | Pins Except 29,       |            | 1 53 (25 C)                                                                                               |                              |     |                              |      |

|-----------------|-----------------------|------------|-----------------------------------------------------------------------------------------------------------|------------------------------|-----|------------------------------|------|

|                 | PARAMET               | ER         | TEST CONDITIONS                                                                                           | MIN                          | NOM | MAX                          | UNIT |

| $C_{IN}$        | Pin capacitance       | )          |                                                                                                           |                              | 4   |                              | pF   |

| $V_{IH}$        | High-level input      | voltage    |                                                                                                           | $0.65 \times V_{DD}$         |     | $V_{DD} + 0.5 V$             | V    |

| $V_{IL}$        | Low-level input       | voltage    |                                                                                                           | -0.5                         |     | $0.35 \times V_{DD}$         | V    |

| I <sub>IH</sub> | High-level input      | current    |                                                                                                           |                              | 5   |                              | nA   |

| I <sub>IL</sub> | Low-level input       | current    |                                                                                                           |                              | 5   |                              | nA   |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>$2.4 \text{ V} \leq \text{V}_{DD} < 3.6 \text{ V}$ |                              |     | V <sub>DD</sub> × 0.8        |      |

| V <sub>ОН</sub> |                       |            | IL = 4 mA; configured I/O drive strength = 4 mA;<br>2.4 V $\leq$ V <sub>DD</sub> $<$ 3.6 V                |                              |     | V <sub>DD</sub> × 0.7        |      |

|                 | High-level outpo      | ut voltage | IL = 8 mA; configured I/O drive<br>strength = 8 mA;<br>$2.4 \text{ V} \le \text{V}_{DD} < 3.6 \text{ V}$  |                              |     | V <sub>DD</sub> × 0.7        | V    |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>$2.1 \text{ V} \leq \text{V}_{DD} < 2.4 \text{ V}$ |                              |     | V <sub>DD</sub> × 0.75       |      |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>V <sub>DD</sub> = 1.85 V                           |                              |     | V <sub>DD</sub> <b>×</b> 0.7 |      |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>$2.4 \text{ V} \le \text{V}_{DD} < 3.6 \text{ V}$  | V <sub>DD</sub> <b>×</b> 0.2 |     |                              |      |

|                 |                       |            | IL = 4 mA; configured I/O drive<br>strength = 4 mA;<br>$2.4 \text{ V} \le \text{V}_{DD} < 3.6 \text{ V}$  | V <sub>DD</sub> <b>×</b> 0.2 |     |                              |      |

| V <sub>OL</sub> | Low-level outpu       | ıt voltage | IL = 8 mA; configured I/O drive<br>strength = 8 mA;<br>$2.4 \text{ V} \leq \text{V}_{DD} < 3.6 \text{ V}$ | V <sub>DD</sub> × 0.2        |     |                              | V    |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>$2.1 \text{ V} \le \text{V}_{DD} < 2.4 \text{ V}$  | V <sub>DD</sub> × 0.25       |     |                              |      |

|                 |                       |            | IL = 2 mA; configured I/O drive<br>strength = 2 mA;<br>V <sub>DD</sub> = 1.85 V                           | V <sub>DD</sub> × 0.35       |     |                              |      |

|                 | High-level            | 2-mA drive |                                                                                                           | 2                            |     |                              |      |

| ОН              | source                | 4-mA drive |                                                                                                           | 4                            |     |                              | mA   |

|                 | current,              | 6-mA drive |                                                                                                           | 6                            |     |                              |      |

|                 |                       | 2-mA drive |                                                                                                           | 2                            |     |                              |      |

| $I_{OL}$        | Low-level sink        | 4-mA drive |                                                                                                           | 4                            |     |                              | mA   |

|                 | current,              | 6-mA drive |                                                                                                           | 6                            |     |                              |      |

| V <sub>IL</sub> | nRESET <sup>(1)</sup> |            |                                                                                                           | 0.6                          |     |                              | V    |

<sup>(1)</sup> The nRESET pin must be held below 0.6 V for the device to register a reset.

## 4.9 WLAN Receiver Characteristics

$T_A = 25$ °C, VBAT = 2.1 V to 3.6 V. Parameters are measured at the SoC pin on channel 6 (2437 MHz).

| PARAMETER                                                                  | TEST CONDITIONS (Mbps)   | MIN TYP <sup>(1)</sup> MAX | UNIT |

|----------------------------------------------------------------------------|--------------------------|----------------------------|------|

|                                                                            | 1 DSSS                   | -96.0                      |      |

|                                                                            | 2 DSSS                   | -94.0                      |      |

|                                                                            | 11 CCK                   | -88.0                      |      |

|                                                                            | 6 OFDM                   | -90.5                      |      |

| Sensitivity                                                                | 9 OFDM                   | -90.0                      | dBm  |

| (8% PER for 11b rates, 10% PER for 11g/11n rates) (10% PER) <sup>(2)</sup> | 18 OFDM                  | -86.5                      | авін |

| , , ,                                                                      | 36 OFDM                  | -80.5                      |      |

|                                                                            | 54 OFDM                  | -74.5                      |      |

|                                                                            | MCS7 (GF) <sup>(3)</sup> | <b>-71.5</b>               |      |

|                                                                            | MCS7 (MM) <sup>(3)</sup> | -70.5                      |      |

| Maximum input level                                                        | 802.11b                  | -4.0                       | dBm  |

| (10% PER)                                                                  | 802.11g                  | -10.0                      | иын  |

- (1) In preregulated 1.85-V mode, RX sensitivity is 0.25- to 1-dB lower.

- (2) Sensitivity is 1-dB worse on channel 13 (2472 MHz).

- (3) Sensitivity for mixed mode is 1-dB worse.

# 4.10 WLAN Transmitter Characteristics

$T_A = 25$ °C,  $V_{BAT} = 2.1$  V to 3.6 V. Parameters measured at SoC pin on channel 7 (2442 MHz). (1)

| PARAMETER                                                                | TEST CONDITIONS (2) | MIN TYP | MAX | UNIT |

|--------------------------------------------------------------------------|---------------------|---------|-----|------|

|                                                                          | 1 DSSS              | +18.0   |     |      |

|                                                                          | 2 DSSS              | +18.0   |     |      |

|                                                                          | 11 CCK              | +18.3   |     |      |

|                                                                          | 6 OFDM              | +17.3   |     |      |

| Maximum RMS output power measured at 1 dB from IEEE spectral mask or EVM | 9 OFDM              | +17.3   |     | dBm  |

| ab nom izzz oposital mask of z vivi                                      | 18 OFDM             | +17.0   |     |      |

|                                                                          | 36 OFDM             | +16.0   |     |      |

|                                                                          | 54 OFDM             | +14.5   |     |      |

|                                                                          | MCS7 (MM)           | +13.0   |     |      |

| Transmit center frequency accuracy                                       |                     | -25     | 25  | ppm  |

<sup>(1)</sup> Channel-to-channel variation is up to 2 dB. The edge channels (2412 and 2472 MHz) have reduced TX power to meet FCC emission limits.

NSTRUMENTS

<sup>(2)</sup> In preregulated 1.85-V mode, maximum TX power is 0.25- to 0.75-dB lower for modulations higher than 18 OFDM.

# 4.11 WLAN Filter Requirements

The device requires an external band-pass filter to meet the various emission standards, including FCC. Table 4-2 presents the attenuation requirements for the band-pass filter. TI recommends using the same filter used in the reference design to ease the process of certification.

**Table 4-2. WLAN Filter Requirements**

| PARAMETER                     | FREQUENCY (MHz) | MIN | TYP | MAX | UNIT |

|-------------------------------|-----------------|-----|-----|-----|------|

| Return loss                   | 2412 to 2484    | 10  |     |     | dB   |

| Insertion loss <sup>(1)</sup> | 2412 to 2484    |     | 1   | 1.5 | dB   |

|                               | 800 to 830      | 30  | 45  |     |      |

|                               | 1600 to 1670    | 20  | 25  |     |      |

|                               | 3200 to 3300    | 30  | 48  |     |      |

|                               | 4000 to 4150    | 45  | 50  |     |      |

| Attenuation                   | 4800 to 5000    | 20  | 25  |     | dB   |

|                               | 5600 to 5800    | 20  | 25  |     |      |

|                               | 6400 to 6600    | 20  | 35  |     |      |

|                               | 7200 to 7500    | 35  | 45  |     |      |

|                               | 7500 to 10000   | 20  | 25  |     |      |

| Reference impendence          | 2412 to 2484    |     | 50  |     | Ω    |

| Filter type                   | Bandpass        |     |     |     |      |

<sup>(1)</sup> Insertion loss directly impacts output power and sensitivity. At customer discretion, insertion loss can be relaxed to meet attenuation requirements.

# 4.12 Thermal Resistance Characteristics for RGK Package

|                   | AIR FLOW    |               |               |               |  |  |  |  |

|-------------------|-------------|---------------|---------------|---------------|--|--|--|--|

| PARAMETER         | 0 Ifm (C/W) | 150 Ifm (C/W) | 250 Ifm (C/W) | 500 Ifm (C/W) |  |  |  |  |

| $\theta_{ja}$     | 23          | 14.6          | 12.4          | 10.8          |  |  |  |  |

| $\Psi_{jt}$       | 0.2         | 0.2           | 0.3           | 0.1           |  |  |  |  |

| $\Psi_{jb}$       | 2.3         | 2.3           | 2.2           | 2.4           |  |  |  |  |

| $\theta_{\sf jc}$ | 6.3         |               |               |               |  |  |  |  |

| $\theta_{jb}$     | 2.4         |               |               |               |  |  |  |  |

SWAS034 - FEBRUARY 2017

# ISTRUMENTS www.ti.com

# 4.13 Timing and Switching Characteristics

# 4.13.1 Power Supply Sequencing

For proper operation of the CC3120R device, perform the recommended power-up sequencing as follows:

- 1. Tie VBAT (pins 37, 39, 44) and VIO (pins 54 and 10) together on the board.

- 2. Hold the RESET pin low while the supplies are ramping up. TI recommends using a simple RC circuit  $(100 \text{ K} \parallel, 1 \mu\text{F}, RC = 100 \text{ ms}).$

- 3. For an external RTC, ensure that the clock is stable before RESET is deasserted (high).

For timing diagrams, see Section 4.13.3.

### 4.13.2 Device Reset

When a device restart is required, the user may either issue a negative pulse on the nHIB pin (pin 2) or on the nRESET pin (pin 32), keeping the other pulled high, depending on the configuration of the platform. In case the nRESET pin is used, the user must follow one of the two alternatives to ensure the reset is properly applied:

- A high-to-low reset pulse (on pin 32) of at least 200-mS duration

- If the above cannot be ensured, a pulldown resistor of 2M Ω should be connected to pin 32 (RTC\_XTAL\_N). If implemented, a shorter pulse of at least 100 uSec can be used.

To ensure a proper reset sequence, the user has to call the sl stop function prior to toggling the reset.

# 4.13.3 Reset Timing

## 4.13.3.1 nRESET (32k XTAL)

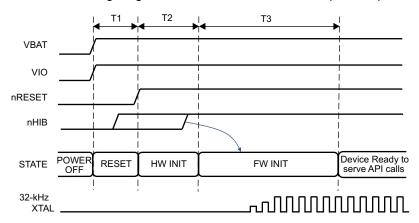

Figure 4-6 shows the reset timing diagram for the 32k XTAL first-time power-up and reset removal.

Figure 4-6. First-Time Power-Up and Reset Removal Timing Diagram (32k XTAL)

Table 4-3 describes the timing requirements for the XTAL first-time power-up and reset removal.

Table 4-3. First-Time Power-Up and Reset Removal Timing Requirements (32k XTAL)

| ITEM | NAME                  | DESCRIPTION                                                                   | MIN | TYP  | MAX | UNIT |

|------|-----------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| T1   | Supply settling time  | Depends on application board power supply, decoupling capacitor, and so on    |     | 3    |     | ms   |

| T2   | Hardware wake-up time |                                                                               |     | 25   |     | ms   |

| Т3   | Initialization time   | 32-kHz XTAL settling plus firmware initialization time plus radio calibration |     | 1.35 |     | s    |

# 4.13.3.2 nRESET (External 32K)

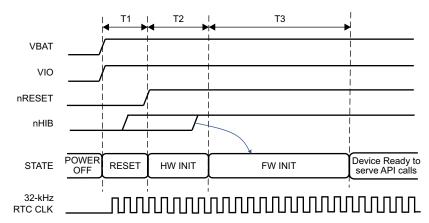

Figure 4-7 shows the reset timing diagram for the external 32K first-time power-up and reset removal.

Figure 4-7. First-Time Power-Up and Reset Removal Timing Diagram (External 32K)

describes the timing requirements for the external first-time power-up and reset removal.

Table 4-4. First-Time Power-Up and Reset Removal Timing Requirements (External 32K)

| ITEM | NAME                  | DESCRIPTION                                                                | MIN | TYP | MAX | UNIT |

|------|-----------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| Т1   | Supply settling time  | Depends on application board power supply, decoupling capacitor, and so on |     | 3   |     | ms   |

| T2   | Hardware wake-up time |                                                                            |     | 25  |     | ms   |

| Т3   | Initialization time   | Firmware initialization time plus radio calibration                        |     | 250 |     | ms   |

# NSTRUMENTS

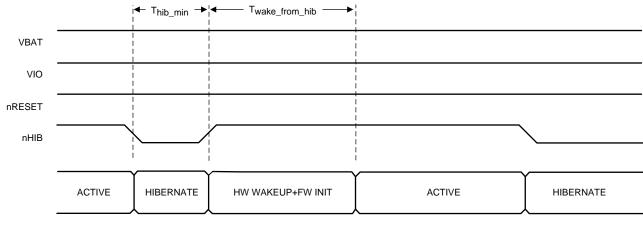

## 4.13.3.3 Wakeup From HIBERNATE Mode

Figure 4-8 shows the timing diagram for wakeup from HIBERNATE mode.

32-kHz XTAL/CXO

Figure 4-8. nHIB Timing Diagram

#### NOTE

The 32.768-kHz XTAL is kept enabled by default when the chip goes into HIBERNATE mode in response to nHIB being pulled low.

Table 4-5 describes the timing requirements for nHIB.

Table 4-5. nHIB Timing Requirements

| ITEM                       | NAME                                                   | DESCRIPTION                                          | MIN | TYP | MAX | UNIT |

|----------------------------|--------------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| T <sub>hib_min</sub>       | Minimum hibernate time                                 | Minimum pulse width of nHIB being low <sup>(1)</sup> | 10  |     |     | ms   |

| T <sub>wake_from_hib</sub> | Hardware wakeup time plus firmware initialization time | See <sup>(2)</sup>                                   |     | 50  |     | ms   |

Ensure that the nHIB pulse width is kept above the minimum requirement under all conditions (such as power up, MCU reset, and so

# 4.13.4 Clock Specifications

The CC3120R device requires two separate clocks for its operation:

- A slow clock running at 32.768 kHz is used for the RTC.

- A fast clock running at 40 MHz is used by the device for the internal processor and the WLAN subsystem.

The device features internal oscillators that enable the use of less-expensive crystals rather than dedicated TCXOs for these clocks. The RTC can also be fed externally to provide reuse of an existing clock on the system and to reduce overall cost.

If temperature changes by more than 20°C, initialization time from HIB can increase by 200 ms due to radio calibration.

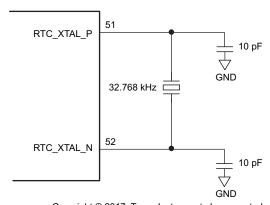

#### 4.13.4.1 Slow Clock Using Internal Oscillator

The RTC crystal connected on the device supplies the free-running slow clock. The accuracy of the slow clock frequency must be 32.768 kHz ±150 ppm. In this mode of operation, the crystal is tied between RTC\_XTAL\_P (pin 51) and RTC\_XTAL\_N (pin 52) with a suitable load capacitance to meet the ppm requirement.

Figure 4-9 shows the crystal connections for the slow clock.

Copyright © 2017, Texas Instruments Incorporated

Figure 4-9. RTC Crystal Connections

Table 4-6 lists the RTC crystal requirements.

**Table 4-6. RTC Crystal Requirements**

| CHARACTERISTICS    | TEST CONDITIONS                     | MIN | TYP    | MAX  | UNIT |

|--------------------|-------------------------------------|-----|--------|------|------|

| Frequency          |                                     |     | 32.768 |      | kHz  |

| Frequency accuracy | Initial plus temperature plus aging |     |        | ±150 | ppm  |

| Crystal ESR        | 32.768 kHz                          |     |        | 70   | kΩ   |

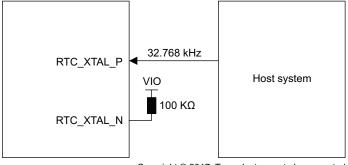

#### 4.13.4.2 Slow Clock Using an External Clock

When an RTC oscillator is present in the system, the CC3120R device can accept this clock directly as an input. The clock is fed on the RTC\_XTAL\_P line, and the RTC\_XTAL\_N line is held to VIO. The clock must be a CMOS-level clock compatible with VIO fed to the device.

Figure 4-10 shows the external RTC input connection.

Copyright © 2017, Texas Instruments Incorporated

Figure 4-10. External RTC Input

Table 4-7 lists the external RTC digital clock requirements.

Table 4-7. External RTC Digital Clock Requirements

|                                 | CHARACTERISTICS                                          | TEST CONDITIONS                  | MIN        | TYP   | MAX        | UNIT       |

|---------------------------------|----------------------------------------------------------|----------------------------------|------------|-------|------------|------------|

|                                 | Frequency                                                |                                  |            | 32768 |            | Hz         |

|                                 | Frequency accuracy (Initial plus temperature plus aging) |                                  |            | ±150  |            | ppm        |

| t <sub>r</sub> , t <sub>f</sub> | Input transition time $t_r$ , $t_f$ (10% to 90%)         |                                  |            |       | 100        | ns         |

|                                 | Frequency input duty cycle                               |                                  | 20%        | 50%   | 80%        |            |

| V <sub>ih</sub>                 | Class also le importe calta da limita                    | Carrage results and a second and | 0.65 × VIO |       | VIO        | V          |

| V <sub>il</sub>                 | Slow clock input voltage limits                          | Square wave, DC coupled          | 0          |       | 0.35 × VIO | $V_{peak}$ |

|                                 | lanut impadance                                          |                                  | 1          |       |            | ΜΩ         |

|                                 | Input impedance                                          |                                  |            |       | 5          | pF         |

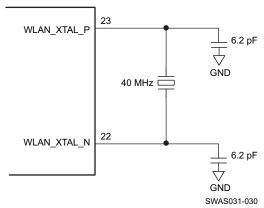

# 4.13.4.3 Fast Clock (F<sub>ref</sub>) Using an External Crystal

The CC3120R device also incorporates an internal crystal oscillator to support a crystal-based fast clock. The XTAL is fed directly between WLAN\_XTAL\_P (pin 23) and WLAN\_XTAL\_N (pin 22) with suitable loading capacitors.

Figure 4-11 shows the crystal connections for the fast clock.

NOTE: The XTAL capacitance must be tuned to ensure that the PPM requirement is met. See CC31xx & CC32xx Frequency Tuning for information on frequency tuning.

Figure 4-11. Fast Clock Crystal Connections

www.ti.com SWAS034 – FEBRUARY 2017

Table 4-8 lists the WLAN fast-clock crystal requirements.

Table 4-8. WLAN Fast-Clock Crystal Requirements

| CHARACTERISTICS    | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------|-----|-----|-----|------|

| Frequency          |                                     |     | 40  |     | MHz  |

| Frequency accuracy | Initial plus temperature plus aging |     |     | ±25 | ppm  |

| Crystal ESR        | 40 MHz                              |     |     | 60  | Ω    |

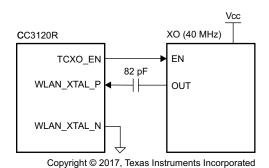

# 4.13.4.4 Fast Clock (F<sub>ref</sub>) Using an External Oscillator

The CC3120R device can accept an external TCXO/XO for the 40-MHz clock. In this mode of operation, the clock is connected to WLAN\_XTAL\_P (pin 23). WLAN\_XTAL\_N (pin 22) is connected to GND. The external TCXO/XO can be enabled by TCXO\_EN (pin 21) from the device to optimize the power consumption of the system.

If the TCXO does not have an enable input, an external LDO with an enable function can be used. Using the LDO improves noise on the TCXO power supply.

Figure 4-12 shows the connection.

Figure 4-12. External TCXO Input

Table 4-9 lists the external F<sub>ref</sub> clock requirements.

Table 4-9. External F<sub>ref</sub> Clock Requirements (-40°C to +85°C)

|          | CHARACTE                     | RISTICS                      | TEST CONDITIONS                       | MIN | TYP   | MAX    | UNIT     |

|----------|------------------------------|------------------------------|---------------------------------------|-----|-------|--------|----------|

|          | Frequency                    |                              |                                       |     | 40.00 |        | MHz      |

|          | Frequency accuracy (I aging) | nitial plus temperature plus |                                       |     |       | ±25    | ppm      |

|          | Frequency input duty of      | ycle                         |                                       | 45% | 50%   | 55%    |          |

| $V_{pp}$ | Clock voltage limits         |                              | Sine or clipped sine wave, AC coupled | 0.7 |       | 1.2    | $V_{pp}$ |

|          |                              |                              | @ 1 kHz                               |     |       | -125   |          |

|          | Phase noise @ 40 MH          | z                            | @ 10 kHz                              |     |       | -138.5 | dBc/Hz   |

|          |                              |                              | @ 100 kHz                             |     |       | -143   |          |

|          | Innut impedance              | Resistance                   |                                       | 12  | ·     |        | kΩ       |

|          | Input impedance              | Capacitance                  |                                       |     |       | 7      | pF       |

# 4.13.5 Interfaces

This section describes the interfaces that are supported by the CC3120R device:

- Host SPI

- Flash SPI

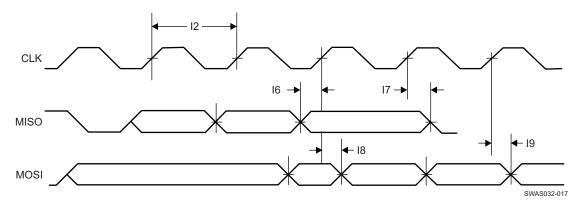

# 4.13.5.1 Host SPI Interface Timing

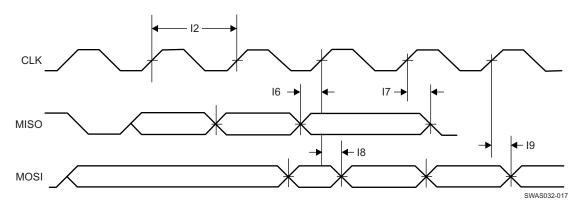

Figure 4-13 shows the Host SPI interface timing diagram.

Figure 4-13. Host SPI Interface Timing

Table 4-10 lists the Host SPI interface timing parameters.

**Table 4-10. Host SPI Interface Timing Parameters**

| PARAMETER<br>NUMBER |                                    |                                            | MIN | MAX | UNIT |

|---------------------|------------------------------------|--------------------------------------------|-----|-----|------|

| I1                  | F <sup>(1)</sup>                   | Clock frequency @ V <sub>BAT</sub> = 3.3 V |     | 20  | MHz  |

|                     |                                    | Clock frequency @ V <sub>BAT</sub> ≤ 2.1 V |     | 12  |      |

| 12                  | t <sub>clk</sub> <sup>(2)(1)</sup> | Clock period                               | 50  |     | ns   |

| 13                  | t <sub>LP</sub> <sup>(1)</sup>     | Clock low period                           |     | 25  | ns   |

| 14                  | t <sub>HT</sub> <sup>(1)</sup>     | Clock high period                          |     | 25  | ns   |

| 15                  | D <sup>(1)</sup>                   | Duty cycle                                 | 45% | 55% |      |

| 16                  | t <sub>IS</sub> <sup>(1)</sup>     | RX data setup time                         | 4   |     | ns   |

| 17                  | t <sub>IH</sub> <sup>(1)</sup>     | RX data hold time                          | 4   |     | ns   |

| 18                  | t <sub>OD</sub> <sup>(1)</sup>     | TX data output delay                       |     | 20  | ns   |

| 19                  | t <sub>OH</sub> <sup>(1)</sup>     | TX data hold time                          |     | 24  | ns   |

The timing parameter has a maximum load of 20 pF at 3.3  $\rm V.$

NSTRUMENTS

Ensure that nCS (active-low signal) is asserted 10 ns before the clock is toggled. nCS can be deasserted 10 ns after the clock edge.

# 4.13.5.2 Flash SPI Interface Timing

Figure 4-14 shows the Flash SPI interface timing diagram.

Figure 4-14. Flash SPI Interface Timing

Table 4-11 lists the Flash SPI interface timing parameters.

**Table 4-11. Flash SPI Interface Timing Parameters**

|                     |                  |                      | •   |     |      |

|---------------------|------------------|----------------------|-----|-----|------|

| PARAMETER<br>NUMBER |                  |                      | MIN | MAX | UNIT |

| I1                  | F                | Clock frequency      |     | 20  | MHz  |

| 12                  | t <sub>clk</sub> | Clock period         | 50  |     | ns   |

| 13                  | t <sub>LP</sub>  | Clock low period     |     | 25  | ns   |

| 14                  | t <sub>HT</sub>  | Clock high period    |     | 25  | ns   |

| 15                  | D                | Duty cycle           | 45% | 55% |      |

| 16                  | t <sub>IS</sub>  | RX data setup time   | 1   |     | ns   |

| 17                  | t <sub>IH</sub>  | RX data hold time    | 2   |     | ns   |

| 18                  | t <sub>OD</sub>  | TX data output delay |     | 8.5 | ns   |

| 19                  | t <sub>OH</sub>  | TX data hold time    |     | 8   | ns   |

# 4.14 External Interfaces

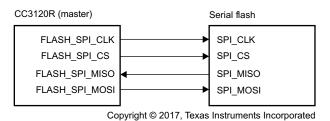

## 4.14.1 SPI Flash Interface

The external serial flash stores the user profiles and firmware patch updates. The CC3120R device acts as a master in this case; the SPI serial flash acts as the slave device. This interface can work up to a speed of 20 MHz.

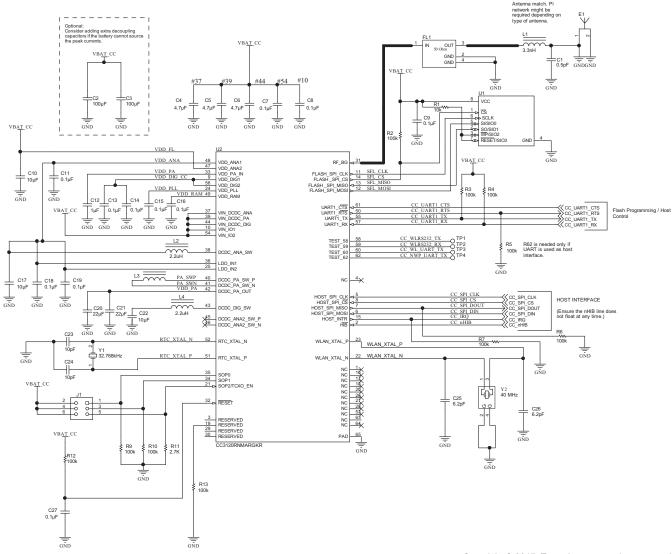

Figure 4-15 shows the SPI flash interface.

Figure 4-15. SPI Flash Interface

Table 4-12 lists the SPI flash interface pins.

Table 4-12. SPI Flash Interface

| PIN NAME       | DESCRIPTION                                         |

|----------------|-----------------------------------------------------|

| FLASH_SPI_CLK  | Clock (up to 20 MHz) CC3120R device to serial flash |

| FLASH_SPI_CS   | CS signal from CC3120R device to serial flash       |

| FLASH_SPI_MISO | Data from serial flash to CC3120R device            |

| FLASH_SPI_MOSI | Data from CC3120R device to serial flash            |

**ISTRUMENTS**

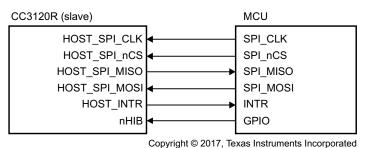

# 4.14.2 SPI Host Interface

The device interfaces to an external host using the SPI interface. The CC3120R device can interrupt the host using the HOST\_INTR line to initiate the data transfer over the interface. The SPI host interface can work up to a speed of 20 MHz.

Figure 4-16 shows the SPI host interface.

Copyright © 2017, Toxad motiamento modipo

Figure 4-16. SPI Host Interface

Table 4-13 lists the SPI host interface pins.

Table 4-13. SPI Host Interface

| PIN NAME      | DESCRIPTION                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------|

| HOST_SPI_CLK  | Clock (up to 20 MHz) from MCU host to CC3120R device                                            |

| HOST_SPI_nCS  | CS (active low) signal from MCU host to CC3120R device                                          |

| HOST_SPI_MOSI | Data from MCU host to CC3120R device                                                            |

| HOST_INTR     | Interrupt from CC3120R device to MCU host                                                       |

| HOST_SPI_MISO | Data from CC3120R device to MCU host                                                            |

| nHIB          | Active-low signal that commands the CC3120R device to enter hibernate mode (lowest power state) |

#### 4.15 Host UART

The SimpleLink device requires the UART configuration described in Table 4-14.

Table 4-14. SimpleLink UART Configuration

| PROPERTY                | SUPPORTED CC3120R CONFIGURATION                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------|

| Baud rate               | 115200 bps, no auto-baud rate detection, can be changed by the host up to 3 Mbps using a special command |

| Data bits               | 8 bits                                                                                                   |

| Flow control            | CTS/RTS                                                                                                  |

| Parity                  | None                                                                                                     |

| Stop bits               | 1                                                                                                        |

| Bit order               | LSBit first                                                                                              |

| Host interrupt polarity | Active high                                                                                              |

| Host interrupt mode     | Rising edge or level 1                                                                                   |

| Endianness              | Little-endian only <sup>(1)</sup>                                                                        |

<sup>(1)</sup> The SimpleLink device does not support automatic detection of the host length while using the UART interface.

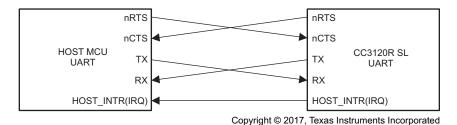

# 4.15.1 5-Wire UART Topology

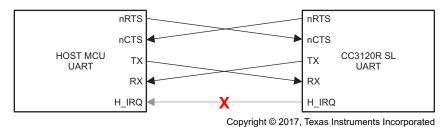

Figure 4-17 shows the typical 5-wire UART topology comprised of four standard UART lines plus one IRQ line from the device to the host controller to allow efficient low-power mode.

Figure 4-17. Typical 5-Wire UART Topology

This topology is recommended because the configuration offers the maximum communication reliability and flexibility between the host and the SimpleLink device.

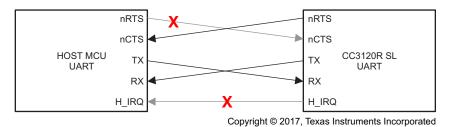

## 4.15.2 4-Wire UART Topology

The 4-wire UART topology eliminates the host IRQ line (see Figure 4-18). Using this topology requires meeting one of the following conditions:

- The host is always awake or active.

- The host goes to sleep, but the UART module has receiver start-edge detection for auto wakeup and does not lose data.

Figure 4-18. 4-Wire UART Configuration

Specifications

# 4.15.3 3-Wire UART Topology

The 3-wire UART topology requires only the following lines (see Figure 4-19):

- RX

- TX

- CTS

Figure 4-19. 3-Wire UART Topology

Using this topology requires meeting one of the following conditions:

- The host always stays awake or active.

- The host goes to sleep but the UART module has receiver start-edge detection for auto-wake-up and does not lose data.

- The host can always receive any amount of data transmitted by the SimpleLink device because there

is no flow control in this direction.

Because there is no full flow control, the host cannot stop the SimpleLink device to send its data; thus, the following parameters must be carefully considered:

- · Maximum baud rate

- · RX character interrupt latency and low-level driver jitter buffer

- Time consumed by the user's application

# 5 Detailed Description

#### 5.1 Overview

The CC3120R Wi-Fi Internet-on-a-chip contains a dedicated ARM MCU that offloads many of the networking activities from the host MCU. The device includes an 802.11b/g/n radio, baseband, and MAC with a powerful crypto engine for a fast, secure WLAN and Internet connections with 256-bit encryption. The CC3120R device supports station, AP, and Wi-Fi Direct modes. The device also supports WPA2 personal and enterprise security and WPS 2.0. The Wi-Fi network processor includes an embedded IPv6 and IPv4 TCP/IP stack.

# 5.2 Functional Block Diagram

Figure 5-1 shows the functional block diagram of the CC3120R SimpleLink Wi-Fi solution.

Figure 5-1. Functional Block Diagram

# 5.3 Device Features

#### 5.3.1 WLAN

The WLAN features are as follows:

802.11b/g/n integrated radio, modem, and MAC supporting WLAN communication as a BSS station, AP, Wi-Fi Direct client and group owner with CCK and OFDM rates in the 2.4-GHz ISM band, channels 1 to 13.

# NOTE

802.11n is supported only in Wi-Fi station, Wi-Fi direct, and P2P client mode

- Autocalibrated radio with a single-ended  $50-\Omega$  interface enables easy connection to the antenna without requiring expertise in radio circuit design.

- Advanced connection manager with multiple user-configurable profiles stored in serial-flash allows automatic fast connection to an access point without user or host intervention.

- Supports all common Wi-Fi security modes for personal and enterprise networks with on-chip security accelerators, including: WEP, WPA/WPA2 PSK, WPA2 Enterprise (802.1x).

- Smart provisioning options deeply integrated within the device providing a comprehensive end-to-end solution. With elaborate events notification to the host, enabling the application to control the provisioning decision flow. The wide variety of Wi-Fi provisioning methods include:

- Access Point using HTTPS

- SmartConfig Technology: a 1-step, 1-time process to connect a CC3120R-enabled device to the home wireless network, removing dependency on the I/O capabilities of the host MCU; thus, it is usable by deeply embedded applications

- 802.11 transceiver mode allows transmitting and receiving of proprietary data through a socket without adding MAC or PHY headers. The 802.11 transceiver mode provides the option to select the working channel, rate, and transmitted power. The receiver mode works with the filtering options.

#### 5.3.2 Network Stack

The Network Stack features are as follows:

Integrated IPv4, IPv6 TCP/IP stack with BSD (BSD adjacent) socket APIs for simple Internet connectivity with any MCU, microprocessor, or ASIC

#### NOTE

Not all APIs are 100% BSD compliant. Not all BSD APIs are supported.

- Support of 16 simultaneous TCP, UDP, or RAW sockets

- Support of 6 simultaneous SSL\TLS sockets

- Built-in network protocols:

- Static IP, LLA, DHCPv4, DHCPv6 with DAD and stateless autoconfiguration

- ARP, ICMPv4, IGMP, ICMPv6, MLD, ND

- DNS client for easy connection to the local network and the Internet

TEXAS INSTRUMENTS

- · Built-in network application and utilities:

- HTTP/HTTPS

- · Web page content stored on serial flash

- RESTful APIs for setting and configuring application content

- Dynamic user callbacks

- Service discovery: Multicast DNS service discovery lets a client advertise its service without a centralized server. After connecting to the access point, the CC3120R device provides critical information, such as device name, IP, vendor, and port number.

- DHCP server

- Ping

Table 5-1 summarizes the NWP features.

Table 5-1. NWP Features

| Feature                            | Description                                                                                       |

|------------------------------------|---------------------------------------------------------------------------------------------------|

|                                    | 802.11b/g/n station                                                                               |

| Wi-Fi standards                    | 802.11b/g AP supporting up to four stations                                                       |

|                                    | Wi-Fi Direct client and group owner                                                               |

| Wi-Fi                              | Channels 1 to 13                                                                                  |

| Wi-Fi security                     | WEP, WPA/WPA2 PSK, WPA2 enterprise (802.1x)                                                       |

| Wi-Fi provisioning                 | SmartConfig technology, Wi-Fi protected setup (WPS2), AP mode with internal HTTP/HTTPS web server |

| IP protocols                       | IPv4/IPv6                                                                                         |

| IP addressing                      | Static IP, LLA, DHCPv4, DHCPv6 (Stateful) with DAD and stateless auto configuration               |