# **kHz Band Temperature Compensated MEMS Oscillator**

## MO1566

#### ■ Features

- ●32.768 kHz ±5 x 10<sup>-6</sup> all-inclusive frequency stability

- Smallest TCXO Footprint: 1.2mm²

- •1.5 x 0.8 mm CSP / •No external bypass cap required

- ■Ultra-low power: +4.5 µA

- Improved stability reduces system power with fewer network timekeeping updates

### ■ Applications

- Smart watches, Health and wellness monitors

- Smart utility meters

- Internet of Things (IoT)

- Ultra-accurate RTC reference clock

**■**Standard Specification

Conditions: Min/Max limits are over temperature, Vdd = +1.8V±10%, unless otherwise stated. Typicals are at +25°C and Vdd = +1.8V.

| Item                                      | symbol     | Min.                 | Тур. | Max.      | Unit                  | Condition                                                                                                                                |

|-------------------------------------------|------------|----------------------|------|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Output Frequency                          | Fout       | t 32.768             |      |           | kHz                   |                                                                                                                                          |

| Operating Supply Voltage                  | Vdd        | +1.62                | +1.8 | +1.98     | V                     |                                                                                                                                          |

| Operating remperature Range               | T_use      | se -20~+70 / -40~+85 |      |           | °C                    |                                                                                                                                          |

| Total Frequency Stability[1]              | F_stab     | -5.0                 | -    | +5.0      | x 10 <sup>-6</sup>    | All inclusive, without overmold.                                                                                                         |

| Allan Deviation                           | AD         | -                    | 1e-8 | 4e-8      | -                     | 1 second averaging time                                                                                                                  |

| First Year Frequency Aging                | F_aging    | -                    | ±1.0 | -         | x 10 <sup>-6</sup>    | $T_A = +25^{\circ}C$ , Vdd = +1.8V                                                                                                       |

| Supply Current                            | ldd        | -                    | +4.5 | +5.3      | μΑ                    | No load                                                                                                                                  |

| Start-up Time at Power-up                 | t_start    | -                    | -    | 300       | ms                    | Measured when supply reaches 90% of final Vdd to the first output pulse.                                                                 |

| Output Clock Duty Cycle                   | DC         | 45                   | -    | 55        | %                     |                                                                                                                                          |

| Output Voltage Low                        | $V_{OL}$   | -                    | -    | Vdd x 0.1 | <b>→</b> ∨ ⊦          | $I_{OL} = +1.0 \ \mu A$                                                                                                                  |

| Output Voltage High                       | $V_{OH}$   | Vdd x 0.9            | -    | -         |                       | I <sub>OH</sub> = -1.0 μA                                                                                                                |

| Output Rise/Fall Time                     | tr,tf      | -                    | 9.0  | 20        | ns                    | 10-90% (Vdd), 15 pF Load                                                                                                                 |

| Integrated Phase Jitter                   | IPJ        | -                    | 1.8  | 2.5       | ns <sub>RMS</sub>     | Integration bandwidth = 100 Hz to 16.384 kHz. Inclusive of +50mV peak-to-peaks inusoidal noise on Vdd. Noise frequency 100 Hz to 20 MHz. |

| RMS Period Jitter                         | $PJ_{RMS}$ | -                    | 2.5  | 4         | ns <sub>RMS</sub>     | 10,000 samples, per JEDEC standard 65B                                                                                                   |

| Peak-to-Peak Period Jitter                | $PJ_{p-p}$ | -                    | 20   | 35        | ns <sub>p-p</sub>     |                                                                                                                                          |

| Dynamic Temperature<br>Frequency Response | -          | -0.5                 | -    | +0.5      | 10 <sup>-6</sup> /sec | Under temp ramp up to +1.5°C/sec                                                                                                         |

<sup>[1].</sup> Relative to 32.768 kHz, includes initial tolerance, over temp stability, Vdd, load variation, hysteresis, board-level underfill, 3x reflow. Tested with Keysight 53132A frequency counter. Measured with 100 ms gate time for accurate frequency measurement.

Consult our sales representative for other specifications.

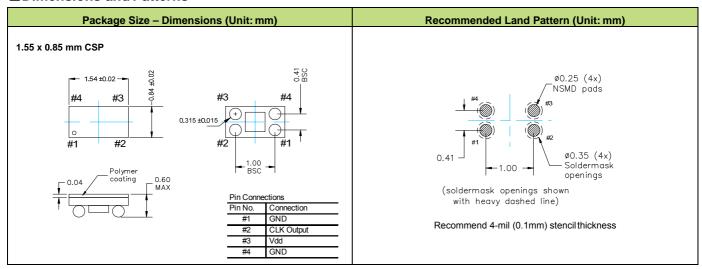

#### **■** Dimensions and Patterns