# **Intel<sup>®</sup> Platform Controller Hub EG20T**

**Datasheet**

**July 2012**

Order Number: 324211-009US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor%5Fnumber/ for details.

$\alpha$  Intel® Hyper-Threading Technology requires an Intel® HT Technology enabled system. Check with your PC manufacturer. Performance will vary depending on the specific hardware and software used. Not available on Intel® Core™ i5-750. For more information including details on which processors support Intel® HT Technology, visit http://www.intel.com/technology/platform-technology/hyper-threading/index.htm.

β Intel<sup>®</sup> High Definition Audio requires an Intel<sup>®</sup> HD Audio enabled system. Consult your PC manufacturer for more information. Sound quality will depend on equipment and actual implementation. For more information about Intel<sup>®</sup> HD Audio, refer to http://www.intel.com/design/chipsets/hdaudio.htm.

$\chi$  Intel<sup>®</sup> 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit http://developer.intel.com/technology/intel64/index.htm.

$\delta$  Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/technology/virtualization/server/.

ε The original equipment manufacturer must provide Intel<sup>®</sup> Trusted Platform Module (Intel<sup>®</sup> TPM) functionality, which requires an Intel<sup>®</sup> TPM-supported BIOS. Intel<sup>®</sup> TPM functionality must be initialized and may not be available in all countries.

$\theta$  For Enhanced Intel SpeedStep® Technology, see the Processor Spec Finder at http://ark.intel.com/, or contact your Intel representative for more information.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, i960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow. the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel YPro, Intel XScale, InTru, the InTru logo, the InTru Inside logo, InTru soundmark, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, skoool, the skoool logo, Sound Mark, The Creators Project, The Journey Inside, VPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

Copyright @ 2009-2012, Intel Corporation and/or its suppliers and licensors. All rights reserved.

Intel<sup>®</sup> Platform Controller Hub EG20T Datasheet

July 2012 Order Number: 324211-009US

## **Contents**

| 1.0 | Ove | rview                |                                                         | 45   |

|-----|-----|----------------------|---------------------------------------------------------|------|

|     | 1.1 | Referer              | nce Documents                                           | 47   |

|     | 1.2 | Feature              | PS                                                      | 47   |

|     | 1.3 | Devices              | s and Functions                                         | 51   |

| 2.0 | PCI | Express <sup>3</sup> | * Bridge                                                | 55   |

|     | 2.1 | Overvie              |                                                         | 55   |

|     | 2.2 |                      | nal Clarification                                       |      |

|     | 2.3 |                      | r Address Map                                           |      |

|     |     | 2.3.1                | PCI Configuration Registers                             |      |

|     | 2.4 | PCI Cor              | nfiguration Registers                                   |      |

|     |     | 2.4.1                | VID— Vendor Identification Register                     |      |

|     |     | 2.4.2                | DID— Device Identification Register                     |      |

|     |     | 2.4.3                | PCICMD— PCI Command Register                            |      |

|     |     | 2.4.4                | PCISTS—PCI Status Register                              |      |

|     |     | 2.4.5                | RID— Revision Identification Register                   |      |

|     |     | 2.4.6                | CC— Class Code Register                                 |      |

|     |     | 2.4.7                | MLT— Master Latency Timer Register                      |      |

|     |     | 2.4.8                | HEADTYP— Header Type Register                           | 60   |

|     |     | 2.4.9                | PBN— Primary Bus Number Register                        | 60   |

|     |     | 2.4.10               | SDBN— Secondary Bus Number Register                     | . 61 |

|     |     | 2.4.11               | SBBN— Subordinate Bus Number Register                   | 61   |

|     |     | 2.4.12               | SDLT— Secondary Latency Timer Register                  | 61   |

|     |     | 2.4.13               | IOBS— I/O Base Register                                 | 61   |

|     |     |                      | IOLMT— I/O Limit Register                               |      |

|     |     |                      | SDSTS— Secondary Status Register                        |      |

|     |     |                      | MBS— Memory Base Register                               |      |

|     |     |                      | MLMT— Memory Limit Register                             |      |

|     |     |                      | PMBS— Prefetchable Memory Base Register                 |      |

|     |     |                      | PMLMT— Prefetchable Memory Limit Register               |      |

|     |     |                      | PMUBS— Prefetchable Memory Base Upper 32-bit Register   |      |

|     |     |                      | PMULMT— Prefetchable Memory Limit Upper 32-bit Register |      |

|     |     |                      | IOUBS— I/O Base Upper 16-bit Register                   |      |

|     |     |                      | IOULMT— I/O Limit Upper 16-bit Register                 |      |

|     |     |                      | CAP_PTR— Capabilities Pointer Register                  |      |

|     |     |                      | INT_LN— Interrupt Line Register                         |      |

|     |     |                      | INT_PN— Interrupt Pin Register                          |      |

|     |     |                      | BRG_CTL— Bridge Control Register                        |      |

|     |     |                      | PM_CAPID—PCI Power Management Capability ID Register    |      |

|     |     |                      | NXT_PTR1—Next Item Pointer #1 Register                  |      |

|     |     |                      | PM_CAP—Power Management Capabilities Register           |      |

|     |     |                      | PWR_CNTL_STS—Power Management Control/Status Register   |      |

|     |     |                      | PCIe_CAPID—PCIe Capability ID Register                  |      |

|     |     |                      | PCIe_NPR—PCIe Next Item Pointer Register                |      |

|     |     |                      | PCIe_CP—PCIe Capabilities Register                      |      |

|     |     |                      | PCIe_DCP—PCIe Device Capabilities Register              |      |

|     |     |                      | PCIe_DCT—PCIe Device Control Register                   |      |

|     |     |                      | PCIe_DST—PCIe Device Status Register                    |      |

|     |     |                      | PCIe_LCP—PCIe Link Capabilities Register                |      |

|     |     |                      | PCIe_LCT—PCIe Link Control Register                     |      |

|     |     |                      | PCIe_LST—PCIe Link Status Register                      |      |

|     |     | 2.4.41               | PCIe DCP2—PCIe Device Capabilities 2 Register           | ชา   |

|     |       |         |                      | T2—PCIe Device Control 2 Register                     |       |

|-----|-------|---------|----------------------|-------------------------------------------------------|-------|

|     |       |         |                      | T2—PCIe Link Control 2 Register                       |       |

|     |       |         |                      | 72—PCIe Link Status 2 Register                        |       |

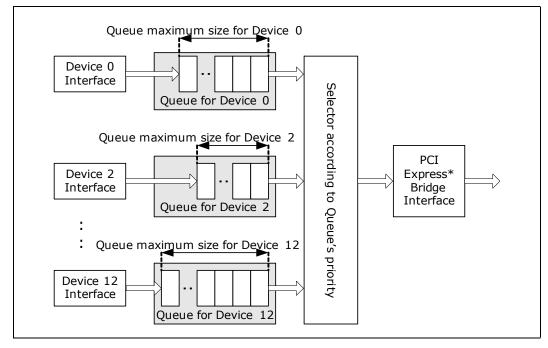

| 3.0 | Pack  | et Hub  |                      |                                                       | 87    |

|     | 3.1   | Overvie | ew                   |                                                       | 87    |

|     | 3.2   |         |                      | Map                                                   |       |

|     |       | 3.2.1   |                      | guration Registers                                    |       |

|     |       | 3.2.2   |                      | Mapped I/O Registers (BAR: MEM_BASE)                  |       |

|     |       | 5.2.2   | 3.2.2.1              | Queue Control Register                                |       |

|     |       |         | 3.2.2.2              | Device Control Registers                              | 03    |

|     | 3.3   | Registe |                      | Device Control (registers                             |       |

|     | 5.5   | 3.3.1   |                      | guration Registers                                    |       |

|     |       | 3.3.1   | 3.3.1.1              | VID— Vendor Identification Register                   |       |

|     |       |         | 3.3.1.2              | DID— Device Identification Register                   |       |

|     |       |         | 3.3.1.3              | PCICMD— PCI Command Register                          | 91    |

|     |       |         | 3.3.1.4              | PCISTS—PCI Status Register                            | 92    |

|     |       |         | 3.3.1.5              | RID— Revision Identification Register                 | 93    |

|     |       |         | 3.3.1.6              | CC— Class Code Register                               | 93    |

|     |       |         | 3.3.1.7              | MLT— Master Latency Timer Register                    | 94    |

|     |       |         | 3.3.1.8              | HEADTYP— Header Type Register                         | 94    |

|     |       |         | 3.3.1.9              | MEM BASE— MEM Base Address Register                   | 94    |

|     |       |         | 3.3.1.10             | ROM_BASE— Extended ROM Base Address Register          | 95    |

|     |       |         | 3.3.1.11             | SSVID— Subsystem Vendor ID Register                   | 95    |

|     |       |         | 3.3.1.12             | SSID— Subsystem ID Register                           | 95    |

|     |       |         | 3.3.1.13             | CAP_PTR— Capabilities Pointer Register                | 96    |

|     |       |         | 3.3.1.14             | INT_LN— Interrupt Line Register                       | 96    |

|     |       |         | 3.3.1.15             | INT_PN— Interrupt Pin Register                        | 96    |

|     |       |         | 3.3.1.16             | MSI_CAPID—MSI Capability ID Register                  | 96    |

|     |       |         | 3.3.1.17<br>3.3.1.18 | MSI_NPR—MSI Next Item Pointer Register                | 97    |

|     |       |         | 3.3.1.19             | MSI_MAR—MSI Message Address Register                  |       |

|     |       |         | 3.3.1.20             | MSI_MD—MSI Message Data Register                      |       |

|     |       |         | 3.3.1.21             | PM_CAPID—PCI Power Management Capability ID Register  |       |

|     |       |         | 3.3.1.22             | PM_NPR—PM Next Item Pointer Register                  | 99    |

|     |       |         | 3.3.1.23             | PM_CAP—Power Management Capabilities Register         | 99    |

|     |       |         | 3.3.1.24             | PWR_CNTL_STS—Power Management Control/Status Register | .100  |

|     |       | 3.3.2   | Memory-              | Mapped I/O Registers (BAR: MEM_BASE)                  |       |

|     |       |         | 3.3.2.1              | Packet Hub ID Register                                |       |

|     |       |         | 3.3.2.2              | Queue Priority Value Register                         | . 101 |

|     |       |         | 3.3.2.3              | Upstream Queue Max Size Register                      |       |

|     |       |         | 3.3.2.4              | Downstream Queue Max Size Register                    |       |

|     |       |         | 3.3.2.5              | Completion Response Time-out Register                 | . 103 |

|     |       |         | 3.3.2.6              | Device Read Pre-Fetch Control Register                |       |

|     |       |         | 3.3.2.7              | Dead Lock Avoid Type Selector Register                |       |

|     |       |         | 3.3.2.8              | Interrupt Pin Register Write Permit Register 0        |       |

|     |       |         | 3.3.2.9              | Interrupt Pin Register Write Permit Register 1        |       |

|     |       |         | 3.3.2.10<br>3.3.2.11 | Interrupt Pin Register Write Permit Register 2        | 106   |

|     |       |         | 3.3.2.11             | Interrupt Pin Register Write Permit Register 3        | 100   |

|     | 3.4   | Eunstin |                      | ption                                                 |       |

|     | 3.4   |         |                      |                                                       |       |

|     |       | 3.4.1   | •                    | Doloted Degisters                                     |       |

|     |       | 2 4 2   | 3.4.1.1              | Related Registers                                     |       |

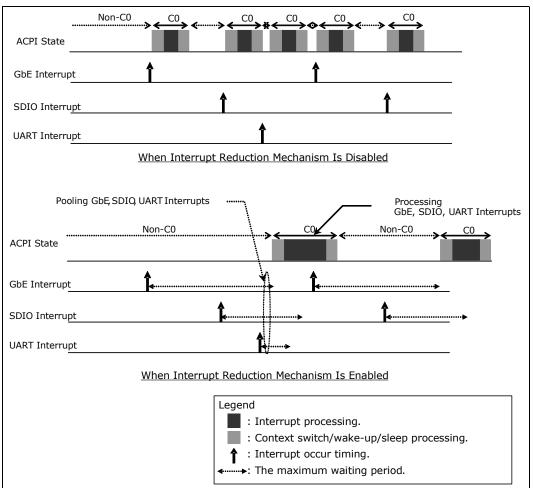

|     |       | 3.4.2   |                      | Reduction Mechanism                                   |       |

|     |       |         | 3.4.2.1              | Related Registers                                     | . 111 |

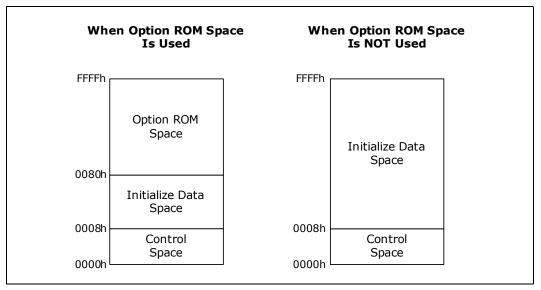

| 4.0 | Seria | I ROM I | interface.           |                                                       | . 113 |

|     | 4.1   | Overvi  | ew                   |                                                       | . 113 |

|     |       | 4.1.1   |                      | Connection When Not Connecting Serial ROM             |       |

|     |       |         |                      |                                                       |       |

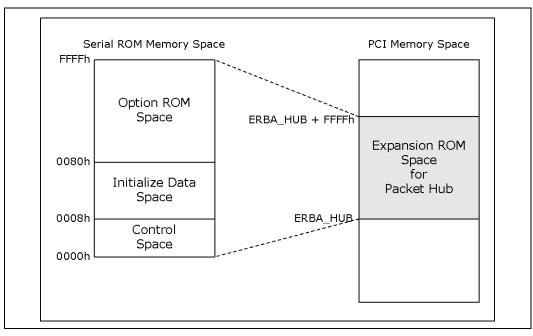

|     |                 | 4.1.2                                                   |                                                                        | JM Address Map Structure                              |                                               |  |  |

|-----|-----------------|---------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|--|--|

|     |                 |                                                         | 4.1.2.1                                                                | Option ROM Space                                      | 114                                           |  |  |

|     |                 |                                                         | 4.1.2.2                                                                | Initialize Data Space                                 | 114                                           |  |  |

|     |                 |                                                         | 4.1.2.3                                                                | Control Space                                         | 116                                           |  |  |

|     | 4.2             | Function                                                | nal Descri                                                             | ption                                                 | 116                                           |  |  |

|     |                 | 4.2.1                                                   |                                                                        | n Mode                                                |                                               |  |  |

|     |                 | 4.2.2                                                   |                                                                        | de                                                    |                                               |  |  |

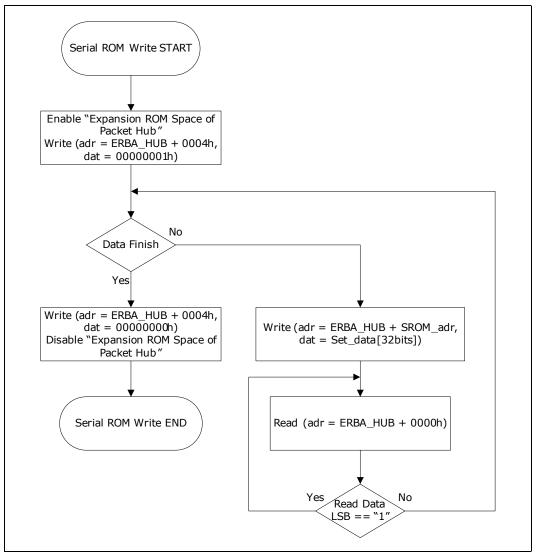

|     |                 | 7.2.2                                                   | 4.2.2.1                                                                | The Serial ROM Writing Method                         |                                               |  |  |

|     |                 |                                                         | 4.2.2.1                                                                | Special Address                                       |                                               |  |  |

|     |                 | 4.2.3                                                   |                                                                        |                                                       |                                               |  |  |

|     |                 | 4.2.3                                                   | •                                                                      | of Serial ROM Data                                    |                                               |  |  |

|     |                 |                                                         | 4.2.3.1                                                                | When Not Using Initialize Function                    |                                               |  |  |

|     |                 |                                                         | 4.2.3.2                                                                | Only MAC Address Set                                  | 120                                           |  |  |

|     |                 |                                                         | 4.2.3.3                                                                | Only Subsystem ID or Subsystem Vendor ID Set          |                                               |  |  |

|     |                 |                                                         | 4.2.3.4                                                                | MAC Address & Subsystem ID or Subsystem Vendor ID Set | 121                                           |  |  |

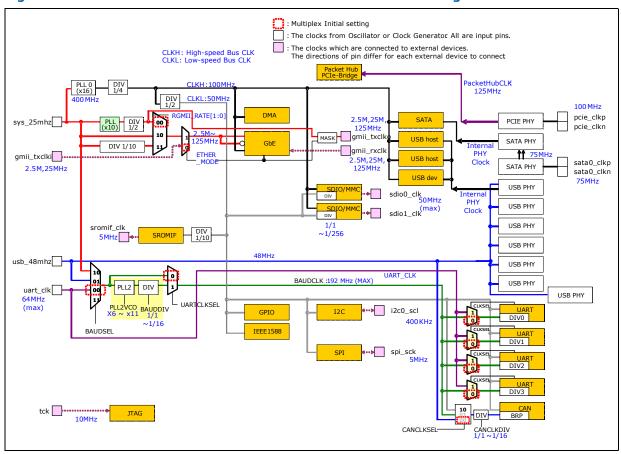

| 5.0 | Clock           | (S                                                      |                                                                        |                                                       | 123                                           |  |  |

|     | 5.1             | Overvi                                                  | ew                                                                     |                                                       | 123                                           |  |  |

|     | 5.2             |                                                         |                                                                        | l                                                     |                                               |  |  |

|     | 5.3             |                                                         |                                                                        | ram                                                   |                                               |  |  |

|     | 5.4             |                                                         |                                                                        |                                                       |                                               |  |  |

|     | J. <del>4</del> |                                                         |                                                                        |                                                       |                                               |  |  |

|     |                 | 5.4.1                                                   |                                                                        | Mapped I/O Registers                                  |                                               |  |  |

|     |                 |                                                         | 5.4.1.1                                                                | Clock Configuration Register (CLKCFG)                 |                                               |  |  |

|     | 5.5             |                                                         | onal Descri                                                            | ption                                                 | 126                                           |  |  |

|     |                 | 5.5.1                                                   |                                                                        | Clock                                                 |                                               |  |  |

|     |                 |                                                         | 5.5.1.1                                                                | Packet Hub Clock                                      | 126                                           |  |  |

|     |                 |                                                         | 5.5.1.2                                                                | Internal BUS Clock of Each Function                   |                                               |  |  |

|     |                 | 5.5.2                                                   | Periphera                                                              | al Clock                                              |                                               |  |  |

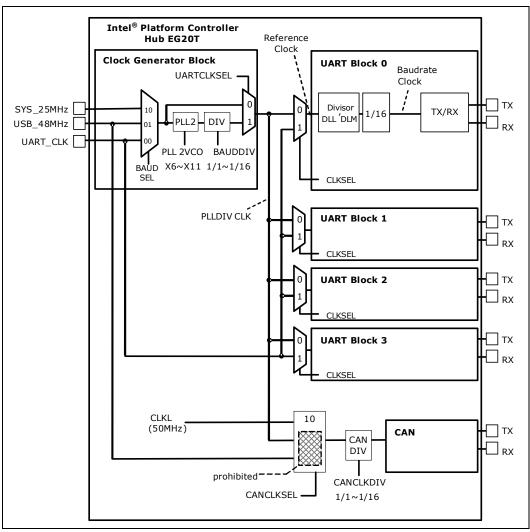

|     |                 |                                                         | 5.5.2.1                                                                | Baud Rate Clock (UART/CAN)                            | 126                                           |  |  |

|     |                 |                                                         | 5.5.2.2                                                                | UART Clock Selection Sequence Without PLL Setting     | 131                                           |  |  |

|     |                 |                                                         | 5.5.2.3                                                                | UART Clock Selection Sequence With PLL Setting        | 131                                           |  |  |

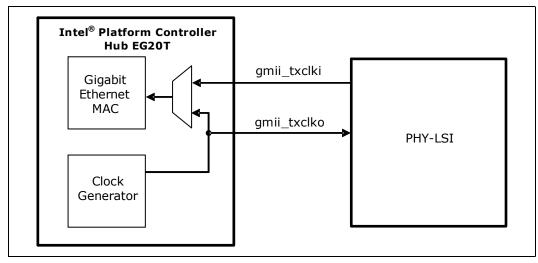

|     |                 |                                                         | 5.5.2.4                                                                | Gigabit Ethernet Transmission Clock Control           | 131                                           |  |  |

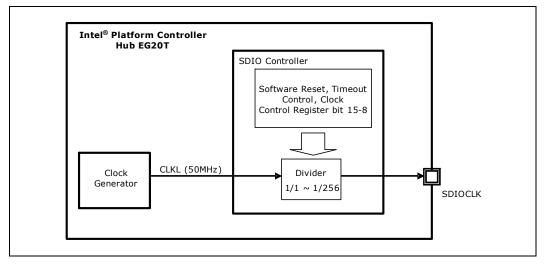

|     |                 |                                                         | 5.5.2.5                                                                | SDIO Clock Control                                    | 132                                           |  |  |

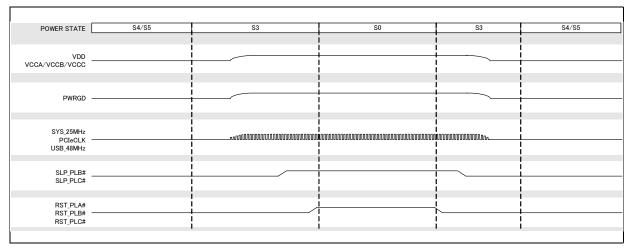

| 6.0 | Dowe            | r Mana                                                  | gement                                                                 |                                                       | 125                                           |  |  |

| 0.0 |                 | _                                                       |                                                                        |                                                       |                                               |  |  |

|     | 6.1             |                                                         |                                                                        |                                                       |                                               |  |  |

|     |                 | 6.1.1                                                   |                                                                        | ription                                               |                                               |  |  |

|     | 6.2             |                                                         |                                                                        | ption                                                 |                                               |  |  |

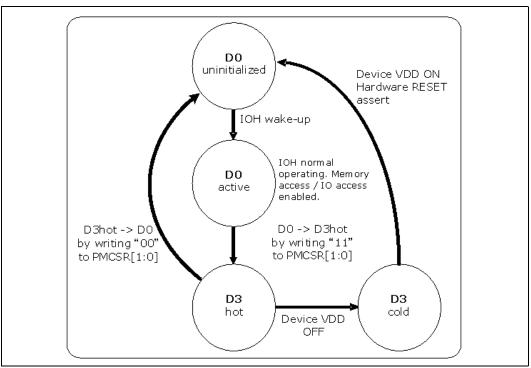

|     |                 | 6.2.1                                                   |                                                                        | tate                                                  |                                               |  |  |

|     |                 |                                                         | 6.2.1.1                                                                | Theory of Operation                                   |                                               |  |  |

|     |                 | 6.2.2                                                   | Sleep Sta                                                              | ates                                                  | 137                                           |  |  |

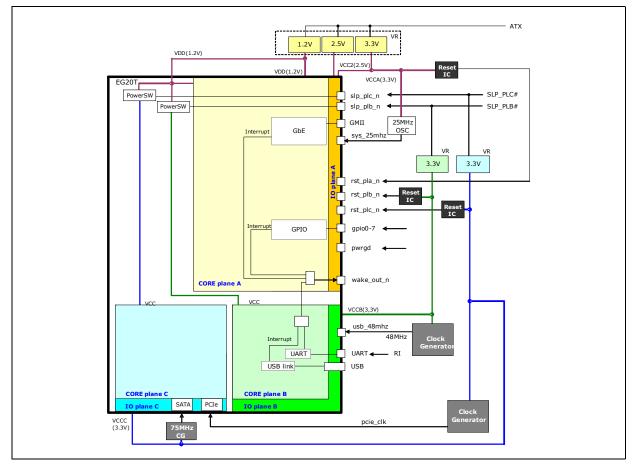

|     |                 |                                                         | 6.2.2.1                                                                | Power Planes                                          | 137                                           |  |  |

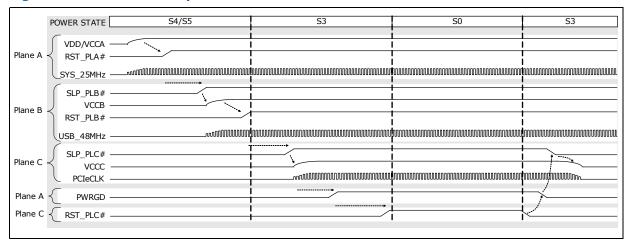

|     |                 |                                                         | 6.2.2.2                                                                | Power Sequence with Wake-up Function                  |                                               |  |  |

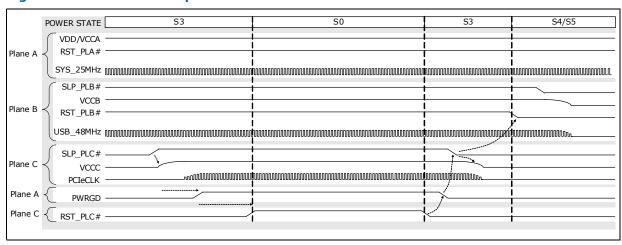

|     |                 |                                                         |                                                                        | Power Sequence with no Wake-up Function               |                                               |  |  |

|     |                 |                                                         | 6.2.2.3                                                                | Power Sequence with no wake-up runction               | ±JJ                                           |  |  |

|     |                 |                                                         |                                                                        | Wake-Up Event                                         | 140                                           |  |  |

|     |                 |                                                         |                                                                        | Wake-Up Event                                         | 140                                           |  |  |

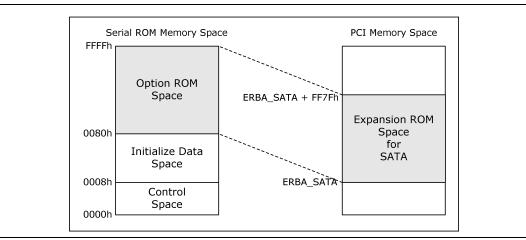

| 7.0 | SATA            |                                                         | 6.2.2.4<br>6.2.2.5                                                     | Wake-Up Event<br>Hardware and Software Operation      | 140<br>141                                    |  |  |

| 7.0 |                 |                                                         | 6.2.2.4<br>6.2.2.5                                                     | Wake-Up Event                                         | 140<br>141<br>143                             |  |  |

| 7.0 | 7.1             | Overvi                                                  | 6.2.2.4<br>6.2.2.5<br>ew                                               | Wake-Up EventHardware and Software Operation          | 140<br>141<br>143<br>143                      |  |  |

| 7.0 |                 | Overvi<br>Registe                                       | 6.2.2.4<br>6.2.2.5<br>ewer Address                                     | Wake-Up Event                                         | 140<br>141<br>143<br>143                      |  |  |

| 7.0 | 7.1             | Overvi<br>Registe<br>7.2.1                              | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf                         | Wake-Up Event                                         | 140<br>141<br>143<br>143<br>143               |  |  |

| 7.0 | 7.1             | Overvi<br>Registe<br>7.2.1<br>7.2.2                     | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf<br>I/O Regis            | Wake-Up Event                                         | 140<br>141<br>143<br>143<br>143               |  |  |

| 7.0 | 7.1             | Overvi<br>Registe<br>7.2.1                              | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf<br>I/O Regis            | Wake-Up Event                                         | 140<br>141<br>143<br>143<br>143               |  |  |

| 7.0 | 7.1             | Overvi<br>Registe<br>7.2.1<br>7.2.2<br>7.2.3            | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf<br>I/O Regis<br>Memory- | Wake-Up Event                                         | 140<br>141<br>143<br>143<br>144<br>144        |  |  |

| 7.0 | 7.1<br>7.2      | Overvi<br>Registe<br>7.2.1<br>7.2.2<br>7.2.3            | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf<br>I/O Regis<br>Memory- | Wake-Up Event                                         | 140<br>141<br>143<br>143<br>144<br>144        |  |  |

| 7.0 | 7.1<br>7.2      | Overvi<br>Registe<br>7.2.1<br>7.2.2<br>7.2.3<br>Registe | ewer Address PCI Conf I/O Regis Memory-ers                             | Wake-Up Event                                         | 140<br>143<br>143<br>143<br>144<br>144<br>146 |  |  |

| 7.0 | 7.1<br>7.2      | Overvi<br>Registe<br>7.2.1<br>7.2.2<br>7.2.3<br>Registe | 6.2.2.4<br>6.2.2.5<br>ewer Address<br>PCI Conf<br>I/O Regis<br>Memory- | Wake-Up Event                                         | 140 143 143 143 144 144 146 146               |  |  |

| 7.0 | 7.1<br>7.2      | Overvi<br>Registe<br>7.2.1<br>7.2.2<br>7.2.3<br>Registe | ewer Address PCI Conf I/O Regis Memory- ers PCI Conf 7.3.1.1           | Wake-Up Event                                         | 140 143 143 143 144 144 146 146               |  |  |

|       | 7.3.1.5              | RID— Revision Identification Register                                   | 148        |

|-------|----------------------|-------------------------------------------------------------------------|------------|

|       | 7.3.1.6              | CC— Class Code Register                                                 | 149        |

|       | 7.3.1.7              | MLT— Master Latency Timer Register                                      | 149        |

|       | 7.3.1.8              | HEADTYP— Header Type Register                                           |            |

|       | 7.3.1.9              | IO_BASE— I/O Base Address Register                                      | 150        |

|       | 7.3.1.10             | MEM_BASE— MEM Base Address Register                                     | 150        |

|       | 7.3.1.11             | SSVID— Subsystem Vendor ID Register                                     | 150        |

|       | 7.3.1.12             | SSID— Subsystem ID Register                                             |            |

|       |                      | ROM_BASE— Extended ROM Base Address Register                            | 151        |

|       | 7.3.1.13             |                                                                         |            |

|       | 7.3.1.14             | CAP_PTR— Capabilities Pointer Register                                  |            |

|       | 7.3.1.15             | INT_LN— Interrupt Line Register                                         |            |

|       | 7.3.1.16             | INT_PN— Interrupt Pin Register                                          | 152        |

|       | 7.3.1.17             | MSI_CAPID—MSI Capability ID Register                                    | 152        |

|       | 7.3.1.18             | MSI_NPR—MSI Next Item Pointer Register                                  | 152        |

|       | 7.3.1.19             | MSI_MCR—MSI Message Control Register                                    | 152        |

|       | 7.3.1.20             | MSI_MAR—MSI Message Address Register                                    | 153        |

|       | 7.3.1.21             | MSI_MD—MSI Message Data Register                                        | 153        |

|       | 7.3.1.22             | PM_CAPID—PCI Power Management Capability ID Register                    | 154        |

|       | 7.3.1.23             | PM_NPR—PM Next Item Pointer Register                                    |            |

|       | 7.3.1.24             | PM_CAP—Power Management Capabilities Register                           | 154        |

|       | 7.3.1.25             | PWR_CNTL_STS—Power Management Control/Status Register                   | 155        |

|       |                      | CATA CARID CATA Canability ID Posistor                                  | 155        |

|       | 7.3.1.26             | SATA_CAPID—SATA Capability ID Register                                  | 155        |

|       | 7.3.1.27             | SATA_NPR—SATA Next Item Pointer Register                                | 156        |

|       | 7.3.1.28             | SATA_MAJREV_MINREV—Major Revision Number and Minor                      |            |

|       |                      | Revision Number of the SATA Capability Pointer Register                 | 156        |

|       | 7.3.1.29             | SATA_BAROFST_BARLOC—SATA BAR Offset and BAR Location                    |            |

|       |                      | Register                                                                | 156        |

| 7.3.2 | I/O Regis            | sters                                                                   | 157        |

|       | 7.3.2.1              | AHCI Index Register                                                     |            |

|       | 7.3.2.2              | AHCI Index Register                                                     | 150        |

| 7 2 2 |                      |                                                                         |            |

| 7.3.3 |                      | Mapped I/O Registers (BAR: MEM_BASE)                                    | 158        |

|       | 7.3.3.1              | HBA Capabilities Register                                               | 158        |

|       | 7.3.3.2              | Global HBA Control Register                                             | 159        |

|       | 7.3.3.3              | Interrupt Status Register                                               | 160        |

|       | 7.3.3.4              | Ports Implemented Register                                              | 161        |

|       | 7.3.3.5              | AHCI Version Register                                                   | 161        |

|       | 7.3.3.6              | Command Completion Coalescing Control                                   | 161        |

|       | 7.3.3.7              | Command Completion Coalescing Ports                                     | 162        |

|       | 7.3.3.8              | BIST Activate FIS Register                                              | 163        |

|       | 7.3.3.9              | BIST Control Register                                                   |            |

|       | 7.3.3.10             | BIST FIS Count Register                                                 |            |

|       | 7.3.3.10             | BIST Status Register                                                    | 166        |

|       | 7.3.3.11             | BIST DWORD Error Count Register                                         | 167        |

|       |                      |                                                                         |            |

|       | 7.3.3.13             | OOB Register                                                            | 16/        |

|       |                      | Timer 1 ms Register                                                     |            |

|       | 7.3.3.15             | Global Parameter 1 Register                                             |            |

|       | 7.3.3.16             | Global Parameter 2 Register                                             |            |

|       | 7.3.3.17             | Port Parameter Register                                                 |            |

|       | 7.3.3.18             | Test Register                                                           | 171        |

|       | 7.3.3.19             | Version Register                                                        | 172        |

|       | 7.3.3.20             | ID Register                                                             |            |

|       | 7.3.3.21             | Port# Command List Base Address Register (P#CLB)                        | 173        |

|       | 7.3.3.22             | Port# Command List Base Address Upper 32-Bits Register                  | , 5        |

|       | , .5.5.22            |                                                                         | 172        |

|       | 7.3.3.23             | (P#CLBU)                                                                | 17/        |

|       |                      | Port # FIC Race Address Upper 22 Pite Register (P#EDL)                  | エノケ<br>1フォ |

|       | 7.3.3.24             | Port# FIS Base Address Upper 32-Bits Register (P#FBU)                   | 1/4        |

|       | 7.3.3.25             | Port# Interrupt Status Register (P#IS)                                  | 1/4        |

|       | 7.3.3.26             | Port# Interrupt Enable Register (P#IE)                                  |            |

|       |                      |                                                                         |            |

|       | 7.3.3.27<br>7.3.3.28 | Port# Command Register (P#CMD)<br>Port# Task File Data Register (P#TFD) | 178        |

Intel<sup>®</sup> Platform Controller Hub EG20T Datasheet 6

Downloaded from Arrow.com.

|     |            |            | 7.3.3.29   | Port# Signature Register (P#SIG)                      | 183        |

|-----|------------|------------|------------|-------------------------------------------------------|------------|

|     |            |            | 7.3.3.30   | Port# Serial ATA Status {SStatus} Register (P#SSTS)   | 183        |

|     |            |            | 7.3.3.31   | Port# Serial ATA Control {SControl} Register (P#SCTL) | 184        |

|     |            |            | 7.3.3.32   | Port# Serial ATA Error {SError} Register (P#SERR)     | 185        |

|     |            |            | 7.3.3.33   | Port# Serial ATA Active {SActive} Register (P#SACT)   | 188        |

|     |            |            | 7.3.3.34   | Port# Command Issue Register (P#CI)                   | 188        |

|     |            |            | 7.3.3.35   | Port# Serial ATA Notification Register (P#SNTF)       | 188        |

|     |            |            | 7.3.3.36   | Port# DMA Control Register (P#DMACR)                  | 180        |

|     |            |            | 7.3.3.37   | Port# PHY Control Register (P#PHYCR)                  | 101        |

|     |            |            | 7.3.3.38   | Port# PHY Status Register (P#PHYSR)                   | 101        |

|     |            |            |            |                                                       |            |

|     |            |            | 7.3.3.39   | Test Register 2 (TESTR2)                              | 191        |

|     |            |            | 7.3.3.40   | PHY SOFT RESET Register (PSRST)                       |            |

|     | 7.4        | Functio    |            | otion                                                 |            |

|     |            | 7.4.1      | Operation  | n Details                                             | 192        |

|     |            |            | 7.4.1.1    | Data Transfer                                         |            |

|     |            |            | 7.4.1.2    | Power Management                                      |            |

|     |            |            | 7.4.1.3    | Port Multiplier Support                               | 195        |

|     |            |            | 7.4.1.4    | Interrupts                                            |            |

|     |            |            | 7.4.1.5    | PHY and Link Control                                  | 106        |

|     |            |            | _          |                                                       |            |

|     |            |            | 7.4.1.6    | Reset Conditions                                      |            |

|     |            |            | 7.4.1.7    | Interface Speed Support                               |            |

|     |            |            | 7.4.1.8    | Staggered Spin-up                                     | 198        |

|     |            |            | 7.4.1.9    | Activity LED                                          |            |

|     |            |            | 7.4.1.10   | Asynchronous Notification                             | 199        |

|     |            |            | 7.4.1.11   | BIST Operation                                        | 199        |

|     |            |            | 7.4.1.12   |                                                       | 202        |

|     |            | 7.4.2      | Programn   | ning                                                  |            |

|     |            | , <u> </u> | 7.4.2.1    | Software Initialization                               | 203        |

|     |            |            | 7.4.2.2    | Software Manipulation of Port DMA                     | 203        |

|     | <b>7</b> F | O-4:       |            |                                                       |            |

|     | 7.5        |            |            |                                                       |            |

|     | 7.6        | Legacy     |            |                                                       |            |

|     |            | 7.6.1      | Legacy M   | ode Support                                           | 206        |

|     | 7.7        | Addition   |            | ations                                                |            |

|     |            | 7.7.1      |            | ability with SATA Gen1 Device                         |            |

|     |            | 7.7.2      |            | Setting for Outputting BIST Patterns                  |            |

|     |            | 1.7.2      | Audi ess s | setting for Outputting bist Patterns                  | 200        |

| 8.0 | USB I      | lost Co    | ntroller   |                                                       | 209        |

|     | 8.1        |            |            |                                                       |            |

|     |            |            |            |                                                       |            |

|     | 8.2        | _          |            | Map                                                   |            |

|     |            | 8.2.1      |            | guration Registers                                    |            |

|     |            | 8.2.2      | Memory-I   | Mapped I/O Registers (BAR: MEM_BASE)                  | 211        |

|     |            |            | 8.2.2.1    | EHCI Registers                                        |            |

|     |            |            | 8.2.2.2    | OHCI Registers                                        |            |

|     | 8.3        | Dogisto    |            |                                                       |            |

|     | 0.5        |            |            |                                                       |            |

|     |            | 8.3.1      |            | guration Registers                                    |            |

|     |            |            | 8.3.1.1    | VID— Vendor Identification Register                   | 213        |

|     |            |            | 8.3.1.2    | DID— Device Identification Register                   | 213        |

|     |            |            | 8.3.1.3    | PCICMD— PCI Command Register                          | 213        |

|     |            |            | 8.3.1.4    | PCISTS—PCI Status Register                            | 214        |

|     |            |            | 8.3.1.5    | RID— Revision Identification Register                 | 215        |

|     |            |            | 8.3.1.6    | CC— Class Code Register                               |            |

|     |            |            | 8.3.1.7    | MLT— Master Latency Timer Register                    |            |

|     |            |            | 8.3.1.8    | HEADTYP— Header Type Register                         |            |

|     |            |            | 8.3.1.9    | SSVID— Subsystem Vendor ID Register                   | 217        |

|     |            |            | 8.3.1.10   | SSVID— Subsystem Vendor ID Register                   | 21/<br>210 |

|     |            |            |            |                                                       |            |

|     |            |            | 8.3.1.11   | SSID— Subsystem ID Register                           | 710        |

|     |            |            | 8.3.1.12   | CAP_PTR— Capabilities Pointer Register                |            |

|     |            |            | 8.3.1.13   | INT_LN— Interrupt Line Register                       | 718        |

|       |       |         |                      | INT_PN— Interrupt Pin Register                                                                                       |       |

|-------|-------|---------|----------------------|----------------------------------------------------------------------------------------------------------------------|-------|

|       |       |         | 8.3.1.15             | MSI_CAPID—MSI Capability ID Register                                                                                 | . 219 |

|       |       |         | 8.3.1.16             | MSI_NPR—MSI Next Item Pointer Register                                                                               | .219  |

|       |       |         | 8.3.1.17             | MSI_MCR—MSI Message Control Register                                                                                 | . 220 |

|       |       |         | 8.3.1.18             | MSI_MAR—MSI Message Address Register                                                                                 | 220   |

|       |       |         | 8.3.1.19<br>8.3.1.20 | MSI_MD—MSI Message Data Register PM_CAPID—PCI Power Management Capability ID Register                                | 220   |

|       |       |         | 8.3.1.21             | PM_PTR—PM Next Item Pointer Register                                                                                 |       |

|       |       |         | 8.3.1.22             | PM_CAP—Power Management Capabilities Register                                                                        | 221   |

|       |       |         |                      | PWR_CNTL_STS—Power Management Control/Status Register                                                                |       |

|       |       |         | 8.3.1.24             | SBRN—Serial Bus Release Number Register                                                                              |       |

|       |       |         |                      | FLADJH— Frame Length Adjustment Register for Host Controller                                                         | 223   |

|       |       |         |                      | FLADJH— Frame Length Adjustment Register for PORT                                                                    |       |

|       |       |         | 8.3.1.27             | USBLEGSUP—USB Legacy Support EHCI Extended Capability                                                                |       |

|       |       |         |                      | Register                                                                                                             | 225   |

|       |       |         |                      | USBLEGCTLSTS— USB Legacy Support Control/Status Register                                                             |       |

|       |       | 8.3.2   | EHCI Reg             | isters (BAR: MEM_BASE)                                                                                               | . 227 |

|       |       |         | 8.3.2.1              | HCCAPBASE - Capability Register                                                                                      | . 227 |

|       |       |         | 8.3.2.2              | HCSPARAMS - Structural Parameter Register                                                                            |       |

|       |       |         | 8.3.2.3              | HCCPARAMS - Capability Parameter Register                                                                            | 228   |

|       |       |         | 8.3.2.4              | USBCMD - USB Command Register                                                                                        | . 229 |

|       |       |         | 8.3.2.5              | USBSTS - USB Status Register                                                                                         | . 231 |

|       |       |         | 8.3.2.6              | USBINTR - USB Interrupt Enable Register                                                                              | . 232 |

|       |       |         | 8.3.2.7              | FRINDEX - Frame Index Register                                                                                       | 233   |

|       |       |         | 8.3.2.8<br>8.3.2.9   | CTRLDSSEGMENT - Control Data Structure Segment Register PERIODICLISTBASE - Periodic Frame List Base Address Register |       |

|       |       |         | 8.3.2.10             | ASYNCLISTADDR - Current Asynchronous List Address Register                                                           |       |

|       |       |         | 8.3.2.11             | CONFIGELAG - Configure Flag Register                                                                                 |       |

|       |       |         | 8.3.2.12             | PORTSC_n - Port Status and Control Register                                                                          | 235   |

|       |       |         | 8.3.2.13             | Debug01 Register (Test Register)                                                                                     | 240   |

|       |       |         | 8.3.2.14             | PHY SOFT RESET Register (PSRST)                                                                                      | 241   |

|       |       | 8.3.3   |                      | gisters (BAR: MEM_BASE)                                                                                              | 242   |

|       |       |         | 8.3.3.1              | HcRevision Register                                                                                                  |       |

|       |       |         | 8.3.3.2              | HcControl Register                                                                                                   | 242   |

|       |       |         | 8.3.3.3              | HcCommandStatus Register                                                                                             | 244   |

|       |       |         | 8.3.3.4              | HcInterruptStatus Register                                                                                           | . 245 |

|       |       |         | 8.3.3.5              | HcInterruptEnable Register                                                                                           | 246   |

|       |       |         | 8.3.3.6              | HcInterruptDisable Register                                                                                          | 246   |

|       |       |         | 8.3.3.7              | HcHCCA Register                                                                                                      | . 247 |

|       |       |         | 8.3.3.8              | HcPeriodCurrentED Register                                                                                           |       |

|       |       |         | 8.3.3.9              | HcControlHeadED Register                                                                                             | 248   |

|       |       |         | 8.3.3.10<br>8.3.3.11 | HcControlCurrentED Register                                                                                          | 249   |

|       |       |         | 8.3.3.12             | HcBulkCurrentED Register                                                                                             |       |

|       |       |         |                      | HcDoneHead Register                                                                                                  | 250   |

|       |       |         | 8 3 3 14             | HcFmInterval Register                                                                                                | 251   |

|       |       |         |                      | HcFmRemaining Register                                                                                               |       |

|       |       |         |                      | HcFmNumber Register                                                                                                  |       |

|       |       |         |                      | HcPeriodicStart Register                                                                                             |       |

|       |       |         |                      | HcLSThreshold Register                                                                                               |       |

|       |       |         | 8.3.3.19             | HcRhDescriptorA Register                                                                                             | 253   |

|       |       |         | 8.3.3.20             | HcRhDescriptorB Register                                                                                             | 254   |

|       |       |         | 8.3.3.21             | HcRhStatus Register                                                                                                  | . 255 |

|       |       |         | 8.3.3.22             | HcRhPortStatus[1:NDP] Register (NDP=1,2,3)                                                                           |       |

|       | 8.4   | Functio |                      | otion                                                                                                                |       |

|       |       | 8.4.1   | Legacy D             | evice Support                                                                                                        | . 259 |

|       | 8.5   | Additio |                      | ations                                                                                                               |       |

|       |       | 8.5.1   | Remote V             | Vake-Up by Port 0 and Port 1                                                                                         | . 260 |

| 9.0   | USB I | Device  |                      |                                                                                                                      | 261   |

| J . U |       |         |                      | ***************************************                                                                              |       |

Intel<sup>®</sup> Platform Controller Hub EG20T Datasheet 8

|      | 9.2  | Registe | r Address I | Map                                                   | 261 |

|------|------|---------|-------------|-------------------------------------------------------|-----|

|      |      | 9.2.1   | PCI Confid  | guration Registers                                    | 261 |

|      |      | 9.2.2   | Memory-N    | Mapped I/O Registers (BAR: MEM_BASE)                  | 262 |

|      |      |         |             | Command and Status Register Memory Map                |     |

|      | 9.3  | Registe | rs          |                                                       | 265 |

|      |      | 9.3.1   | Control ar  | nd Status Registers                                   | 265 |

|      |      |         | 9.3.1.1     | PCI Configuration Registers                           |     |

|      |      |         | 9.3.1.2     | Memory-Mapped I/O Registers (BAR: MEM_BASE)           | 273 |

|      | 9.4  | Functio | nal Descrir | otion                                                 |     |

|      |      | 9.4.1   |             | Operation                                             |     |

|      |      | 51 112  | 9.4.1.1     | Overview                                              |     |

|      |      |         | 9.4.1.2     | DMA Mode                                              |     |

|      |      |         | 9.4.1.3     | Slave-Only Mode                                       |     |

|      | 9.5  | Additio |             | ations                                                |     |

|      |      | 9.5.1   | Wake On     | Function is Not Supported                             | 301 |

|      |      | 9.5.2   |             | g/Plug                                                |     |

|      |      | 9.5.3   |             | of Endpoint Interrupt Register and Mask Register      |     |

|      |      | 9.5.4   |             | ce DMA Operation                                      |     |

|      |      | 3.3.    | 9.5.4.1     | SETUP Data Memory Structure                           |     |

|      |      |         | 9.5.4.2     | OUT Data Memory Structure                             | 30  |

|      |      |         | 9.5.4.3     | IN Data Memory Structure                              |     |

|      | a: . |         |             | •                                                     |     |

| 10.0 | _    |         |             |                                                       |     |

|      |      |         |             |                                                       |     |

|      |      |         |             |                                                       |     |

|      | 10.3 |         |             | Map                                                   |     |

|      |      |         |             | guration Registers                                    |     |

|      |      | 10.3.2  | I/O Regist  | ters                                                  | 312 |

|      |      |         |             | Mapped I/O Registers (BAR: MEM_BASE)                  |     |

|      | 10.4 |         |             |                                                       |     |

|      |      | 10.4.1  |             | guration Registers                                    |     |

|      |      |         | 10.4.1.1    | VID— Vendor Identification Register                   | 315 |

|      |      |         | 10.4.1.2    | DID— Device Identification Register                   | 315 |

|      |      |         | 10.4.1.3    | PCICMD— PCI Command Register                          | 315 |

|      |      |         | 10.4.1.4    | PCISTS—PCI Status Register                            | 317 |

|      |      |         |             | CC— Class Code Register                               |     |

|      |      |         | 10.4.1.0    | MLT— Master Latency Timer Register                    | 318 |

|      |      |         | 10.4.1.8    | HEADTYP— Header Type Register                         | 318 |

|      |      |         | 10.4.1.9    | IO_BASE— IO Base Address Register                     | 318 |

|      |      |         | 10.4.1.10   | MEM_BASE— MEM Base Address Register                   | 319 |

|      |      |         | 10.4.1.11   | SSVID— Subsystem Vendor ID Register                   | 319 |

|      |      |         |             | SSID— Subsystem ID Register                           |     |

|      |      |         |             | CAP_PTR— Capabilities Pointer Register                |     |

|      |      |         | 10.4.1.14   | INT_LN— Interrupt Line Register                       | 320 |

|      |      |         |             | INT_PN— Interrupt Pin Register                        |     |

|      |      |         | 10.4.1.16   | MSI_CAPID—MSI Capability ID Register                  | 320 |

|      |      |         |             | MSI_NPR—MSI Next Item Pointer Register                |     |

|      |      |         | 10.4.1.18   | MSI_MCR—MSI Message Control Register                  | 321 |

|      |      |         | 10.4.1.19   | MSI_MD—MSI Message Data Register                      | 327 |

|      |      |         | 10.7.1.20   | PM_CAPID—PCI Power Management Capability ID Register  | 322 |

|      |      |         |             | PM_NPR—PM Next Item Pointer Register                  |     |

|      |      |         | 10.4.1.23   | PM_CAP—Power Management Capabilities Register         | 323 |

|      |      |         |             | PWR_CNTL_STS—Power Management Control/Status Register |     |

|      |      | 10.4.2  |             | I/O Registers                                         |     |

|      |      |         |             | Ether MAC Index Pagister                              | 32/ |

|      |         | 10.4.2.2 Ether MAC Index Data Register      | 324   |

|------|---------|---------------------------------------------|-------|

|      | 10 4 3  | Memory-Mapped I/O Registers (BAR: MEM_BASE) | 325   |

|      | 10.1.5  | 10.4.3.1 Interrupt Status                   |       |

|      |         | 10.4.3.2 Interrupt Status Hold              |       |

|      |         | 10.4.3.3 Interrupt Enable                   |       |

|      |         | 10.4.3.4 PHY Interrupt Control Register     | 329   |

|      |         | 10.4.3.5 Mode                               | . 329 |

|      |         | 10.4.3.6 Reset                              | . 330 |

|      |         | 10.4.3.7 TCP/IP Accelerator Control         |       |

|      |         | 10.4.3.8 External List                      |       |

|      |         | 10.4.3.9 MAC RX Enable                      |       |

|      |         | 10.4.3.10 RX Flow Control                   |       |

|      |         | 10.4.3.11 Pause Packet Request              |       |

|      |         | 10.4.3.12 RX Mode                           |       |

|      |         | 10.4.3.14 RX FIFO Status                    |       |

|      |         | 10.4.3.15 TX FIFO Status                    |       |

|      |         | 10.3.2.16 Test0                             |       |

|      |         | 10.3.2.17 Test1                             |       |

|      |         | 10.3.2.18 Pause Packet1                     |       |

|      |         | 10.3.2.19 Pause Packet2                     |       |

|      |         | 10.3.2.20 Pause Packet3                     |       |

|      |         | 10.3.2.21 Pause Packet4                     |       |

|      |         | 10.3.2.22 Pause Packet5                     |       |

|      |         | 10.3.2.23 MAC Address                       |       |

|      |         | 10.3.2.24 Address Mask                      |       |

|      |         | 10.3.2.25 MIM                               | .340  |

|      |         | 10.3.2.26 MAC Address1 Load                 |       |

|      |         | 10.3.2.27 RGMII Status                      |       |

|      |         | 10.3.2.28 RGMII Control                     |       |

|      |         | 10.3.2.30 RX Descriptor Base Address        |       |

|      |         | 10.3.2.31 RX Descriptor Size                |       |

|      |         | 10.3.2.32 RX Descriptor Hard Pointer        |       |

|      |         | 10.3.2.33 RX Descriptor Hard Pointer Hold   | 344   |

|      |         | 10.3.2.34 RX Descriptor Soft Pointer        | 344   |

|      |         | 10.3.2.35 TX Descriptor Base Address        | 344   |

|      |         | 10.3.2.36 TX Descriptor Size                |       |

|      |         | 10.3.2.37 TX Descriptor Hard Pointer        | 345   |

|      |         | 10.3.2.38 TX Descriptor Hard Pointer Hold   | . 345 |

|      |         | 10.3.2.39 TX Descriptor Soft Pointer        |       |

|      |         | 10.3.2.40 Wake-on LAN Status                |       |

|      |         | 10.3.2.41 Wake-on LAN Control               |       |

|      |         | 10.3.2.42 Wake-on LAN Address Mask          |       |

| 10.4 |         |                                             |       |

| 10.4 |         | nal Description                             |       |

|      |         | Descriptor                                  |       |

|      |         | Frame Buffer                                |       |

|      |         | Receive Procedure                           |       |

|      |         | Transmission Procedure                      |       |

|      |         | Booting Procedure                           |       |

|      |         | DMA Termination/Restart Procedure           |       |

|      |         | Reset Operation                             |       |

|      |         | Transmission Clock Control                  |       |

|      |         | MAC Address Filtering                       |       |

|      |         | Wake-on LAN                                 |       |

|      |         | Ethernet Frame Length                       |       |

|      | 10.4.12 | TCP/IP Accelerator                          | .364  |

|      |             | 10.4.12.1 Ethernet Format                                                   |                |

|------|-------------|-----------------------------------------------------------------------------|----------------|

|      |             | 10.4.12.2 PPPoE                                                             | 364            |

|      |             | 10.4.12.3 IPv4                                                              |                |

|      |             | 10.4.12.4 IPv6                                                              |                |

|      |             | 10.4.13 Indirect Access to Memory-Mapped I/O Registers via I/O Space        | 367            |

|      | 10.5        | Additional Clarification 3                                                  |                |

|      | 10.5        | 10.5.1 Compatibility with Intel® Ethernet Products                          | 367            |

|      |             | ·                                                                           |                |

| 11.0 | <b>SDIO</b> |                                                                             | 369            |

|      | 11.1        | Overview                                                                    | 369            |

|      |             | Features                                                                    |                |

|      |             | Register Address Map                                                        |                |

|      | 11.5        |                                                                             |                |

|      |             | 11.3.1 PCI Configuration Registers                                          | 369            |

|      |             | 11.3.2 Memory-Mapped I/O Registers (BAR: MEM_BASE)                          |                |

|      | 11.4        | Registers                                                                   |                |

|      |             | 11.4.1 PCI Configuration Registers                                          |                |

|      |             | 11.4.1.1 VID— Vendor Identification Register 3                              | 371            |

|      |             | 11.4.1.2 DID— Device Identification Register                                | 372            |

|      |             | 11.4.1.3 PCICMD— PCI Command Register                                       | 372            |

|      |             | 11.4.1.4 PCISTS—PCI Status Register                                         | 373            |

|      |             | 11.4.1.5 RID— Revision Identification Register                              | 374            |

|      |             | 11.4.1.6 CC— Class Code Register                                            |                |

|      |             | 11.4.1.7 MLT— Master Latency Timer Register                                 | 374            |

|      |             | 11.4.1.8 HEADTYP— Header Type Register                                      | 375            |

|      |             | 11.4.1.9 MEM_BASE— MEM Base Address Register                                | 375            |

|      |             | 11.4.1.10 SSVID— Subsystem Vendor ID Register                               |                |

|      |             | 11.4.1.11 SSID— Subsystem ID Register                                       | 376            |

|      |             | 11.4.1.12 CAP_PTR— Capabilities Pointer Register                            |                |

|      |             | 11.4.1.13 INT_LN— Interrupt Line Register                                   |                |

|      |             | 11.4.1.14 INT_PN— Interrupt Pin Register                                    | 376            |

|      |             | 11.4.1.15 SLOTINF— Slot Information Register                                | 377            |

|      |             | 11.4.1.16 MSI_CAPID—MSI Capability ID Register                              | 377            |

|      |             | 11.4.1.17 MSI_NPR—MSI Next Item Pointer Register                            | 377            |

|      |             | 11.4.1.18 MSI_MCR—MSI Message Control Register                              | 378            |

|      |             | 11.4.1.19 MSI_MAR—MSI Message Address Register                              | 378            |

|      |             | 11.4.1.20 MSI_MD—MSI Message Data Register                                  | 378            |

|      |             | 11.4.1.21 PM_CAPID—PCI Power Management Capability ID Register              | 379            |

|      |             | 11.4.1.22 PM_NPR—PM Next Item Pointer Register                              |                |

|      |             | 11.4.1.23 PM_CAP—Power Management Capabilities Register                     | 379            |

|      |             | 11.4.1.24 PWR_CNTL_STS—Power Management Control/Status Register 3           | 3,7,5<br>3,8,0 |

|      |             | 11.4.2 Memory-Mapped I/O Registers (BAR: MEM_BASE)                          |                |

|      |             |                                                                             |                |

|      |             | 11.4.2.1 DMA System Address                                                 | 201            |

|      |             | 11.4.2.2 Block Count, Block Size                                            |                |

|      |             | 11.4.2.3 Argument1, 0                                                       | 30Z            |

|      |             | 11.4.2.4 Command Transfer Mode                                              |                |

|      |             | 11.4.2.5 Response1, 0                                                       |                |

|      |             | 11.4.2.6 Response3, 2                                                       |                |

|      |             | 11.4.2.7 Response5, 4                                                       |                |

|      |             | 11.4.2.8 Response7, 6                                                       |                |

|      |             | 11.4.2.9 Buffer Data Port                                                   |                |

|      |             | 11.4.2.10 Present State1, 0                                                 | 387            |

|      |             | 11.4.2.11 Wakeup Control, Block Gap Control, Power Control, Host Control. 3 |                |

|      |             | 11.4.2.12 Software Reset, Timeout Control, Clock Control                    |                |

|      |             | 11.4.2.13 Error Interrupt Status, Normal Interrupt Status                   | 394            |