TPS65983B

ZHCSFL8B -OCTOBER 2016-REVISED JUNE 2018

# TPS65983B USB Type-C 和 USB PD 控制器、电源开关和高速多路复用器

### 1 特性

- USB 供电 (PD) 控制器

- 支持 PD2.0 和 PD3.0 规范。

- 支持快速角色交换

- 提供供电器件(主机)、受电器件(设备)或供 电-受电器件三种模式配置

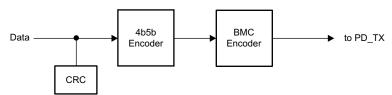

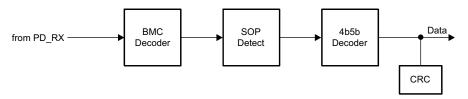

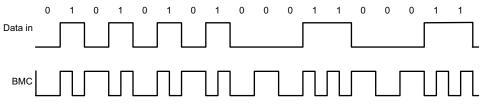

- 双相标记编码/解码 (BMC)

- 物理层和策略引擎

- 可配置为自举控制和主机控制

- 符合 USB Type-C 规范

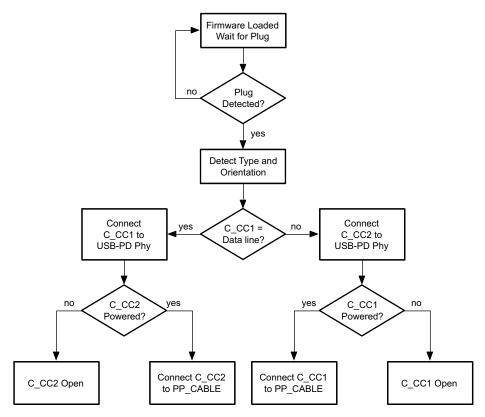

- 电缆方向和角色检测

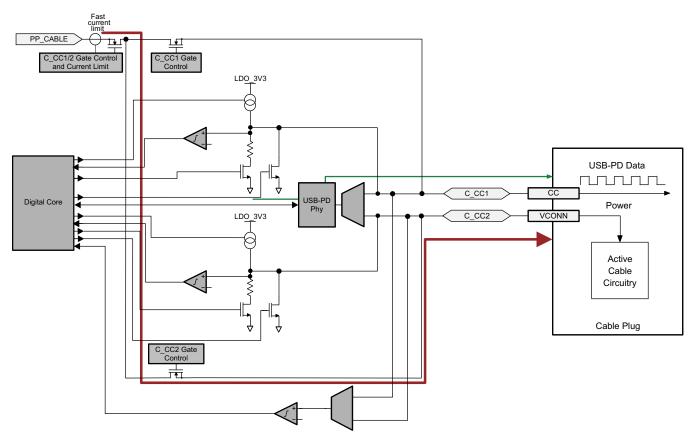

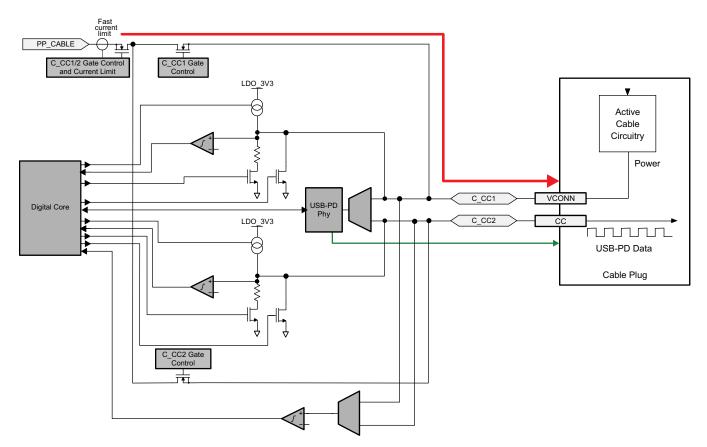

- 分配 CC 和 VCONN 引脚

- 针对 Type-C 电源提供默认值、1.5A 或 3A 三 种电流

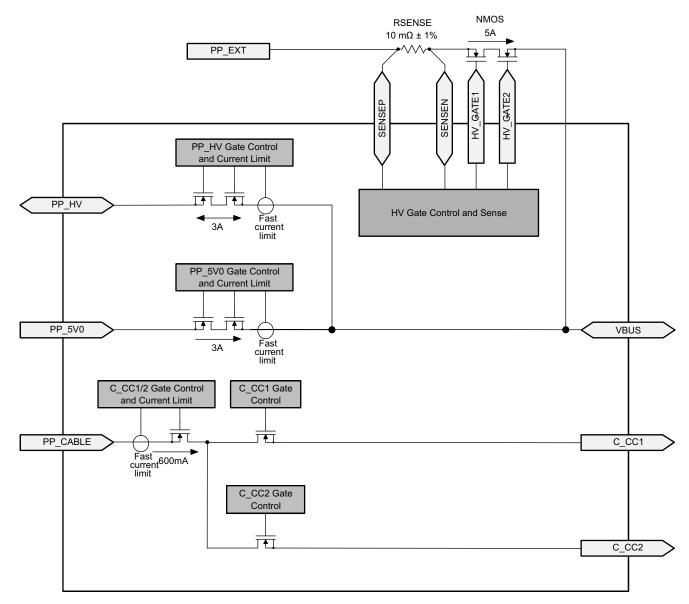

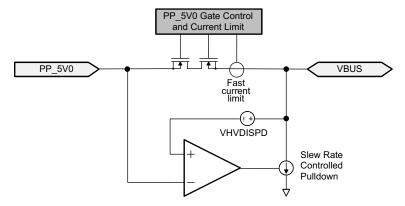

- 端口电源开关

- 5V/3A 开关(Type-C 电源的 VBUS)

- 5V-20V/3A 双向开关(USB PD 电源的 VBUS)

- 5V/600mA 开关 (VCONN)

- 过流限制器,过压保护器

- 转换率控制

- 支持硬复位

- 端口数据多路复用器

- USB 2.0 HS 数据、UART 数据以及低速端点

- 适用于交替模式(DisplayPort 和 Thunderbolt)的 边带使用™数据

#### 电源管理

- 适用于外部 5V-20V/5A 双向开关(背靠背 NFET)的栅极控制和电流感测

- 通过 3.3V 或 VBUS 电源供电

- 3.3V LDO 输出,为电池电量耗尽情况提供支持

- BGA MicroStar Junior 封装和 NFBGA 封装

- 0.5mm 间距

- 通孔对于所有引脚均兼容

### 2 应用

• Thunderbolt 3 设备

### 3 说明

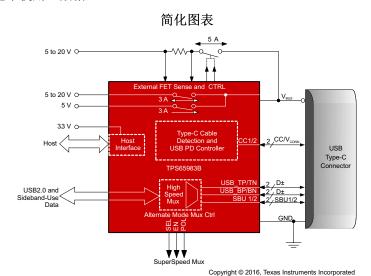

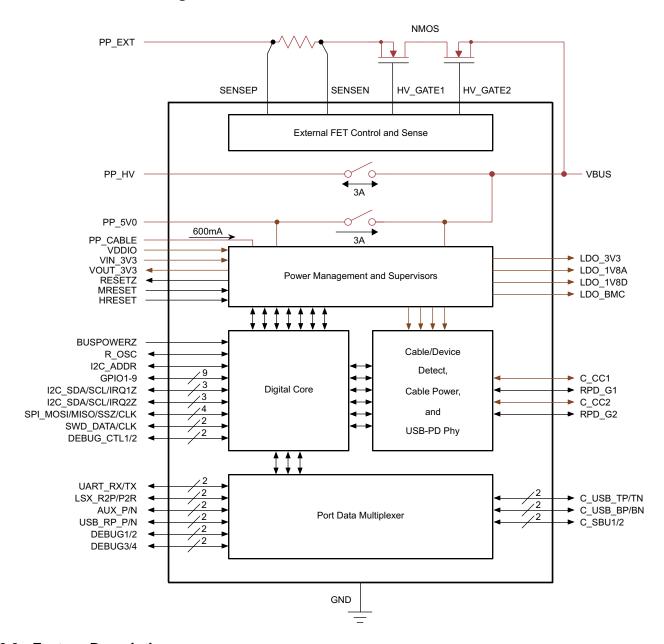

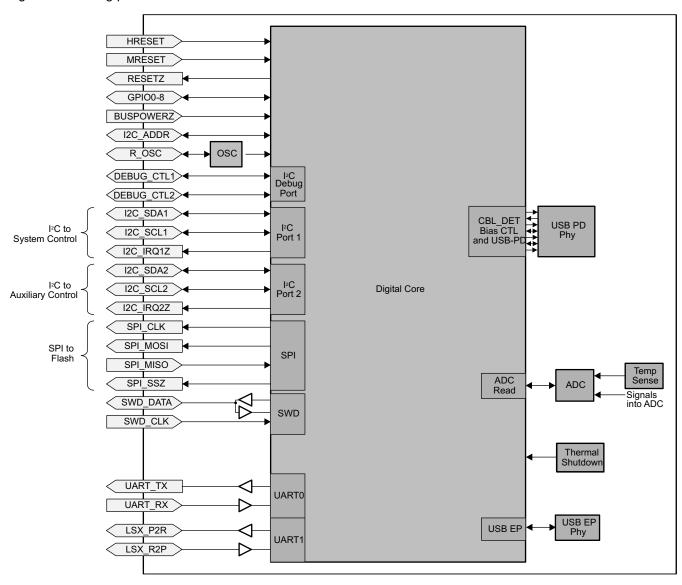

TPS65983B 是一款独立式 USB Type-C 和 USB 供电 (PD) 控制器,可在 USB Type-C 连接器中提供电缆插入状态和方向检测。在电缆检测过程中,TPS65983B 会在 CC 线上使用 USB PD 协议进行相应传输。当完成电缆检测和 USB PD 协商之后,TPS65983B 会使能相应的电源路径,并配置内部和外部(可选)多路复用器的交替模式设置。

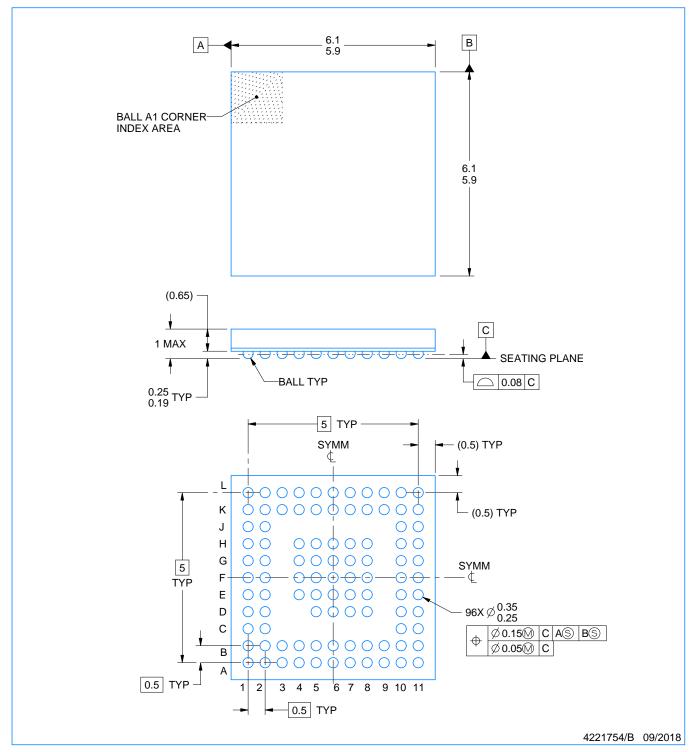

#### 器件信息(1)

| 器件编号      | 封装                        | 封装尺寸 (标称值)      |

|-----------|---------------------------|-----------------|

| TPS65983B | BGA MicroStar Junior (96) | 6.00mm 6.00mm   |

| 1P303963B | NFBGA (96)                | 6.00mm × 6.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

Changes from Original (October 2016) to Revision A

|                                 |                                                                                   | 目录     |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------|-----------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 特性                                                                                | 1<br>1 | 11.1 3.3 V Power       91         11.2 1.8 V Core Power       91         11.3 VDDIO       91         2 Layout       93         12.1 Layout Guidelines       93         12.2 Layout Example       97         3 器件和文档支持       111         13.1 器件支持       111         13.2 文档支持       111         13.3 接收文档更新通知       111         13.4 社区资源       111         13.5 商标       111         13.6 静电放电警告       111         13.7 术语表       111 |

|                                 | 7.20 I <sup>2</sup> C Slave Requirements and Characteristics 22                   | 1      | 4 机械、封装和可订购信息111                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 注: え                            | 多订历史记录<br>之前版本的页码可能与当前版本有所不同。<br>ges from Revision A (October 2016) to Revision B |        | Page                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | -<br>.添加 添加了 NFBGA (ZBH) 封装选项                                                     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**Page**

# 5 (说明(续))

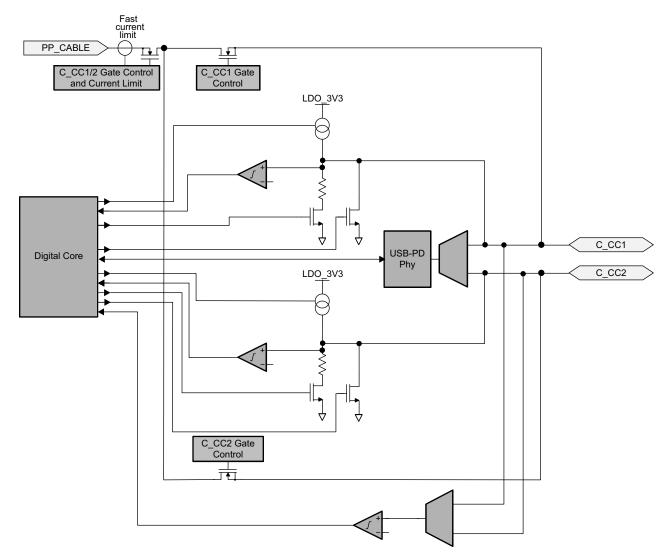

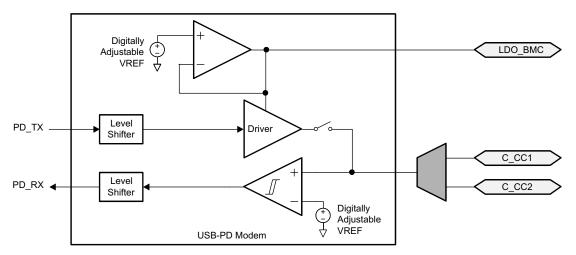

CC 引脚上的混合信号前端可为 Type-C 电源提供默认值 (500mA)、1.5A 或 3A 三种电流、检测电缆插入事件、确定 USB Type-C 电缆方向以及遵循指定的双相标记编码 (BMC) 和物理层 (PHY) 协议自主协商 USB PD 合约。

端口电源开关在 5V 电压下可为传统 USB 电源和 Type-C USB 电源提供高达 3A 的下行电流。当 USB PD 电源用作供电器件(主机)、受电器件(设备)或供电-受电器件时,附加的双向开关路径可在最高 20V 的电压下为其提供高达 3A 的电流。

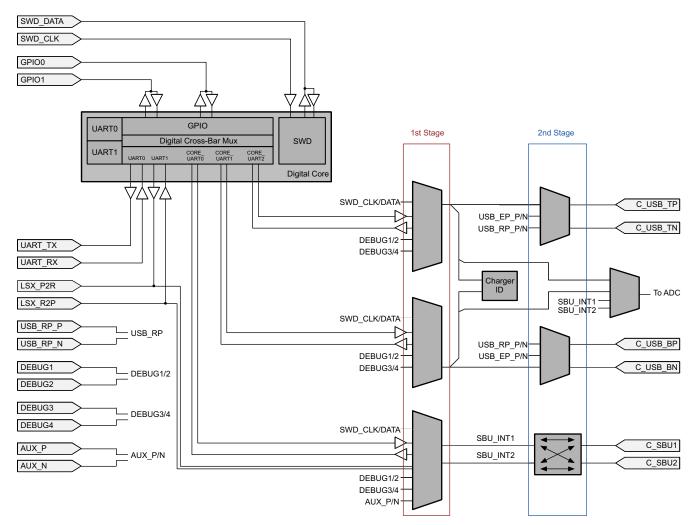

此外,TPS65983B 也可用作上行数据端口 (UFP)、下行数据端口 (DFP) 或者双角色数据端口。端口数据多路复用器可实现端口与顶部或底部 D+/D- 信号对之间的 USB 2.0 HS 数据传输,并且具有一个 USB 2.0 低速端点。此外,还可以将边带使用 (SBU) 信号对用于辅助或交替模式的通信(例如,DisplayPort 或 Thunderbolt)。

电源管理电路使用系统内部的 3.3V 电压供电,同时使用 VBUS 启动并针对电池电量耗尽或无电池情况进行供电协商。

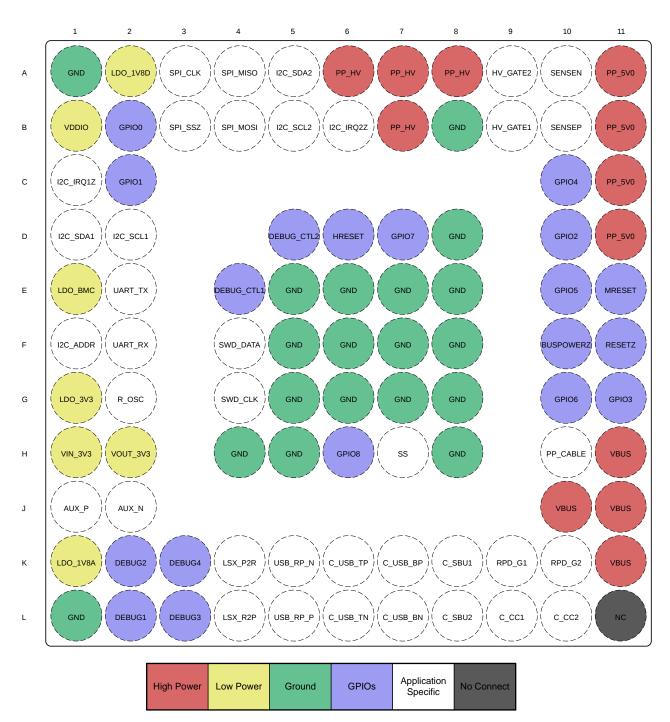

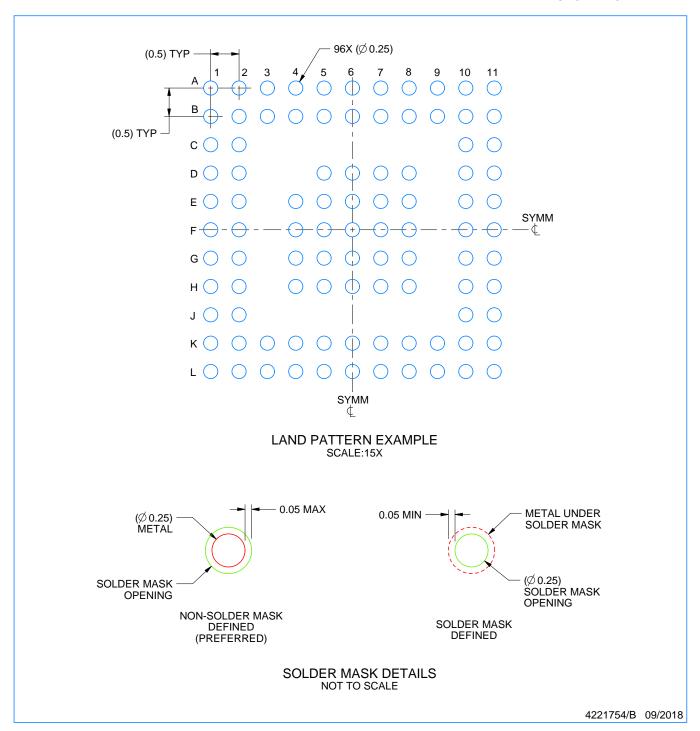

# 6 Pin Configuration and Functions

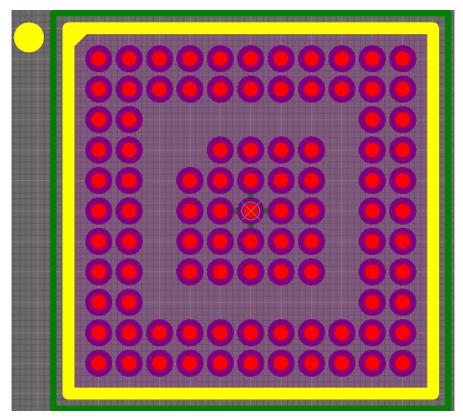

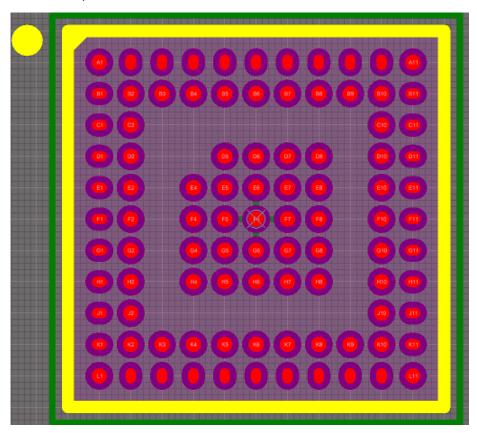

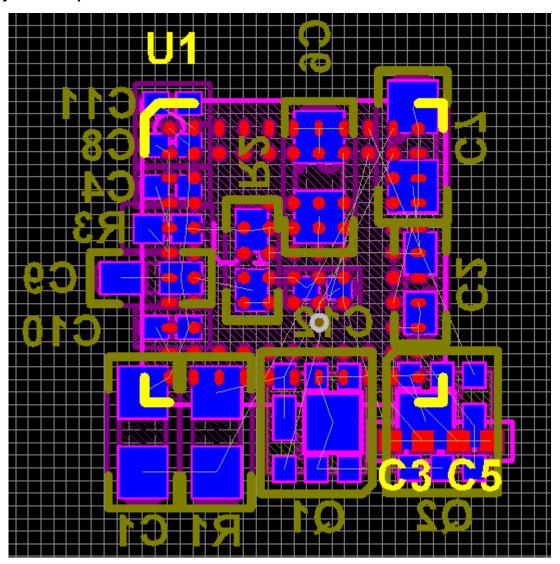

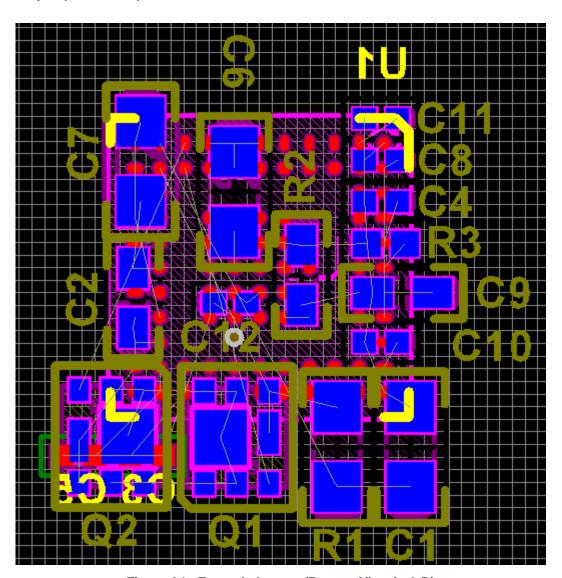

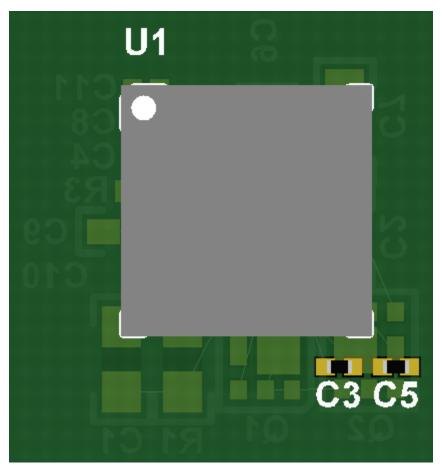

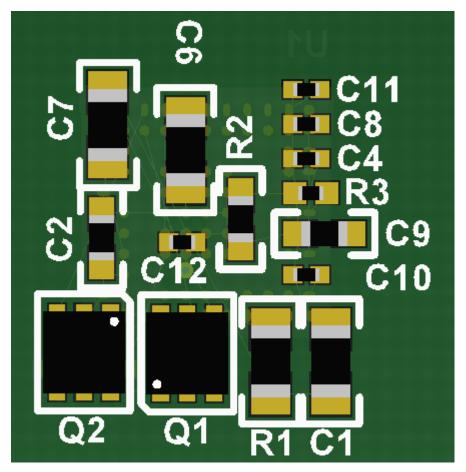

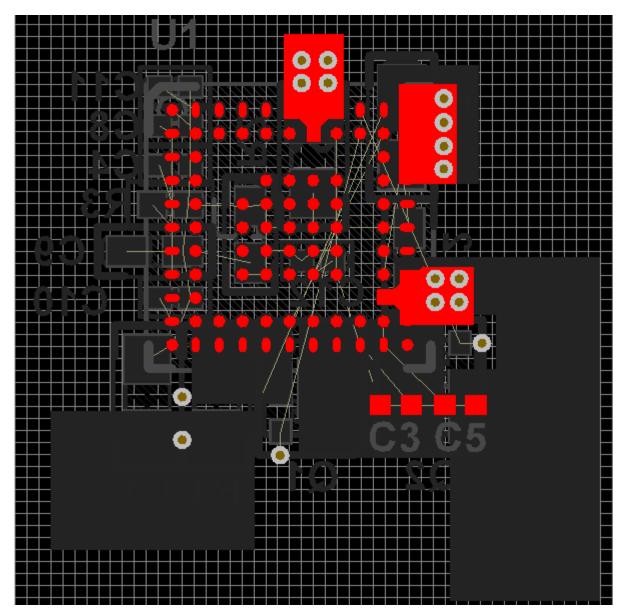

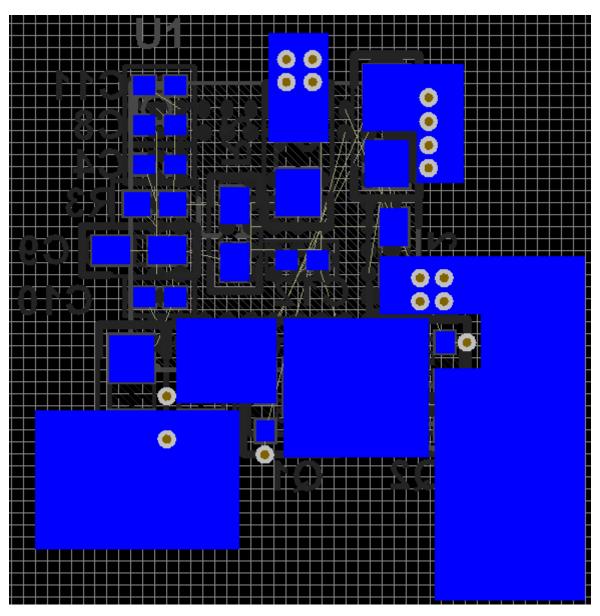

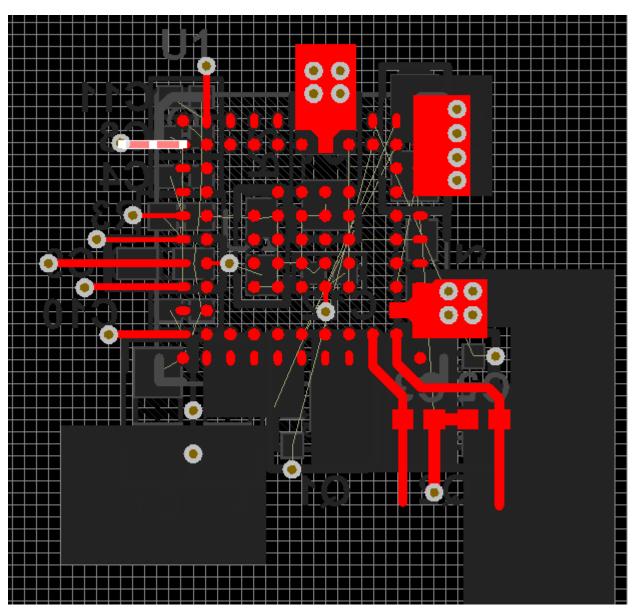

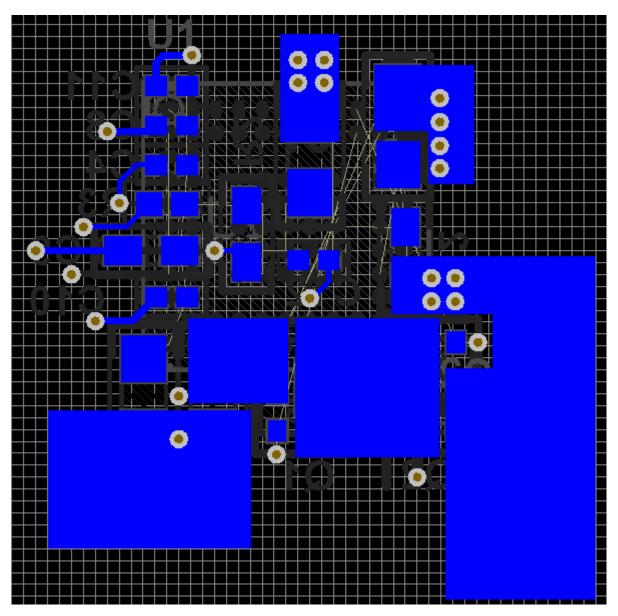

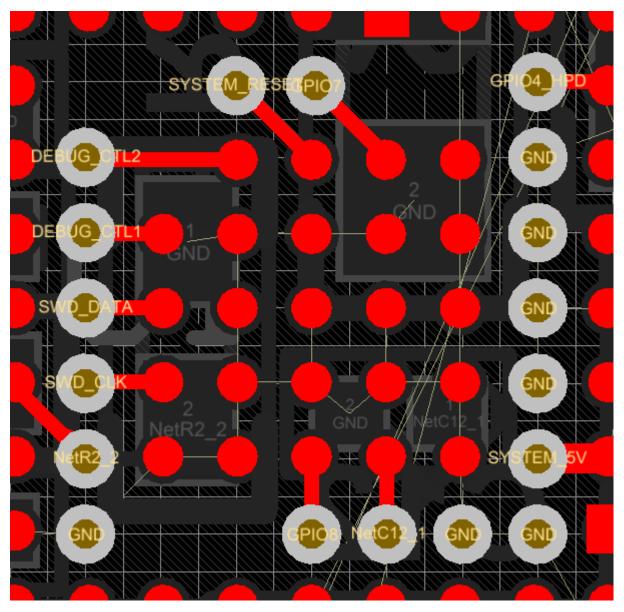

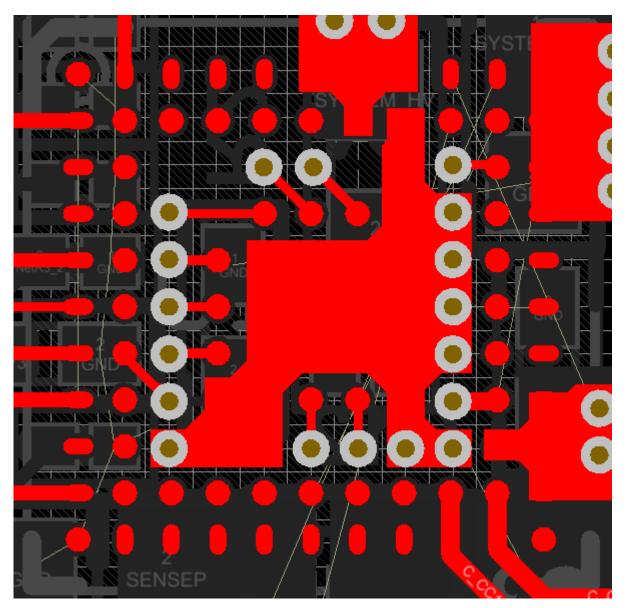

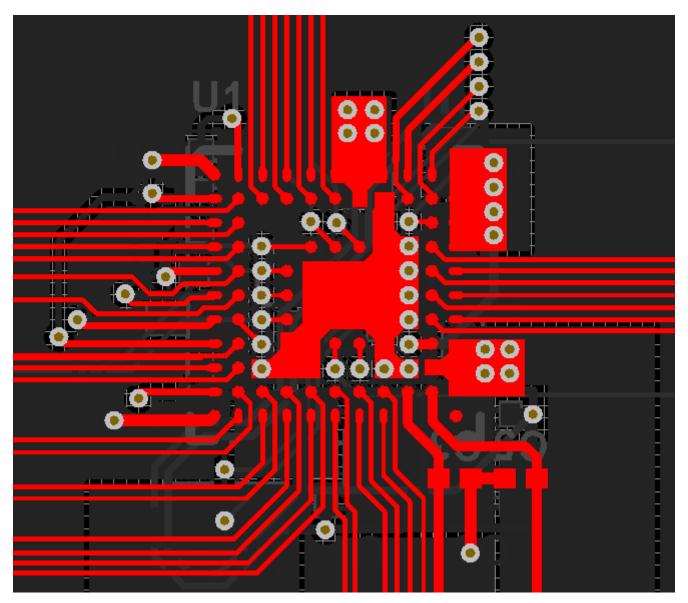

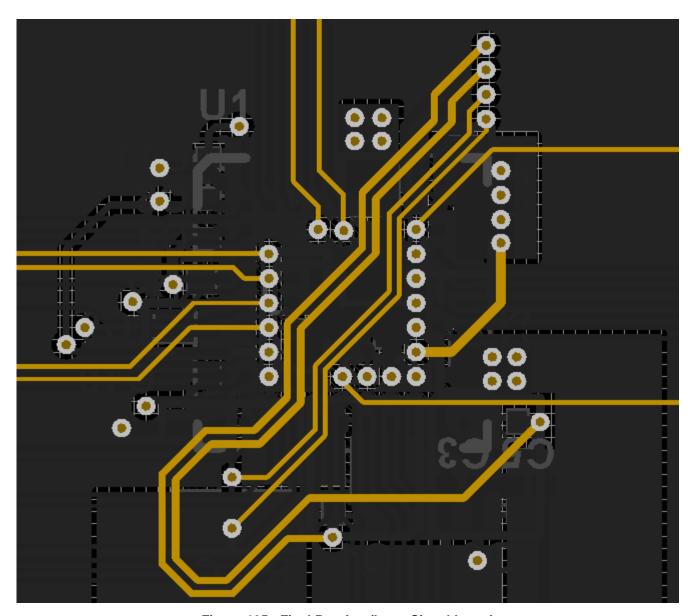

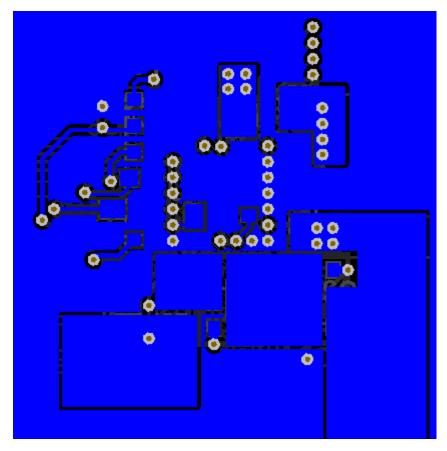

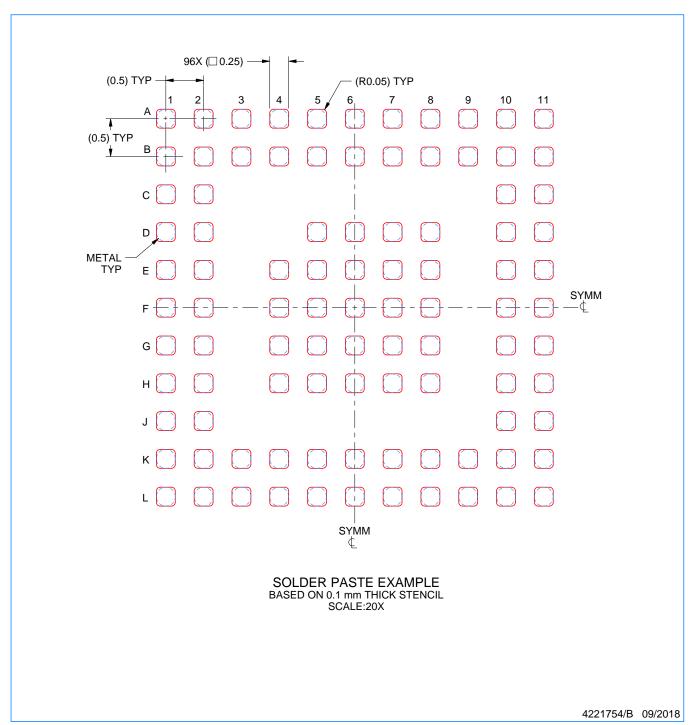

#### ZQZ and ZBH Package 96-Pin BGA MicroStar Junior and NFBGA Top View

Figure 1. Legend for Pinout Drawing

# **Pin Functions**

| PII             | N                     |                | POR                    |                                                                                                                                                                                                                                  |

|-----------------|-----------------------|----------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.                   | TYPE STATE     |                        | DESCRIPTION                                                                                                                                                                                                                      |

| HIGH-CURRENT P  | OWER PINS             |                |                        |                                                                                                                                                                                                                                  |

| PP_5V0          | A11, B11, C11,<br>D11 | Power          | NA                     | 5-V supply for VBUS. Bypass with capacitance CPP_5V0 to GND. Tie pin to GND when unused                                                                                                                                          |

| PP_HV           | A6, A7, A8, B7        | Power          | NA                     | HV supply for VBUS. Bypass with capacitance CPP_HV to GND. Tie pin to GND when unused                                                                                                                                            |

| PP_CABLE        | H10                   | Power          | NA                     | 5-V supply for C_CC pins. Bypass with capacitance CPP_CABLE to GND when not tied to PP_5V0. Tie pin to PP_5V0 when unused.                                                                                                       |

| VBUS            | H11, J10, J11,<br>K11 | Power          | NA                     | 5-V output from PP_5V0. Input or output from PP_HV up to 20 V. Bypass with capacitance CVBUS to GND.                                                                                                                             |

| LOW-CURRENT PO  | OWER PINS             |                |                        |                                                                                                                                                                                                                                  |

| VIN_3V3         | H1                    | Power          | NA                     | Supply for core circuitry and I/O. Bypass with capacitance CVIN_3V3 to GND.                                                                                                                                                      |

| VDDIO           | B1                    | Power          | NA                     | VDD for I/O. Some I/Os are reconfigurable to be powered from VDDIO instead of LDO_3V3. When VDDIO is not used, tie pin to LDO_3V3. When not tied to LDO_3V3 and used as a supply input, bypass with capacitance CVDDIO to GND.   |

| VOUT_3V3        | H2                    | Power          | NA                     | Output of supply switched from VIN_3V3. Bypass with capacitance COUT_3V3 to GND. Float pin when unused.                                                                                                                          |

| LDO_3V3         | G1                    | Power          | NA                     | Output of the VBUS to 3.3 V LDO or connected to VIN_3V3 by a switch. Main internal supply rail. Used to power external flash memory. Bypass with capacitance CLDO_3V3 to GND.                                                    |

| LDO_1V8A        | K1                    | Power          | NA                     | Output of the 3.3 V or 1.8 V LDO for Core Analog Circuits. Bypass with capacitance CLDO_1V8A to GND.                                                                                                                             |

| LDO_1V8D        | A2                    | Power          | NA                     | Output of the 3.3 V or 1.8 V LDO for Core Digital Circuits. Bypass with capacitance CLDO_1V8D to GND.                                                                                                                            |

| LDO_BMC         | E1                    | Power          | NA                     | Output of the USB-PD BMC transceiver output level LDO. Bypass with capacitance CLDO_BMC to GND.                                                                                                                                  |

| TYPE-C PORT PIN | S                     |                |                        |                                                                                                                                                                                                                                  |

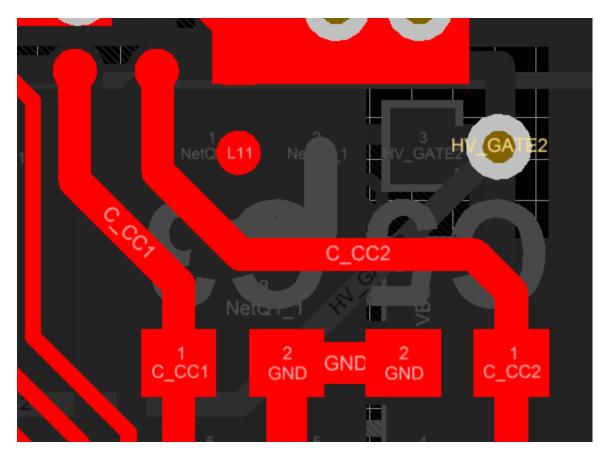

| C_CC1           | L9                    | Analog I/O     | Hi-Z                   | Output to Type-C CC or VCONN pin. Filter noise with capacitance CC_CC1 to GND.                                                                                                                                                   |

| C_CC2           | L10                   | Analog I/O     | Hi-Z                   | Output to Type-C CC or VCONN pin. Filter noise with capacitance CC_CC2 to GND.                                                                                                                                                   |

| RPD_G1          | K9                    | Analog I/O     | Hi-Z                   | Tie pin to C_CC1 when configured to receive power in dead-battery or no-power condition. Tie pin to GND otherwise.                                                                                                               |

| RPD_G2          | K10                   | Analog I/O     | Hi-Z                   | Tie pin to C_CC2 when configured to receive power in dead-battery or no-power condition. Tie pin to GND otherwise.                                                                                                               |

| C_USB_TP        | K6                    | Analog I/O     | Hi-Z                   | Port side Top USB D+ connection to Port Multiplexer.                                                                                                                                                                             |

| C_USB_TN        | L6                    | Analog I/O     | Hi-Z                   | Port side Top USB D- connection to Port Multiplexer.                                                                                                                                                                             |

| C_USB_BP        | K7                    | Analog I/O     | Hi-Z                   | Port side Bottom USB D+ connection to Port Multiplexer.                                                                                                                                                                          |

| C_USB_BN        | L7                    | Analog I/O     | Hi-Z                   | Port side Bottom USB D– connection to Port Multiplexer.                                                                                                                                                                          |

| C_SBU1          | K8                    | Analog I/O     | Hi-Z                   | Port side Sideband Use connection of Port Multiplexer.                                                                                                                                                                           |

| C_SBU2          | L8                    | Analog I/O     | Hi-Z                   | Port side Sideband Use connection of Port Multiplexer.                                                                                                                                                                           |

| PORT MULTIPLEX  | ER PINS               |                |                        |                                                                                                                                                                                                                                  |

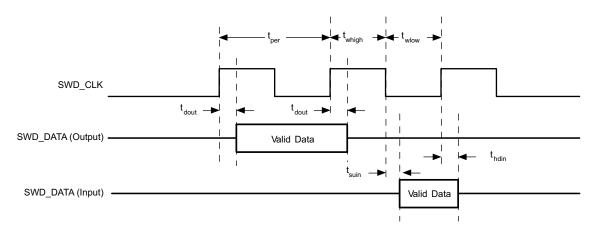

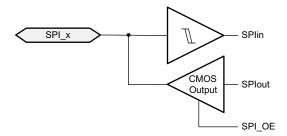

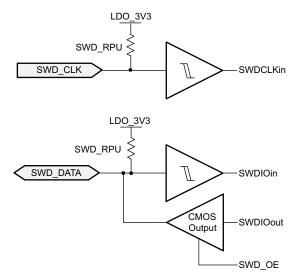

| SWD_DATA        | F4                    | Digital I/O    | Resistive Pull<br>High | SWD serial data. Float pin when unused.                                                                                                                                                                                          |

| SWD_CLK         | G4                    | Digital Input  | Resistive Pull<br>High | SWD serial clock. Float pin when unused.                                                                                                                                                                                         |

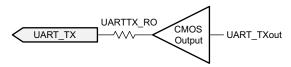

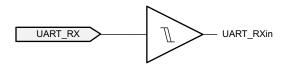

| UART_RX         | F2                    | Digital Input  | Digital Input          | UART serial receive data. Connect pin to another TPS65983B UART_TX to share firmware. Connect UART_RX to UART_TX when not connected to another TPS65983B and ground pin through a 100 k $\Omega$ resistance.                     |

| UART_TX         | E2                    | Digital Output | UART_RX                | UART serial transmit data. Connect pin to another TPS65983B UART_TX to share firmware. Connect UART_RX to UART_TX when not connected to another TPS65983B.                                                                       |

| USB_RP_P        | L5                    | Analog I/O     | Hi-Z                   | System side USB2.0 high-speed connection to Port Multiplexer. Ground pin with between 1-k $\Omega$ and 5-M $\Omega$ resistance when unused.                                                                                      |

| USB_RP_N        | K5                    | Analog I/O     | Hi-Z                   | System side USB2.0 high-speed connection to Port Multiplexer. Ground pin with between 1-k $\Omega$ and 5-M $\Omega$ resistance when unused.                                                                                      |

| LSX_R2P         | L4                    | Digital Input  | Digital Input          | System side low speed TX from system to port. This pin is configurable to be an input to the digital core or the crossbar multiplexer to the port. Ground pin with between 1-k $\Omega$ and 5-M $\Omega$ resistance when unused. |

| LSX_P2R         | K4                    | Digital Output | Hi-Z                   | System side low speed RX to system from port. This pin is configurable to be an output from the digital core or the crossbar multiplexer from the port. Float pin when unused.                                                   |

# Pin Functions (continued)

| DII                            | PIN POR       |                  |                           |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|--------------------------------|---------------|------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                           | NO.           | TYPE             | POR<br>STATE              | DESCRIPTION                                                                                                                                                                                                                                                                                           |  |  |  |  |

| AUX_P                          | J1            | Analog I/O       | Hi-Z                      | System side DisplayPort connection to Port Multiplexer. Ground pin with between 1- $k\Omega$ and 5-M $\Omega$ resistance when unused.                                                                                                                                                                 |  |  |  |  |

| AUX_N                          | J2            | Analog I/O       | Hi-Z                      | System side DisplayPort connection to Port Multiplexer. Ground pin with between 1- $k\Omega$ and 5-M $\Omega$ resistance when unused.                                                                                                                                                                 |  |  |  |  |

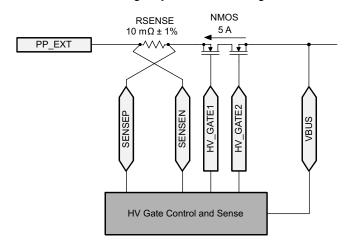

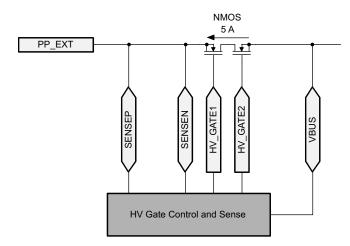

| EXTERNAL HV FET                | CONTROL/SENS  | E PINS AND SO    | OFT START                 |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SENSEP                         | B10           | Analog Input     | Analog Input              | Positive sense for external high voltage power path current sense resistance. Short pin to VBUS when unused.                                                                                                                                                                                          |  |  |  |  |

| SENSEN                         | A10           | Analog Input     | Analog Input              | Positive sense for external high voltage power path current sense resistance. Short pin to VBUS when unused.                                                                                                                                                                                          |  |  |  |  |

| HV_GATE1                       | B9            | Analog<br>Output | Short to<br>SENSEP        | External NFET gate control for high voltage power path. Float pin when unused.                                                                                                                                                                                                                        |  |  |  |  |

| HV_GATE2                       | A9            | Analog<br>Output | Short to VBUS             | External NFET gate control for high voltage power path. Float pin when unused.                                                                                                                                                                                                                        |  |  |  |  |

| SS                             | H7            | Analog<br>Output | Driven Low                | Soft Start. Tie pin to capacitance CSS to ground.                                                                                                                                                                                                                                                     |  |  |  |  |

| DIGITAL CORE I/O               | AND CONTROL P | INS              |                           |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| R_OSC                          | G2            | Analog I/O       | Hi-Z                      | External resistance setting for oscillator accuracy. Connect R_OSC to GND through resistance RR_OSC.                                                                                                                                                                                                  |  |  |  |  |

| GPIO0<br>(HD3 AMSEL)           | B2            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 0. Alternate mode select signal to external Super Speed multiplexer (tri-state capable with pullup and pulldown resistors). Ground pin with a 1- $\mbox{M}\Omega$ resistor when unused in the application.                                                                |  |  |  |  |

| GPIO1<br>(CONFIG0)             | C2            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 1. Must be tied high or low through a 1 k $\Omega$ pullup or pulldown resistor when used as a configuration input.                                                                                                                                                        |  |  |  |  |

| GPIO2                          | D10           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 2. Float pin if it is configured as a push-pull output in the application. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                                                                                        |  |  |  |  |

| GPIO3<br>(HD3 EN)              | G11           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 3. Enable signal to external Super Speed multiplexer. Float pin if it is configured as a push-pull output in the application. Ground pin with a $1-M\Omega$ resistor when unused in the application.                                                                      |  |  |  |  |

| GPIO4<br>(HPD TXRX)            | C10           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 4. Configured as Hot Plug Detect (HPD) TX and/or HPD RX when DisplayPort Mode supported. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                                                                          |  |  |  |  |

| GPIO5<br>(HPD RX)              | E10           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 5. Can be configured as Hot Plug Detect (HPD) RX when DisplayPort Mode supported. Must be tied high or low through a 1 k $\Omega$ pullup or pulldown resistor when used as a configuration input. Ground pin with a 1-M $\Omega$ resistor when unused in the application. |  |  |  |  |

| GPIO6                          | G10           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 6. Float pin if it is configured as a push-pull output in the application. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                                                                                        |  |  |  |  |

| GPIO7                          | D7            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 7. Float pin if it is configured as a push-pull output in the application. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                                                                                        |  |  |  |  |

| GPIO8                          | H6            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 8. Float pin if it is configured as a push-pull output in the application. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                                                                                        |  |  |  |  |

| RESETZ<br>(GPIO9)              | F11           | Digital I/O      | Push-Pull<br>Output (Low) | General Purpose Digital I/O 9. Active low reset output when VOUT_3V3 is low (driven low on start-up). Float pin when unused.                                                                                                                                                                          |  |  |  |  |

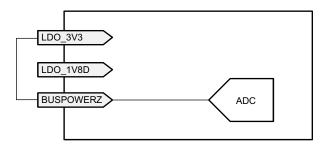

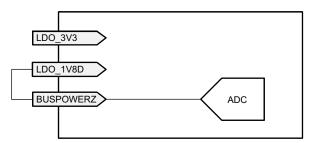

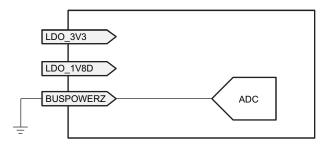

| BUSPOWERZ<br>(GPIO10)          | F10           | Analog Input     | Input (Hi-Z)              | General Purpose Digital I/O 10. Sampled by ADC at boot. Tie pin to LDO_3V3 through a 100-k $\Omega$ resistor to disable PP_HV and PP_EXT power paths during dead-battery or no-battery boot conditions. Refer to the <code>BUSPOWERZ</code> table for more details.                                   |  |  |  |  |

| MRESET<br>(GPIO11)             | E11           | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 11. Forces RESETZ to assert. By default, this pin asserts RESETZ when pulled high. The pin can be programmed to assert RESETZ when pulled low. Ground pin with a 1-M $\Omega$ resistor when unused in the application.                                                    |  |  |  |  |

| DEBUG4<br>(GPIO12,<br>CONFIG2) | К3            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 12. Must be tied high or low through a 1-k $\Omega$ pullup or pulldown resistor when used as a configuration input.                                                                                                                                                       |  |  |  |  |

| DEBUG3<br>(GPIO13,<br>CONFIG1) | L3            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 13. Must be tied high or low through a 1-k $\Omega$ pullup or pulldown resistor when used as a configuration input.                                                                                                                                                       |  |  |  |  |

| DEBUG2<br>(GPIO14, HD3<br>POL) | K2            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 14. Polarity signal to external Super Speed multiplexer. Float pin if it is configured as a push-pull output in the application. Ground pin with a $1\text{-}M\Omega$ resistor when unused in the application.                                                            |  |  |  |  |

| DEBUG1<br>(GPIO15)             | L2            | Digital I/O      | Hi-Z                      | General Purpose Digital I/O 15. Ground pin with a 1-M $\!\Omega$ resistor when unused in the application.                                                                                                                                                                                             |  |  |  |  |

# Pin Functions (continued)

| PI                                                  | N                                                                                                                 |                | POR           |                                                                                                                                                                                                      |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                | NO.                                                                                                               | TYPE           | STATE         | DESCRIPTION                                                                                                                                                                                          |

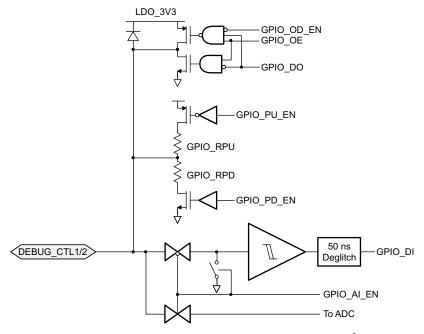

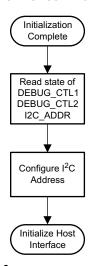

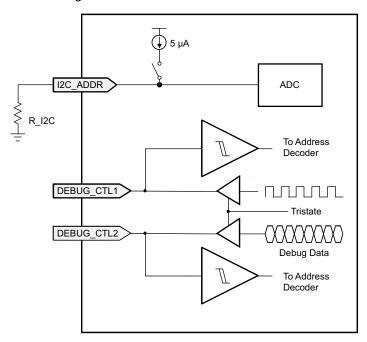

| DEBUG_CTL1<br>(GPIO16, I <sup>2</sup> C<br>ADDR B4) | E4                                                                                                                | Digital I/O    | Hi-Z          | General Purpose Digital I/O 16. At power-up, pin state is sensed to determine bit 4 of the I <sup>2</sup> C address.                                                                                 |

| DEBUG_CTL2<br>(GPIO17, I <sup>2</sup> C<br>ADDR B5) | D5                                                                                                                | Digital I/O    | Hi-Z          | General Purpose Digital I/O 17. At power-up, pin state is sensed to determine bit 5 of the I <sup>2</sup> C address.                                                                                 |

| HRESET                                              | D6                                                                                                                | Digital Input  | Hi-Z          | Active high hardware reset input. Will re-load settings from external flash memory. Ground pin when HRESET functionality will not be used.                                                           |

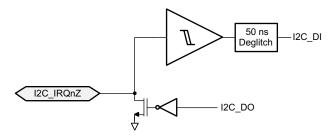

| I2C_SDA1                                            | D1                                                                                                                | Digital I/O    | Digital Input | l <sup>2</sup> C port 1 serial data. Open-drain output. Tie pin to LDO_3V3 or VDDIO (depending on configuration) through a 10-k $\Omega$ resistor when used or unused.                               |

| I2C_SCL1                                            | D2                                                                                                                | Digital I/O    | Digital Input | l <sup>2</sup> C port 1 serial clock. Open-drain output. Tie pin to LDO_3V3 or VDDIO (depending on configuration) through a 10-k $\Omega$ resistor when used or unused.                              |

| I2C_IRQ1Z                                           | C1                                                                                                                | Digital Output | Hi-Z          | I <sup>2</sup> C port 1 interrupt. Active low. Implement externally as an open drain with a pullup resistance. Float pin when unused.                                                                |

| I2C_SDA2                                            | A5                                                                                                                | Digital I/O    | Digital Input | l <sup>2</sup> C port 2 serial data. Open-drain output. Tie pin to LDO_3V3 or VDDIO (depending on configuration) through a 10-k $\Omega$ resistor when used or unused.                               |

| I2C_SCL2                                            | B5                                                                                                                | Digital I/O    | Digital Input | l <sup>2</sup> C port 2 serial clock. Open-drain output. Tie pin to LDO_3V3 or VDDIO (depending on configuration) through a 10-k $\Omega$ resistor when used or unused.                              |

| I2C_IRQ2Z                                           | В6                                                                                                                | Digital Output | Hi-Z          | I <sup>2</sup> C port 2 interrupt. Active low. Implement externally as an open drain with a pullup resistance. Float pin when unused.                                                                |

| I2C_ADDR                                            | F1                                                                                                                | Analog I/O     | Analog Input  | Sets the I <sup>2</sup> C address for both I <sup>2</sup> C ports as well as determine the master and slave devices for memory code sharing.                                                         |

| SPI_CLK                                             | A3                                                                                                                | Digital Output | Digital Input | SPI serial clock. Ground pin when unused                                                                                                                                                             |

| SPI_MOSI                                            | B4                                                                                                                | Digital Output | Digital Input | SPI serial master output to slave. Ground pin when unused.                                                                                                                                           |

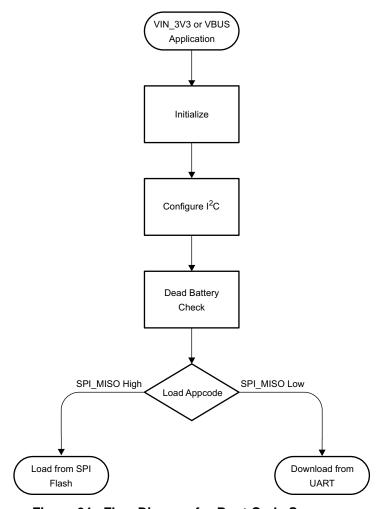

| SPI_MISO                                            | A4                                                                                                                | Digital Input  | Digital Input | SPI serial master input from slave. This pin is used during boot sequence to determine if the flash memory is valid. Refer to the <i>Boot Code</i> section for more details. Ground pin when unused. |

| SPI_SSZ                                             | В3                                                                                                                | Digital Output | Digital Input | SPI slave select. Ground pin when unused.                                                                                                                                                            |

| GROUND AND NO                                       | CONNECT PINS                                                                                                      |                |               |                                                                                                                                                                                                      |

| GND                                                 | A1, B8, D8, E5,<br>E6, E7, E8, F5,<br>F6, F7, F8, G5,<br>G6, G7, G8, H4,<br>H5, H8, L1                            | Ground         | NA            | Ground. Connect all balls to ground plane.                                                                                                                                                           |

| NC                                                  | L11                                                                                                               | Blank          | NA            | Populated Ball that must remain unconnected.                                                                                                                                                         |

| No Ball                                             | C3, C4, C5, C6,<br>C7, C8, C9, D3,<br>D4, D9, E3, E9,<br>F3, F9, G3, G9,<br>H3, H9, J3, J4,<br>J5, J6, J7, J8, J9 | Blank          | NA            | Unpopulated ball for A1 marker and unpopulated inner ring.                                                                                                                                           |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                      |                                                                                                                                                                                                  | MIN                                      | MAX            | UNIT |

|------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|------|

|                  |                      | PP_CABLE, PP_5V0                                                                                                                                                                                 | -0.3                                     | 6              |      |

| .,               | Input voltage (2)    | VIN_3V3                                                                                                                                                                                          | -0.3                                     | 3.6            | V    |

| VI               | input voltage        | SENSEP, SENSEN <sup>(3)</sup>                                                                                                                                                                    | -0.3                                     | 24             | V    |

|                  |                      | VDDIO, UART_RX                                                                                                                                                                                   | -0.3                                     | LDO_3V3 + 0.3  |      |

|                  |                      | LDO_1V8A, LDO_1V8D, LDO_BMC, SS                                                                                                                                                                  | -0.3                                     | 2              |      |

|                  |                      | LDO_3V3                                                                                                                                                                                          | -0.3                                     | 3.45           |      |

| V <sub>IO</sub>  | Output voltage (2)   | VOUT_3V3, RESETZ, I2C _IRQ1Z, I2C_IRQ2Z, SPI_MOSI, SPI_CLK, SPI_SSZ, LSX_P2R, SWD_CLK, UART_TX                                                                                                   | -0.3                                     | LDO_3V3 + 0.3  | V    |

| .0               | , ,                  | HV_GATE1, HV_GATE2                                                                                                                                                                               | -0.3                                     | 30             |      |

|                  |                      | HV_GATE1 (relative to SENSEP)                                                                                                                                                                    | -0.3                                     | 6              |      |

|                  |                      | HV_GATE2 (relative to VBUS)                                                                                                                                                                      | DEBUG2, DEBUG3, DEBUG4, SPOWERZ, GPIO0-8 |                |      |

|                  |                      | PP_HV, VBUS (2)                                                                                                                                                                                  | -0.3                                     | 24             |      |

|                  |                      | I2C_SDA1, I2C_SCL1, SWD_DATA, SPI_MISO, I2C_SDA2, I2C_SCL2, LSX_R2P, USB_RP_P, USB_RP_N, AUX_N, AUX_P, DEBUG1, DEBUG2, DEBUG3, DEBUG4, DEBUG_CTL1, DEBUG_CTL2, GPIOn, MRESET, BUSPOWERZ, GPIO0-8 | -0.3                                     | LDO_3V3 + 0.3  |      |

| V <sub>IO</sub>  |                      | R_OSC, I2C_ADDR                                                                                                                                                                                  | -0.3                                     | 2              |      |

| $V_{IO}$         | I/O voltage (2)      | HRESET                                                                                                                                                                                           | -0.3                                     | LDO_1V8D + 0.3 | V    |

|                  |                      | C_USB_TP, C_USB_TN, C_USB_BP, C_USB_BN, C_SBU2, C_SBU1 (Switches Open)                                                                                                                           | -2                                       | 6              |      |

|                  |                      | C_USB_TP, C_USB_TN, C_USB_BP, C_USB_BN, C_SBU2, C_SBU1 (Switches Closed)                                                                                                                         | -0.3                                     | 6              |      |

|                  |                      | C_CC1, C_CC2, RPD_G1, RPD_G2                                                                                                                                                                     | -0.3                                     | 6              |      |

| TJ               | Operating junction t | emperature                                                                                                                                                                                       | -10                                      | 125            | °C   |

| T <sub>stg</sub> | Storage temperatur   | e                                                                                                                                                                                                | <b>-</b> 55                              | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

<sup>(2)</sup> All voltage values are with respect to network GND. All GND pins must be connected directly to the GND plane of the board.

<sup>(3)</sup> The 24 V maximum is based on keeping HV\_GATE1/2 at or below 30 V. Fast voltage transitions (<100 ns) may occur up to 30 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                                       |                                                        | MIN  | MAX  | UNIT |

|----------|---------------------------------------|--------------------------------------------------------|------|------|------|

|          |                                       | VIN_3V3                                                | 2.85 | 3.45 |      |

|          |                                       | PP_5V0                                                 | 4.75 | 5.5  |      |

| $V_{I}$  | Input voltage<br>range <sup>(1)</sup> | PP_CABLE                                               | 2.95 | 5.5  | V    |

|          | range                                 | PP_HV                                                  | 4.5  | 22   |      |

|          |                                       | VDDIO                                                  | 1.7  | 3.45 |      |

|          |                                       | VBUS                                                   | 4    | 22   |      |

| $V_{IO}$ | I/O voltage<br>range <sup>(1)</sup>   | C_USB_PT, C_USB_NT, C_USB_PB, C_USB_NB, C_SBU1, C_SBU2 | -2   | 5.5  | V    |

|          | range                                 | C_CC1, C_CC2                                           | 0    | 5.5  |      |

| $T_A$    | Ambient operating temperature range   |                                                        | -10  | 85   | °C   |

| $T_{B}$  | Operating board                       | Operating board temperature range                      |      | 100  | °C   |

| $T_{J}$  | Operating junctio                     | n temperature range                                    | -10  | 125  | °C   |

<sup>(1)</sup> All voltage values are with respect to network GND. All GND pins must be connected directly to the GND plane of the board.

### 7.4 Thermal Information

|                      |                                              | TPS65983B |             |      |

|----------------------|----------------------------------------------|-----------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | ZQZ (BGA) | ZBH (NFBGA) | UNIT |

|                      |                                              | 96 BALLS  | 96 BALLS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 42.4      | 42.4        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 12.4      | 12.4        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 13        | 13          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3       | 0.3         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 13        | 13          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

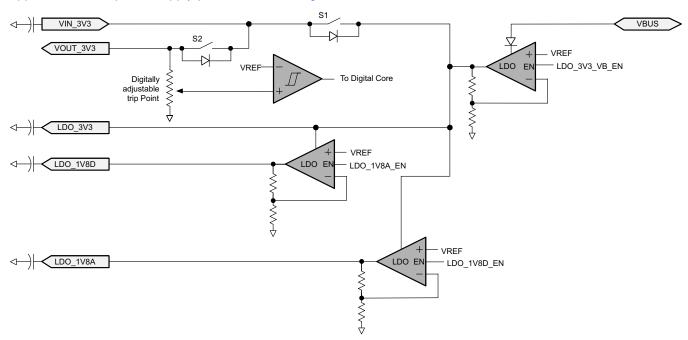

# 7.5 Power Supply Requirements and Characteristics

|                      | PARAMETER                                                                                                        | TEST CONDITIONS                                     | MIN  | TYP   | MAX  | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-------|------|------|

| EXTERNAL             |                                                                                                                  |                                                     |      |       |      |      |

| VIN_3V3              | Input 3.3-V supply                                                                                               |                                                     | 2.85 | 3.3   | 3.45 | V    |

| PP_CABLE             | Input voltage to power C_CC pins. This input is also available to power core circuitry and the VOUT_3V3 output.  |                                                     | 2.95 | 5     | 5.5  | V    |

| VBUS                 | Bi-direction DC bus voltage. Output from the TPS65983B or input to the TPS65983B.                                |                                                     | 4    | 5     | 22   | V    |

| PP_5V0               | 5-V supply input to power VBUS. This supply does not power the TPS65983B.                                        |                                                     | 4.75 | 5     | 5.5  | V    |

| VDDIO <sup>(1)</sup> | Optional supply for I/O cells.                                                                                   |                                                     | 1.7  |       | 3.45 | V    |

| INTERNAL             |                                                                                                                  |                                                     | •    |       |      |      |

| VLDO_3V3             | DC 3.3V generated internally by either a switch from VIN_3V3, an LDO from PP_CABLE, or an LDO from VBUS          |                                                     | 2.7  | 3.3   | 3.45 | V    |

| VDO_LDO3V3           | Drop Out Voltage of LDO_3V3 from PP_CABLE                                                                        | I <sub>LOAD</sub> = 50 mA                           |      |       | 250  | mV   |

|                      | Drop Out Voltage of LDO_3V3 from VBUS                                                                            |                                                     | 250  | 500   | 750  | mV   |

| VLDO_1V8D            | DC 1.8V generated for internal digital circuitry.                                                                |                                                     | 1.7  | 1.8   | 1.9  | V    |

| VLDO_1V8A            | DC 1.8V generated for internal analog circuitry.                                                                 |                                                     | 1.7  | 1.8   | 1.9  | V    |

| VLDO_BMC             | DC voltage generated on LDO_BMC. Setting for USB-PD.                                                             |                                                     | 1.05 | 1.125 | 1.2  | V    |

| ILDO_3V3             | DC current supplied by the 3.3V LDOs. This includes internal core power and external load on LDO_3V3.            |                                                     |      |       | 70   | mA   |

| ILDO_3V3EX           | External DC current supplied by LDO_3V3                                                                          |                                                     |      |       | 30   | mA   |

| IOUT_3V3             | External DC current supplied by VOUT_3V3                                                                         |                                                     |      |       | 100  | mA   |

| ILDO_1V8D            | DC current supplied by LDO_1V8D. This is intended for internal loads only but small external loads may be added. |                                                     |      |       | 50   | mA   |

| ILDO_1V8DEX          | External DC current supplied by LDO_1V8D.                                                                        |                                                     |      |       | 5    | mA   |

| ILDO_1V8A            | DC current supplied by LDO_1V8A. This is intended for internal loads only but small external loads may be added. |                                                     |      |       | 20   | mA   |

| ILDO_1V8AEX          | External DC current supplied by LDO_1V8A.                                                                        |                                                     |      |       | 5    | mA   |

| ILDO_BMC             | DC current supplied by LDO_BMC. This is intended for internal loads only.                                        |                                                     |      |       | 5    | mA   |

| ILDO_BMCEX           | External DC current supplied by LDO_BMC.                                                                         |                                                     |      |       | 0    | mA   |

| VFWD_DROP            | Forward voltage drop across VIN_3V3 to LDO_3V3 switch                                                            | I <sub>LOAD</sub> = 50 mA                           | 25   | 60    | 90   | mV   |

| RIN_3V3              | Input switch resistance from VIN_3V3 to LDO_3V3                                                                  | V <sub>VIN_3V3</sub> – V <sub>LDO_3V3</sub> > 50 mV | 0.5  | 1.1   | 1.75 | Ω    |

| ROUT_3V3             | Output switch resistance from VIN_3V3 to VOUT_3V3                                                                |                                                     |      | 0.35  | 0.7  | Ω    |

| TR_OUT3V3            | 10-90% rise time on VOUT_3V3 from switch enable.                                                                 | C <sub>VOUT_3V3</sub> = 1 μF                        | 35   |       | 120  | μs   |

<sup>(1)</sup> I/O buffers are not fail-safe to LDO\_3V3. Therefore, VDDIO may power-up before LDO\_3V3. When VDDIO powers up before LDO\_3V3, the I/Os shall not be driven high. When VDDIO is low and LDO\_3V3 is high, the I/Os may be driven high.

### 7.6 Power Supervisor Characteristics

Recommended operating conditions:  $T_A = -10$  to +85°C unless otherwise noted

|              | PARAMETER                                                                                  | TEST CONDITIONS            | MIN   | TYP   | MAX                                                                            | UNIT |

|--------------|--------------------------------------------------------------------------------------------|----------------------------|-------|-------|--------------------------------------------------------------------------------|------|

| UV_LDO3V3    | Under-voltage threshold for LDO_3V3. Locks out 1.8-V LDOs                                  | LDO_3V3 rising             | 2.2   | 2.325 | 2.45                                                                           | ٧    |

| UVH_LDO3V3   | Under-voltage hysteresis for LDO_3V3                                                       | LDO_3V3 falling            | 20    | 80    | 150                                                                            | mV   |

| UV_VBUS_LDO  | Under-voltage threshold for VBUS to enable LDO                                             | VBUS rising                | 3.35  | 3.75  | 3.95                                                                           | V    |

| UVH_VBUS_LDO | Under-voltage hysteresis for VBUS to enable LDO                                            | VBUS falling               | 20    | 80    | 150                                                                            | mV   |

| UV_PCBL      | Under-voltage threshold for PP_CABLE                                                       | PP_CABLE rising            | 2.5   | 2.625 | 2.75                                                                           | V    |

| UVH_PCBL     | Under-voltage hysteresis for PP_PCABLE                                                     | PP_CABLE falling           | 20    | 50    | 80                                                                             | mV   |

| UV_5V0       | Under-voltage threshold for PP_5V0                                                         | PP_5V0 rising              | 3.5   | 3.725 | 3.95                                                                           | V    |

| UVH_5V0      | Under-voltage hysteresis for PP_P5V0                                                       | PP_5V0 falling             | 20    | 80    | 150                                                                            | mV   |

| OV_VBUS      | Over-voltage threshold for VBUS. This value is a 6-bit programmable threshold              | VBUS rising                | 5     |       | 24                                                                             | ٧    |

| OVLSB_VBUS   | Over-voltage threshold step for VBUS. This value is the LSB of the programmable threshold  | VBUS rising                |       | 328   |                                                                                | mV   |

| OVH_VBUS     | Over-voltage hysteresis for VBUS                                                           | VBUS falling, % of OV_VBUS | 0.9%  | 1.3%  | 1.7%                                                                           |      |

| UV_VBUS      | Under-voltage threshold for VBUS. This value is a 6-bit programmable threshold             | VBUS falling               | 2.5   |       | 18.21                                                                          | ٧    |

| UVLSB_VBUS   | Under-voltage threshold step for VBUS. This value is the LSB of the programmable threshold | VBUS falling               |       | 249   |                                                                                | mV   |

| UVH_VBUS     | Under-voltage hysteresis for VBUS                                                          | VBUS rising, % of UV_VBUS  | 0.9%  | 1.3%  | 1.7%                                                                           |      |

|              |                                                                                            | Setting 0                  | 2.019 | 2.125 | 2.231                                                                          |      |

|              |                                                                                            | Setting 1                  | 2.138 | 2.25  | 2.45<br>150<br>3.95<br>150<br>2.75<br>80<br>3.95<br>150<br>24<br>1.7%<br>18.21 |      |

|              |                                                                                            | Setting 2                  | 2.256 | 2.375 |                                                                                |      |

| LIVE OUTOVO  | Configurable under-voltage threshold for VOUT 3V3 rising.                                  | Setting 3                  | 2.375 | 2.5   |                                                                                | V    |

| UVR_OUT3V3   | De-asserts RESETZ                                                                          | Setting 4                  | 2.494 | 2.625 | 2.756                                                                          | V    |

|              |                                                                                            | Setting 5                  | 2.613 | 2.75  | 2.888                                                                          |      |

|              |                                                                                            | Setting 6                  | 2.731 | 2.875 | 3.019                                                                          |      |

|              |                                                                                            | Setting 7                  | 2.85  | 3     | 3.15                                                                           |      |

| UVRH_OUT3V3  | Under-voltage hysteresis for VOUT_3V3 falling.                                             | OUT_3V3 falling            |       | 30    | 50                                                                             | mV   |

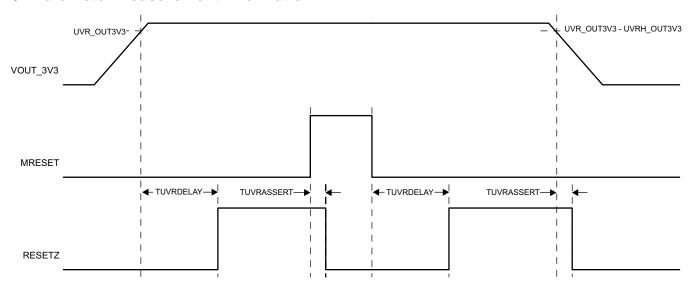

| TUVRASSERT   | Delay from falling VOUT_3V3 or MRESET assertion to RESETZ asserting low                    |                            |       |       | 75                                                                             | μS   |

| TUVRDELAY    | Configurable delay from VOUT_3V3 to RESETZ deassertion.                                    |                            | 0     |       | 161.3                                                                          | ms   |

### 7.7 Power Consumption Characteristics

Recommended operating conditions; T<sub>A</sub> = 25°C (Room temperature) unless otherwise noted<sup>(1)</sup>

| PARAMETER                    | TEST CONDITIONS                                                                                              | MIN | TYP | MAX | UNIT |

|------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| IVIN_3V3 in sleep (2)        | VIN_3V3 = VDDIO = 3.45 V, VBUS = 0,<br>PPCABLE = 0; 100-kHz oscillator running                               |     | 67  |     | μΑ   |

| IVIN_3V3 idle <sup>(3)</sup> | VIN_3V3 = VDDIO = 3.45 V, VBUS=0, PPCABLE = 0; 100-kHz oscillator running, 48-MHz oscillator running         |     | 2.4 |     | mA   |

| IVIN_3V3 active (4)          | VIN_3V3 = VDDIO = 3.45 V, VBUS = 0,<br>PPCABLE = 0; 100-kHz Oscillator running,<br>48-MHz oscillator running |     | 7.6 |     | mA   |

<sup>(1)</sup> Application code can result in other power consumption measurements by adjusting enabled circuitry and clock rates. Application code also provisions the wake-up mechanisms (for example, I<sup>2</sup>C activity and GPIO activity).

Sleep is defined as Type-C cable detect activated as DFP or UFP, internal power management and supervisory functions active.

Idle is defined as Type-C cable detect activated as DFP or UFP, internal power management and supervisory functions active, and the digital core is clocked at 4 MHz.

<sup>(4)</sup> Active is defined as Type-C cable detect activated as DFP or UFP, internal power management and supervisory functions active, all core functionality active, and the digital core is clocked at 12 MHz. DRP in a Source Power Role connected to a Sink under a 5V contract.

# 7.8 Cable Detection Characteristics

|            | PARAMETER                                                                                                                                                                 | TEST CONDITIONS                          | MIN   | TYP  | MAX   | UNIT |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|------|-------|------|

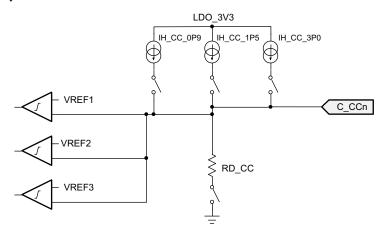

| IH_CC_USB  | Source Current through each C_CC pin when in a disconnected state and Configured as a DFP advertising Default USB current to a peripheral device                          |                                          | 73.6  | 80   | 86.4  | μА   |

| IH_CC_1P5  | Source Current through each C_CC pin when in a disconnected state when Configured as a DFP advertising 1.5 A to a UFP                                                     |                                          | 169   | 180  | 191   | μΑ   |

| IH_CC_3P0  | Source Current through each C_CC pin when in a disconnected state and Configured as a DFP advertising 3.0 A to a UFP.                                                     | VIN_3V3 ≥ 3.135 V                        | 303   | 330  | 356   | μΑ   |

| VD_CCH_USB | Voltage Threshold for detecting a DFP attach when configured as a UFP and the DFP is advertising Default USB current source capability                                    |                                          | 0.15  | 0.2  | 0.25  | ٧    |

| VD_CCH_1P5 | Voltage Threshold for detecting a DFP advertising 1.5 A source capability when configured as a UFP                                                                        |                                          | 0.61  | 0.66 | 0.7   | V    |

| VD_CCH_3P0 | Voltage Threshold for detecting a DFP advertising 3 A source capability when configured as a UFP                                                                          |                                          | 1.169 | 1.23 | 1.29  | V    |

| VH_CCD_USB | Voltage Threshold for detecting a UFP attach when configured as a DFP and advertising Default USB current source capability.                                              | IH_CC = IH_CC_USB                        | 1.473 | 1.55 | 1.627 | V    |

| VH_CCD_1P5 | Voltage Threshold for detecting a UFP attach when configured as a DFP and advertising 1.5 A source capability                                                             | IH_CC = IH_CC_1P5                        | 1.473 | 1.55 | 1.627 | V    |

| VH_CCD_3P0 | Voltage Threshold for detecting a UFP attach when configured as a DFP and advertising 3.0 A source capability.                                                            | IH_CC = IH_CC_3P0<br>VIN_3V3 ≥ 3.135 V   | 2.423 | 2.55 | 2.67  | V    |

| VH_CCA_USB | Voltage Threshold for detecting an active cable attach when configured as a DFP and advertising Default USB current capability.                                           |                                          | 0.15  | 0.2  | 0.25  | ٧    |

| VH_CCA_1P5 | Voltage Threshold for detecting active cables attach when configured as a DFP and advertising 1.5 A capability.                                                           |                                          | 0.35  | 0.4  | 0.45  | V    |

| VH_CCA_3P0 | Voltage Threshold for detecting active cables attach when configured as a DFP and advertising 3 A capability.                                                             |                                          | 0.76  | 0.8  | 0.84  | V    |

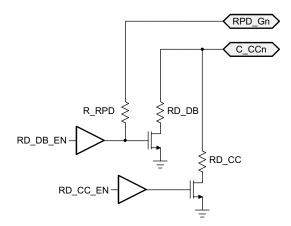

| RD_CC      | Pulldown resistance through each C_CC pin when in a disconnect state and configured as a UFP. LDO_3V3 powered.                                                            | V = 1 V, 1.5 V                           | 4.85  | 5.1  | 5.35  | kΩ   |

| RD_CC_OPEN | Pulldown resistance through each C_CC pin when in a disconnect state and configured as a UFP. LDO_3V3 powered.                                                            | V = 0 V to LDO_3V3                       | 500   |      |       | kΩ   |

| RD_DB      | Pulldown resistance through each C_CC pin when in a disconnect state and configured as a UFP when configured for dead battery (RPD_Gn tied to C_CCn). LDO_3V3 unpowered   | V = 1.5 V, 2.0 V<br>RPD_Gn tied to C_CCn | 4.08  | 5.1  | 6.12  | kΩ   |

| RD_DB_OPEN | Pulldown resistance through each C_CC pin when in a disconnect state and configured as a UFP when not configured for dead battery (RPD_Gn tied to GND). LDO_3V3 unpowered | V = 1.5 V, 2.0 V<br>RPD_Gn tied to GND   | 500   |      |       | kΩ   |

| VTH_DB     | Threshold Voltage of the pulldown FET in series with RD during dead battery                                                                                               | I_CC = 80 μA                             | 0.5   | 0.9  | 1.2   | V    |

| R_RPD      | Resistance between RPD_Gn and the gate of the pulldown FET                                                                                                                |                                          | 25    | 50   | 85    | MΩ   |

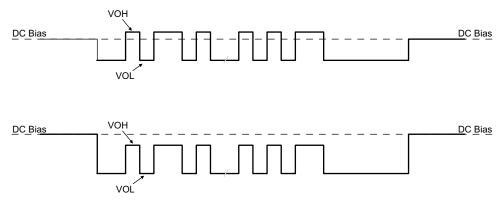

### 7.9 USB-PD Baseband Signal Requirements and Characteristics

Recommended operating conditions;  $T_A = -10$  to +85°C unless otherwise noted

|                         | PARAMETER                                                                                                                                      | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|-----|------|

| COMMON                  |                                                                                                                                                |                                                                                        |      |      | '   |      |

| PD_BITRATE              | PD data bit rate                                                                                                                               |                                                                                        | 270  | 300  | 330 | Kbps |

| UI <sup>(1)</sup>       | Unit interval (1/PD_BITRATE)                                                                                                                   |                                                                                        | 3.03 | 3.33 | 3.7 | μS   |

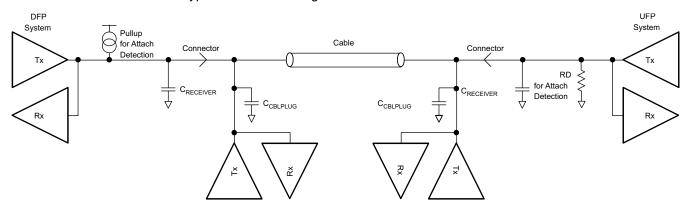

| CCBLPLUG <sup>(2)</sup> | Capacitance for a cable plug (each plug on a cable may have up to this value)                                                                  |                                                                                        |      |      | 25  | pF   |

| ZCABLE                  | Cable characteristic impedance                                                                                                                 |                                                                                        | 32   |      | 65  | Ω    |

| CRECEIVER (3)           | Receiver capacitance. Capacitance looking into C_CCn pin when in receiver mode.                                                                |                                                                                        | 70   |      | 120 | pF   |

| TRANSMITTER             |                                                                                                                                                |                                                                                        |      |      |     |      |

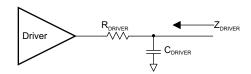

| ZDRIVER                 | TX output impedance. Source output impedance at the Nyquist frequency of USB2.0 low speed (750kHz) while the source is driving the C_CCn line. |                                                                                        | 33   |      | 75  | Ω    |

| TRISE                   | Rise Time. 10% to 90% amplitude points, minimum is under an unloaded condition. Maximum set by TX mask.                                        |                                                                                        | 300  |      |     | ns   |

| TFALL                   | Fall Time. 90% to 10% amplitude points, minimum is under an unloaded condition. Maximum set by TX mask.                                        |                                                                                        | 300  |      |     | ns   |

| RECEIVER                |                                                                                                                                                | <u> </u>                                                                               |      |      |     |      |

| VRXTR                   | Rx Receive Rising Input threshold                                                                                                              |                                                                                        | 605  | 630  | 655 | mV   |

| VRXTF                   | Rx Receive Falling Input threshold                                                                                                             |                                                                                        | 450  | 470  | 490 | mV   |

| NCOUNT <sup>(4)</sup>   | Number of transitions for signal detection (number to count to detect non-idle bus).                                                           |                                                                                        | 3    |      |     |      |

| TTRANWIN <sup>(4)</sup> | Time window for detecting non-idle bus.                                                                                                        |                                                                                        | 12   |      | 20  | μS   |

| ZBMCRX                  | Receiver input impedance                                                                                                                       | Does not include pullup or pulldown resistance from cable detect. Transmitter is Hi-Z. | 10   |      |     | МΩ   |

| TRXFILTER (5)           | Rx bandwidth limiting filter. Time constant of a single pole filter to limit broadband noise ingression                                        |                                                                                        | 100  |      |     | ns   |

- (1) UI denotes the time to transmit an un-encoded data bit not the shortest high or low times on the wire after encoding with BMC. A single data bit cell has duration of 1 UI, but a data bit cell with value 1 will contain a centrally place 01 or 10 transition in addition to the transition at the start of the cell.

- (2) The capacitance of the bulk cable is not included in the CCBLPLUG definition. It is modeled as a transmission line.

- (3) CRECEIVER includes only the internal capacitance on a C\_CCn pin when the pin is configured to be receiving BMC data. External capacitance is needed to meet the required minimum capacitance per the USB-PD Specifications. It is recommended to add capacitance to bring the total pin capacitance to 300 pF for improved TX behavior.

- (4) BMC packet collision is avoided by the detection of signal transitions at the receiver. Detection is active when a minimum of NCOUNT transitions occur at the receiver within a time window of TTRANWIN. After waiting TTRANWIN without detecting NCOUNT transitions, the bus is declared idle.

- (5) Broadband noise ingression is due to coupling in the cable interconnect.

# 7.10 USB-PD TX Driver Voltage Adjustment Parameter<sup>(1)</sup>

|       | PARAMETER                | TEST CONDITIONS | MIN   | NOM   | MAX   | UNIT |

|-------|--------------------------|-----------------|-------|-------|-------|------|

| VTXP0 | TX Transmit Peak Voltage |                 | 1.615 | 1.7   | 1.785 | V    |

| VTXP1 | TX Transmit Peak Voltage |                 | 1.52  | 1.6   | 1.68  | V    |

| VTXP2 | TX Transmit Peak Voltage |                 | 1.425 | 1.5   | 1.575 | V    |

| VTXP3 | TX Transmit Peak Voltage |                 | 1.33  | 1.4   | 1.47  | V    |

| VTXP4 | TX Transmit Peak Voltage |                 | 1.235 | 1.3   | 1.365 | V    |

| VTXP5 | TX Transmit Peak Voltage |                 | 1.188 | 1.25  | 1.312 | V    |

| VTXP6 | TX Transmit Peak Voltage |                 | 1.14  | 1.2   | 1.26  | V    |

| VTXP7 | TX Transmit Peak Voltage |                 | 1.116 | 1.175 | 1.233 | V    |

| VTXP8 | TX Transmit Peak Voltage |                 | 1.092 | 1.15  | 1.208 | V    |

| VTXP9 | TX Transmit Peak Voltage |                 | 1.068 | 1.125 | 1.181 | V    |

<sup>(1)</sup> VTXP voltage settings are determined by application code and the setting used must meet the needs of the application and adhere to the USB-PD Specifications.

# **USB-PD TX Driver Voltage Adjustment Parameter**<sup>(1)</sup> (continued)

Recommended operating conditions;  $T_A = -10$  to +85°C unless otherwise noted

|        | PARAMETER                | TEST CONDITIONS | MIN   | NOM   | MAX   | UNIT |

|--------|--------------------------|-----------------|-------|-------|-------|------|

| VTXP10 | TX Transmit Peak Voltage |                 | 1.045 | 1.1   | 1.155 | ٧    |

| VTXP11 | TX Transmit Peak Voltage |                 | 1.021 | 1.075 | 1.128 | ٧    |

| VTXP12 | TX Transmit Peak Voltage |                 | 0.998 | 1.05  | 1.102 | ٧    |

| VTXP13 | TX Transmit Peak Voltage |                 | 0.974 | 1.025 | 1.076 | ٧    |

| VTXP14 | TX Transmit Peak Voltage |                 | 0.95  | 1     | 1.05  | ٧    |

| VTXP15 | TX Transmit Peak Voltage |                 | 0.903 | 0.95  | 0.997 | V    |

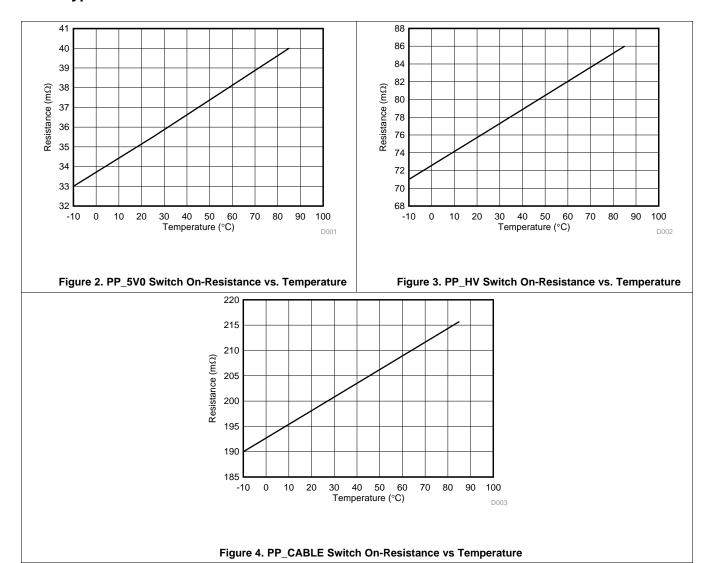

### 7.11 Port Power Switch Characteristics

|                       | PARAMETER                                                         | TEST CONDITIONS <sup>(1)</sup> | MIN   | TYP   | MAX   | UNIT |

|-----------------------|-------------------------------------------------------------------|--------------------------------|-------|-------|-------|------|

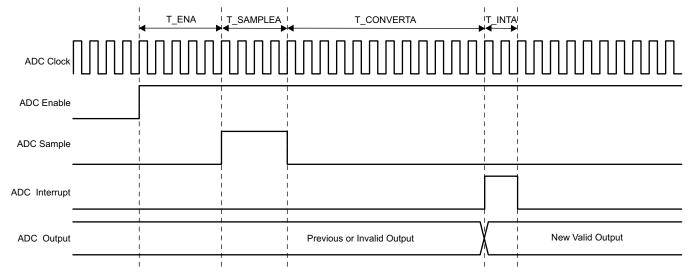

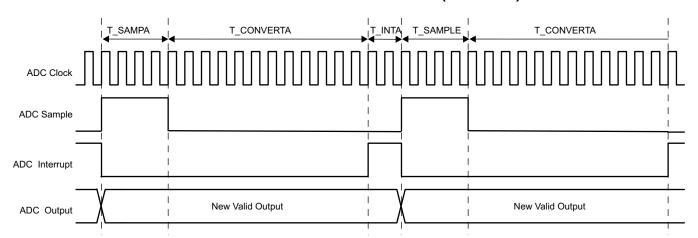

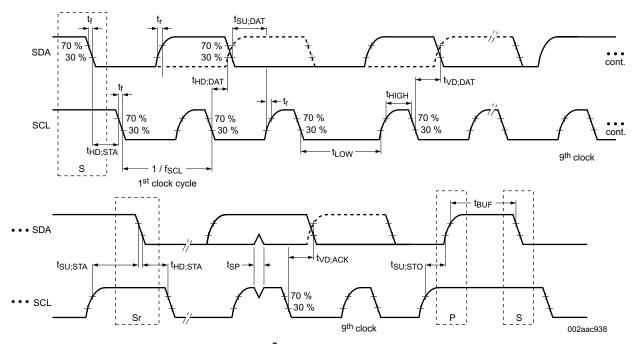

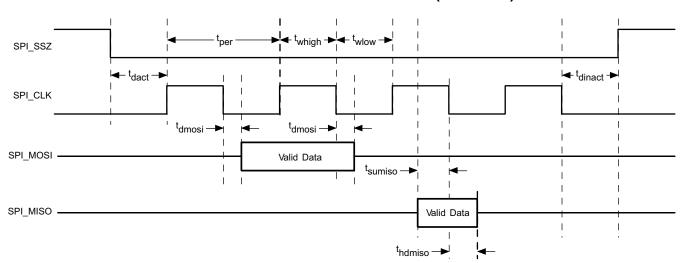

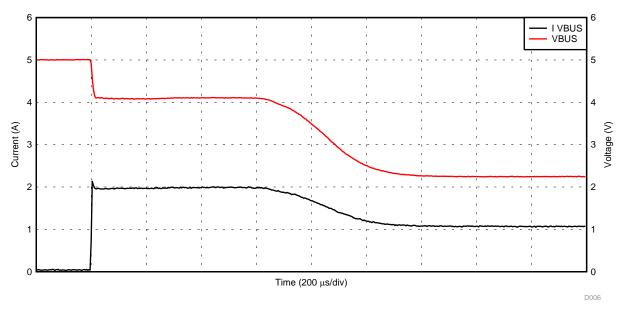

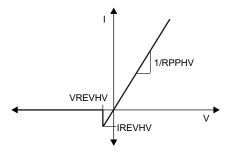

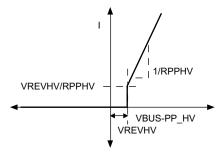

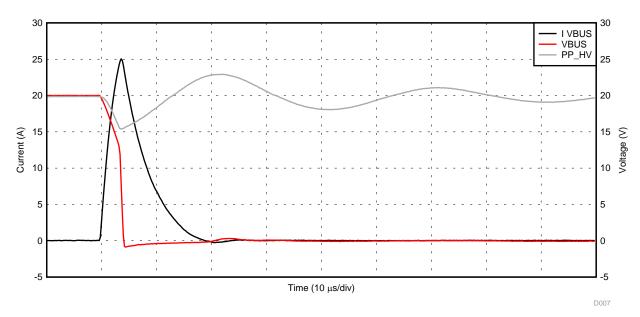

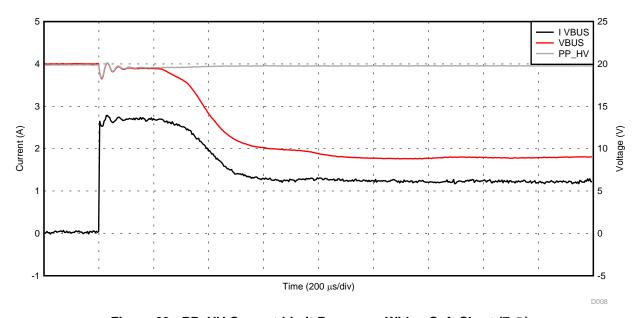

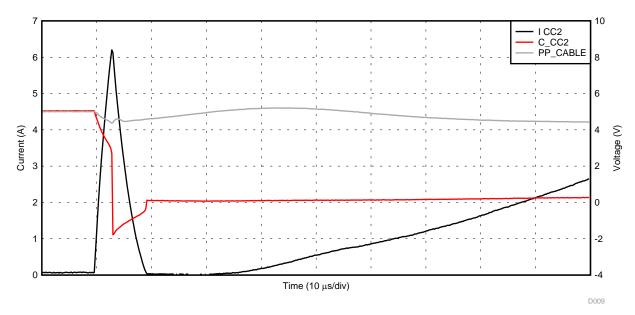

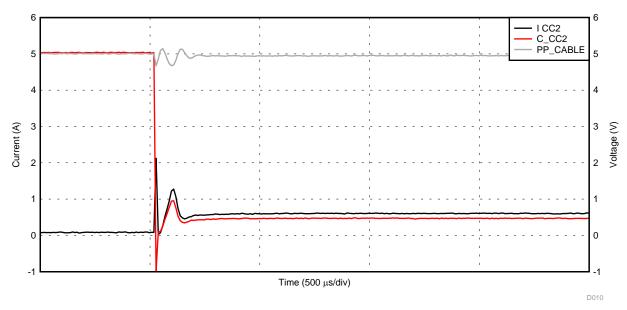

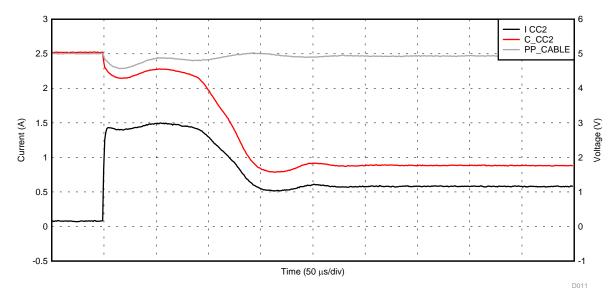

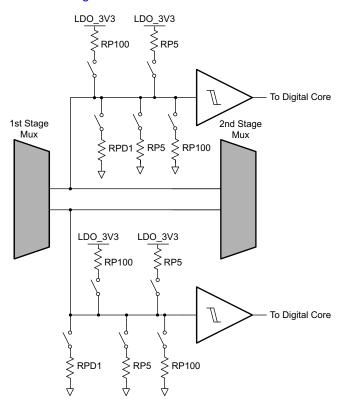

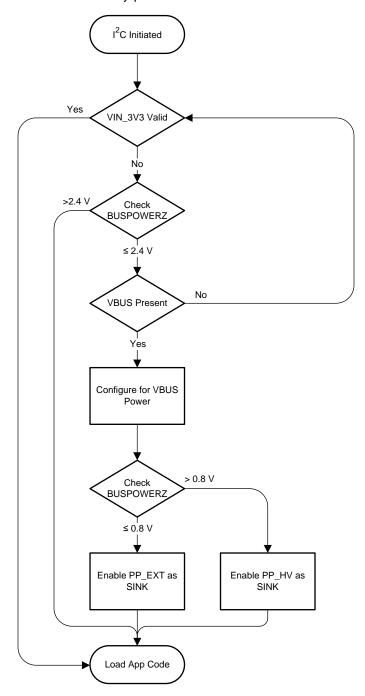

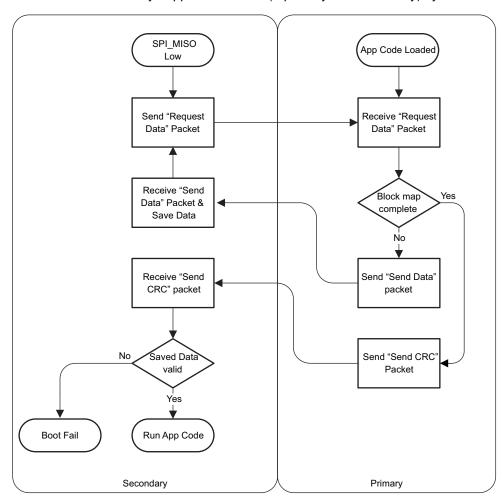

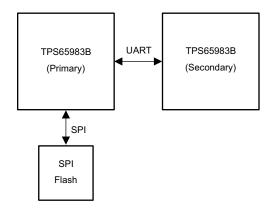

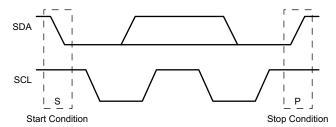

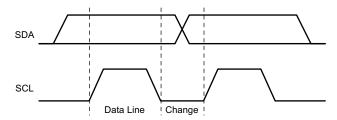

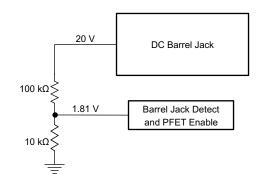

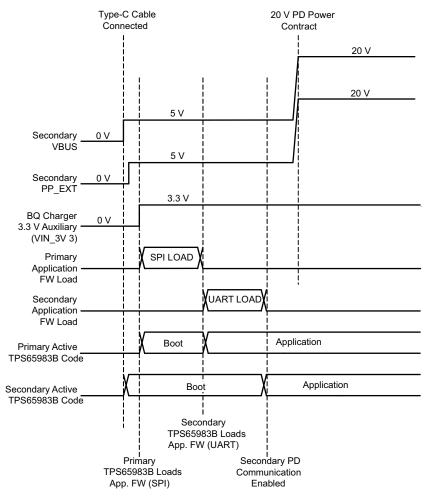

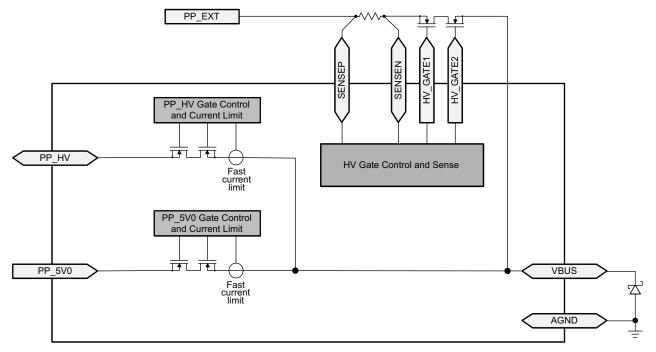

| RPPCC                 | PP_CABLE to C_CCn power switch resistance                         |                                |       |       | 312   | mΩ   |