## **TPS54325-Q1** ZHCS048 – JUNE 2011

# **4.5V**至**18V、3A**输出同步降压转换开关

具有集成 FET (SWIFT™)

查询样品: TPS54325-Q1

# 特性

- 符合汽车应用要求

- **D-CAP2™**模式支持快速瞬态响应

- 低输出纹波,支持陶瓷输出电容器

- 宽 V<sub>CC</sub> 输入电压范围: 4.5V 至 18V

- 宽 V<sub>IN</sub> 输入电压范围: 2.0V 至 18V

- 输出电压范围: 0.76V 至 5.5V

- 高效集成 FET,针对 更低占空比应用进行优化

–120mΩ(高侧)和 70mΩ(低侧)

- 关断时的高效率, 流耗不足 10 µA

- 初始带隙参考的高精度

- 可调软启动

- 预偏置软启动

- 700kHz 开关频率 (f<sub>sw</sub>)

- 逐周期限流

• 电源良好输出

应用

- 用于低电压系统的广泛应用

- 数字电视电源

- 高清 蓝光光盘™ 播放器

- 网络家庭终端设备

- 数字机顶盒(STB)

# 说明

TPS54325-Q1 是一款自适应接通时间 D-CAP2™ 模式同步降压转换器。TPS54325-Q1 可帮助系统设计人员通过 低成本、低组件数量的低待机电流解决方案来完成各种终端设备的电源总线调节器集。TPS54325-Q1 的主控制环 路采用 D-CAP2™ 模式控制,无需外部组件便可实现极快的瞬态响应。此外,TPS54325-Q1 的专有电路还有助于 该器件适应诸如 POSCAP 或 SP-CAP 等低等效串联电阻 (ESR) 输出电容器以及超低 ESR 陶瓷电容器。该设备在 4.5V 至 18V VCC 输入电压下工作,而输入电源电压为 2.0V 至 18V VIN。输出电压可在 0.76V 与 5.5V 之间进行 编程。此外,该器件还支持可调慢启动时间与电源良好功能。TPS54325-Q1 采用 14 引脚 HTSSOP 封装,设计 用于在 \_40°C 至 105°C 的范围下工作。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SWIFT, D-CAP2, PowerPAD are trademarks of Texas Instruments. 蓝光光盘 is a trademark of Blu-ray Disc.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# TPS54325-Q1

ZHCS048-JUNE 2011

Texas Instruments

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**<sup>(1)</sup>

| T <sub>A</sub> | PACKA                       | AGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|-----------------------------|--------------------|-----------------------|------------------|--|

| –40°C to 105°C | PowerPAD™<br>(HTSSOP) – PWP | Reel of 2000       | TPS54325TPWPRQ1       | 54325Q1          |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                   |                                |                                           | VALUE       | UNIT |

|-------------------|--------------------------------|-------------------------------------------|-------------|------|

| VI                |                                | V <sub>IN</sub> , V <sub>CC</sub> , EN    | -0.3 to 20  | V    |

|                   |                                | V <sub>BST</sub>                          | -0.3 to 26  | V    |

|                   | Input voltogo rongo            | V <sub>BST</sub> (vs SW1, SW2)            | -0.3 to 6.5 | V    |

|                   | Input voltage range            | V <sub>FB</sub> , V <sub>O</sub> , SS, PG | -0.3 to 6.5 | V    |

|                   |                                | SW1, SW2                                  | -2 to 20    | V    |

|                   |                                | SW1, SW2 (10 ns transient)                | -3 to 20    | V    |

|                   |                                | V <sub>REG5</sub>                         | -0.3 to 6.5 | V    |

| Vo                | Output voltage range           | P <sub>GND1</sub> , P <sub>GND2</sub>     | -0.3 to 0.3 | V    |

| V <sub>diff</sub> | Voltage from GND to POWERPAD   |                                           | -0.2 to 0.2 | V    |

|                   | Electrostatio discharge        | Human Body Model (HBM)                    | 2           | kV   |

| ESD rating        | Electrostatic discharge        | Charged Device Model (CDM)                | 1000        | V    |

| TJ                | Operating junction temperature |                                           | -40 to 150  | °C   |

| T <sub>stg</sub>  | Storage temperature            |                                           | -55 to 150  | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# THERMAL INFORMATION

|                    |                                              | TPS54325-Q1 |       |  |

|--------------------|----------------------------------------------|-------------|-------|--|

|                    | THERMAL METRIC <sup>(1)</sup>                | PWP         | UNITS |  |

|                    |                                              | 14 PINS     | 1     |  |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance       | 46.3        |       |  |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 1.7         |       |  |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance         | 31.1        | °C/W  |  |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 36.6        | C/W   |  |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 7.2         |       |  |

| $\theta_{JCbot}$   | Junction-to-case (bottom) thermal resistance | 31.4        |       |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range, VCC, VIN = 12V (unless otherwise noted)

|                |                                |                                       | MIN  | MAX | UNIT |  |

|----------------|--------------------------------|---------------------------------------|------|-----|------|--|

| $V_{CC}$       | Supply input voltage range     |                                       | 4.5  | 18  | V    |  |

| $V_{IN}$       | Power input voltage range      | Power input voltage range             |      |     |      |  |

|                |                                | V <sub>BST</sub>                      | -0.1 | 24  |      |  |

|                |                                | V <sub>BST</sub> (vs SW1, SW2)        | -0.1 | 6   |      |  |

|                |                                | SS, PG                                | -0.1 | 6   |      |  |

| V              |                                | EN                                    | -0.1 | 18  | V    |  |

| VI             | Input voltage range            | V <sub>O</sub> , V <sub>FB</sub>      | -0.1 | 5.5 |      |  |

|                |                                | SW1, SW2                              | -1.8 | 18  |      |  |

|                |                                | SW1, SW2 (10 ns transient)            | -3   | 18  |      |  |

|                |                                | P <sub>GND1</sub> , P <sub>GND2</sub> | -0.1 | 0.1 |      |  |

| Vo             | Output voltage range           | V <sub>REG5</sub>                     | -0.1 | 6   | V    |  |

| lo             | Output Current range           | I <sub>VREG5</sub>                    | 0    | 10  | mA   |  |

| T <sub>A</sub> | Operating free-air temperature |                                       | -40  | 105 | °C   |  |

| TJ             | Operating junction temperature |                                       | -40  | 125 | °C   |  |

# **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                | TEST CONDITIONS                                                              | MIN  | TYP     | MAX  | UNIT       |  |

|----------------------|------------------------------------------|------------------------------------------------------------------------------|------|---------|------|------------|--|

| SUPPLY               | CURRENT                                  | I I                                                                          |      |         | L    |            |  |

| I <sub>VCC</sub>     | Operating - non-switching supply current | $V_{CC}$ current, $T_A = 25^{\circ}C$ , $EN = 5 V$ ,<br>$V_{FB} = 0.8 V$     |      | 850     | 1300 | μA         |  |

| IVCCSDN              | Shutdown supply current                  | $V_{CC}$ current, $T_A = 25^{\circ}C$ , EN = 0 V                             |      |         | 10   | μA         |  |

| LOGIC TI             | HRESHOLD                                 |                                                                              |      |         | ·    |            |  |

| V <sub>ENH</sub>     | EN high-level input voltage              | EN                                                                           | 2    |         |      | V          |  |

| V <sub>ENL</sub>     | EN low-level input voltage               | EN                                                                           |      |         | 0.4  | V          |  |

| V <sub>FB</sub> VOL1 | TAGE AND DISCHARGE RESISTANC             | E                                                                            |      |         |      |            |  |

|                      |                                          | $T_A = 25^{\circ}C, V_O = 1.05 V$                                            | 757  | 765     | 775  |            |  |

| V <sub>FBTH</sub>    | V <sub>FB</sub> threshold voltage        | $T_A = 0^{\circ}C$ to 105°C, $V_O = 1.05 V^{(1)}$                            | 753  |         | 777  | mV         |  |

|                      |                                          | $T_A = -40^{\circ}C$ to 105°C, $V_O = 1.05 V^{(1)}$                          | 750  |         | 780  |            |  |

| I <sub>VFB</sub>     | V <sub>FB</sub> input current            | V <sub>FB</sub> = 0.8 V, T <sub>A</sub> = 25°C                               |      | 0       | ±0.1 | μA         |  |

| R <sub>Dischg</sub>  | V <sub>O</sub> discharge resistance      | EN = 0 V, V <sub>O</sub> = 0.5 V, T <sub>A</sub> = 25°C                      |      | 50      | 100  | Ω          |  |

| V <sub>REG5</sub> OU | JTPUT                                    |                                                                              |      |         |      |            |  |

| V <sub>VREG5</sub>   | V <sub>REG5</sub> output voltage         | $T_A = 25^{\circ}C, 6.0 V < V_{CC} < 18 V,$<br>0 < I <sub>VREG5</sub> < 5 mA | 5.3  | 5.5     | 5.7  | V          |  |

| V <sub>LN5</sub>     | Line regulation                          | 6.0 V < V <sub>CC</sub> < 18 V, I <sub>VREG5</sub> = 5 mA                    |      |         | 20   | mV         |  |

| $V_{LD5}$            | Load regulation                          | 0 mA < I <sub>VREG5</sub> < 5 mA                                             |      |         | 100  | mV         |  |

| I <sub>VREG5</sub>   | Output current                           | $V_{CC} = 6 V, V_{REG5} = 4.0 V, T_A = 25^{\circ}C$                          |      | 70      |      | mA         |  |

| MOSFET               |                                          |                                                                              |      |         | ·    |            |  |

| R <sub>dsonh</sub>   | High side switch resistance              | 25°C, V <sub>BST</sub> - SW1, SW2 = 5.5 V                                    |      | 120     |      | mΩ         |  |

| R <sub>dsonl</sub>   | Low side switch resistance               | 25°C                                                                         |      | 70      |      | mΩ         |  |

| CURREN               | T LIMIT                                  |                                                                              |      |         | Ľ    |            |  |

|                      | Current limit                            | $T_A = 25^{\circ}C$ to $105^{\circ}C$                                        | 3.5  | 3.5 4.1 |      | ^          |  |

| l <sub>ocl</sub>     | Current limit                            | $T_A = -40^{\circ}C$                                                         | 3.25 | 3.5     |      | A          |  |

| THERMA               | L SHUTDOWN                               |                                                                              |      |         |      |            |  |

| <b>-</b>             |                                          | Shutdown temperature <sup>(1)</sup>                                          |      | 150     |      | ° <b>0</b> |  |

| T <sub>SDN</sub>     | Thermal shutdown threshold               | Hysteresis <sup>(1)</sup>                                                    |      | 25      |      | °C         |  |

(1) Not production tested.

ZHCS048-JUNE 2011

NSTRUMENTS

ÈXAS

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                 | TEST CONDITIONS                                 | MIN                               | TYP  | MAX  | UNIT |  |

|---------------------------------|---------------------------|-------------------------------------------------|-----------------------------------|------|------|------|--|

| ON-TIME 1                       |                           |                                                 |                                   |      | L.   |      |  |

| T <sub>ON</sub>                 | On time                   | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 1.05 V |                                   | 145  |      | ns   |  |

| T <sub>OFF(MIN)</sub>           | Minimum off time          | $T_A = 25^{\circ}C, V_{FB} = 0.7 V$             |                                   | 260  |      | ns   |  |

| SOFT STA                        | RT                        |                                                 |                                   |      | ·    |      |  |

| I <sub>SSC</sub>                | SS charge current         | $V_{SS} = 0 V$                                  | 1.4                               | 2.0  | 2.6  | μA   |  |

| I <sub>SSD</sub>                | SS discharge current      | $V_{SS} = 0.5 V$                                | 0.1                               | 0.2  |      | mA   |  |

| POWER G                         | OOD                       |                                                 |                                   |      |      |      |  |

|                                 | DC three hold             | V <sub>FB</sub> rising (good)                   | 85                                | 90   | 95   | %    |  |

| V <sub>THPG</sub>               | PG threshold              | V <sub>FB</sub> falling (fault)                 |                                   | 85   |      | 70   |  |

| I <sub>PG</sub> PG sink current |                           | PG = 0.5 V                                      | 2.5                               | 5    |      | mA   |  |

| Ουτρυτ ι                        | INDERVOLTAGE AND OVERVO   | LTAGE PROTECTION                                |                                   |      | ·    |      |  |

| V <sub>OVP</sub>                | Output OVP trip threshold | OVP detect                                      | 115                               | 120  | 125  | %    |  |

| TOVPDEL                         | Output OVP prop delay     |                                                 |                                   | 5    |      | μs   |  |

| M                               |                           | UVP detect                                      | 65                                | 70   | 75   | 0/   |  |

| V <sub>UVP</sub>                | Output UVP trip threshold | Hysteresis                                      |                                   | 10   |      | %    |  |

| T <sub>UVPDEL</sub>             | Output UVP delay          |                                                 |                                   | 0.25 |      | ms   |  |

| T <sub>UVPEN</sub>              | Output UVP enable delay   | Relative to soft-start time                     | Relative to soft-start time x 1.7 |      |      |      |  |

| UVLO                            |                           | ·                                               |                                   |      |      |      |  |

| \ <i>\</i>                      | 1.11/1 O thread and       | Wake up V <sub>REG5</sub> voltage               | 3.45                              | 3.70 | 3.95 | N/   |  |

| V <sub>UVLO</sub>               | UVLO threshold            | Hysteresis V <sub>REG5</sub> voltage            | 0.15                              | 0.25 | 0.35 | 5 V  |  |

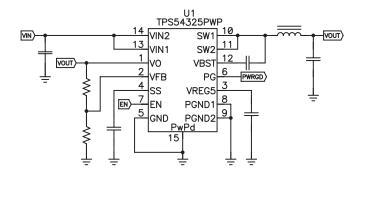

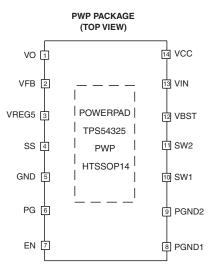

# **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

|       | TERMINAL | DESCRIPTION                                                                      |  |  |  |

|-------|----------|----------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.      | DESCRIPTION                                                                      |  |  |  |

| VO    | 1        | Connect to output of converter. This terminal is used for On-Time Adjustment.    |  |  |  |

| VFB   | 2        | Converter feedback input. Connect with feedback resistor divider.                |  |  |  |

| VREG5 | 3        | 5.5 V power supply output. A capacitor (typical 1µF) should be connected to GND. |  |  |  |

| SS    | 4        | Soft-start control. A external capacitor should be connected to GND.             |  |  |  |

| GND   | 5        | Signal ground pin                                                                |  |  |  |

# **TPS54325-Q1** ZHCS048 – JUNE 2011

# **TERMINAL FUNCTIONS (continued)**

| TERMIN                    | IAL       | DESCRIPTION                                                                                                                                                                                  |  |  |  |  |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO.                  |           | DESCRIPTION                                                                                                                                                                                  |  |  |  |  |

| PG                        | 6         | Open drain power good output                                                                                                                                                                 |  |  |  |  |

| EN 7 Enable control input |           |                                                                                                                                                                                              |  |  |  |  |

| PGND1, PGND2              | 8, 9      | Ground returns for low-side MOSFET. Also serve as inputs of current comparators. Connect PGND and GND strongly together near the IC.                                                         |  |  |  |  |

| SW1, SW2 10, 11           |           | Switch node connection between high-side NFET and low-side NFET. Also serve as inputs to current comparators.                                                                                |  |  |  |  |

| VBST                      | 12        | Supply input for high-side NFET gate driver (boost terminal). Connect capacitor from this pin to respective SW1, SW2 terminals. An internal PN diode is connected between VREG5 to VBST pin. |  |  |  |  |

| VIN                       | 13        | Power input and connected to high side NFET drain                                                                                                                                            |  |  |  |  |

| VCC 14                    |           | Supply input for 5 V internal linear regulator for the control circuitry                                                                                                                     |  |  |  |  |

| PowerPAD™                 | Back side | Thermal pad of the package. Must be soldered to achieve appropriate dissipation. Should be connected to PGND.                                                                                |  |  |  |  |

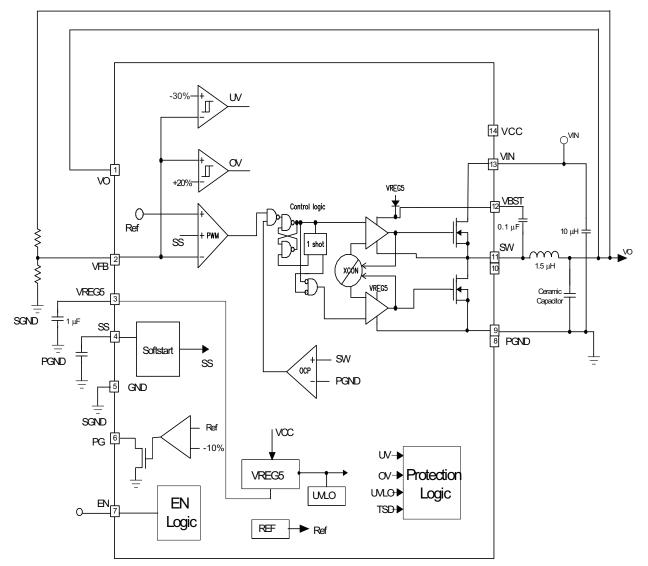

# FUNCTIONAL BLOCK DIAGRAM

### OVERVIEW

The TPS54325-Q1 is a 3-A synchronous step-down (buck) converter with two integrated N-channel MOSFETs. It operates using D-CAP2<sup>™</sup> mode control. The fast transient response of D-CAP2<sup>™</sup> control reduces the output capacitance required to meet a specific level of performance. Proprietary internal circuitry allows the use of low ESR output capacitors including ceramic and special polymer types.

#### **DETAILED DESCRIPTION**

#### **PWM Operation**

The main control loop of the TPS54325-Q1 is an adaptive on-time pulse width modulation (PWM) controller that supports a proprietary D-CAP2<sup>™</sup> mode control. D-CAP2<sup>™</sup> mode control combines constant on-time control with an internal compensation circuit for pseudo-fixed frequency and low external component count configuration with both low ESR and ceramic output capacitors. It is stable even with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off after internal one shot timer expires. This one shot timer is set by the converter input voltage ,VIN, and the output voltage ,VO, to maintain a pseudo-fixed frequency over the input voltage range, hence it is called adaptive on-time control. The one-shot timer is reset and the high-side MOSFET is turned on again when the feedback voltage falls below the reference voltage. An internal ramp is added to the reference voltage to simulate output ripple, eliminating the need for ESR induced output ripple from D-CAP2<sup>™</sup> mode control.

#### **PWM Frequency and Adaptive On-Time Control**

TPS54325-Q1 uses an adaptive on-time control scheme and does not have a dedicated on board oscillator. The TPS54325-Q1 runs with a pseudo-constant frequency of 700 kHz by using the input voltage and output voltage to set the on-time one-shot timer. The on-time is inversely proportional to the input voltage and proportional to the output voltage, therefore, when the duty ratio is VOUT/VIN, the frequency is constant.

#### Soft Start and Pre-Biased Soft Start

The TPS54325-Q1 has an adjustable soft start . When the EN pin becomes high, 2.0- $\mu$ A current begins charging the capacitor which is connected from the SS pin to GND. Smooth control of the output voltage is maintained during start up. The equation for the slow start time is shown in Equation 1. VFB voltage is 0.765 V and SS pin source current is 2  $\mu$ A.

$$Tss(ms) = \frac{C6(nF) \cdot Vref}{Iss(\mu A)} = \frac{C6(nF) \cdot 0.765}{2}$$

(1)

The TPS54325-Q1 contains a unique circuit to prevent current from being pulled from the output during startup in the condition the output is pre-biased. When the soft-start commands a voltage higher than the pre-bias level (internal soft start becomes greater than feedback voltage ( $V_{FB}$ ), the controller slowly activates synchronous rectification by starting the first low side FET gate driver pulses with a narrow on-time. It then increments that on-time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This scheme prevents the initial sinking of the pre-bias output, and ensure that the out voltage (VO) starts and ramps up smoothly into regulation and the control loop is given time to transition from pre-biased start-up to normal mode operation.

#### Power Good

The TPS54325-Q1 has power-good output. The power-good function is activated after soft start has finished. If the output voltage becomes within -10% of the target value, internal comparators detect power good state and the power good signal becomes high. During start up, power good start after 1.7 times soft-start time to avoid a glitch of power-good signal. If the feedback voltage goes under 15% of the target value, the power good signal becomes low after 10 µs internal delay.

#### **Output Discharge Control**

The TPS54325-Q1 discharges the output when EN is low, or the controller is turned off by the protection functions (OVP, UVP, UVLO and thermal shutdown). The device discharges outputs using an internal 50- $\Omega$  MOSFET which is connected to VO and PGND. The internal low-side MOSFET is not turned on during the output discharge operation to avoid the possibility of causing negative voltage at the output.

#### **Current Protection**

The TPS54325-Q1 has cycle-by-cycle over current limiting control. The inductor current is monitored during the OFF state and the controller keeps the OFF state when the inductor current is larger than the over current trip level. In order to provide both good accuracy and cost effective solution, the device supports temperature compensated internal MOSFET  $R_{DS(on)}$  sensing.

The inductor current is monitored by the voltage between PGND pin and SW1/SW2 pin. In an over current condition, the current to the load exceeds the current to the output capacitor; thus the output voltage tends to fall off. Eventually, it will end up with crossing the under voltage protection threshold and shutdown.

#### **Over/Under Voltage Protection**

The TPS54325-Q1 monitors a resistor divided feedback voltage to detect over and under voltage. When the feedback voltage becomes higher than 120% of the target voltage, the OVP comparator output goes high and the circuit latches the high-side MOSFET driver turns off and the low-side MOSFET turns on.

When the feedback voltage becomes lower than 70% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins. After 250  $\mu$ s, the device latches off both internal top and bottom MOSFET. This function is enabled approximately 1.7 x soft-start time.

#### **UVLO Protection**

The TPS54325-Q1 has under voltage lock out protection (UVLO) that monitors the voltage of  $V_{REG5}$  pin. When the  $V_{REG5}$  voltage is lower than UVLO threshold voltage, the TPS54325-Q1 is shut off. This is non-latch protection.

#### **Thermal Shutdown**

The TPS54325-Q1 monitors the temperature of itself. If the temperature exceeds the threshold value (typically 150°C), the device is shut off. This is non-latch protection.

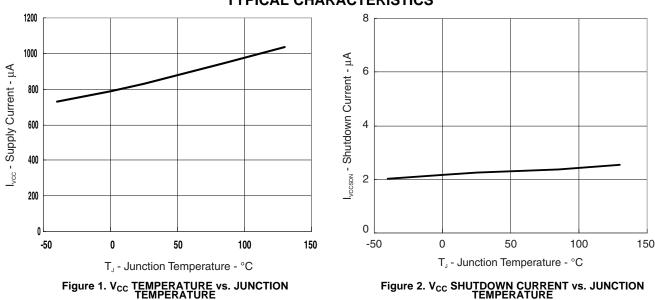

## **TYPICAL CHARACTERISTICS**

**TPS54325-Q1** ZHCS048 – JUNE 2011

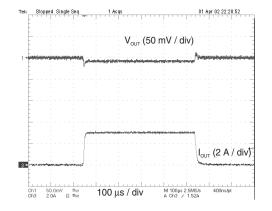

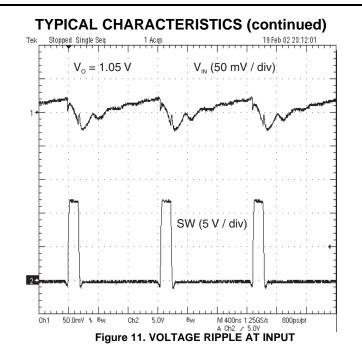

**TYPICAL CHARACTERISTICS (continued)** 1.100 1.100 1.075 1.075 Vout - Output Voltage - V Vour - Output Voltage - V  $I_0 = 0 A$ V = 18 V 1.050 1.050 1  $V_{1} = 12V$ I<sub>0</sub> = 1 A 1.025 1.025 V<sub>1</sub> = 5.5 V 1.000 1.000 5 10 0 15 20 0.0 0.5 1.0 1.5 2.0 2.5 3.0 I<sub>out</sub> - Output Current - A V<sub>IN</sub> - Input Voltage - V Figure 3. 1.05-V OUTPUT VOLTAGE vs. OUTPUT CURRENT Figure 4. 1.05-V OUTPUT VOLTAGE vs. INPUT VOLTAGE Tek Stopped Single 01 Apr 02 22:20:52 V<sub>out</sub> (50 mV / div) EN (10 V / div) V<sub>out</sub> (0.5 V / div) I<sub>out</sub> (2 A / div) PG (5 V / div) 3+ 400 µs / div Ch1 Ch3 50.0m¥ 2.0A M 100µs 2.5MS/s A Ch3 / 1.52A 400ns/p B<sub>W</sub> Ω B<sub>W</sub> 100 µs / div

Figure 6. START-UP WAVE FORM

## TEXAS INSTRUMENTS

www.ti.com.cn

**TYPICAL CHARACTERISTICS (continued)** 100 900  $V_{o} = 3.3 V$ 90 fsw - Switching Frequency - kHz 800 80  $V_{o} = 2.5 V$ Efficiency - % V<sub>o</sub> = 1.8 V V<sub>o</sub> = 1.8 V 70 700 60 600 50 V<sub>o</sub> = 3.3 V 40 500 5 10 20 0 15 0.5 1.5 0.0 1.0 2.0 2.5 3.0 V<sub>IN</sub> - Input Voltage - V I<sub>out</sub> - Output Current - A Figure 7. EFFICIENCY vs. OUTPUT CURRENT ( $V_{IN}$  = 12 V) Figure 8. SWITCHING FREQUENCY vs. INPUT VOLTAGE (I<sub>0</sub>=1 A) 20 Feb 02 01:43:14 900 Tek Stopped Single Seq 1 Acq  $V_{o} = 1.05 V_{o}$ V<sub>o</sub> (10 mV / div) fsw - Switching Frequency - kHz 800 1+  $V_{o} = 1.8 V$ 700  $V_{o} = 2.5 V$ SW (5 V / div) 600 500 M 400ns 1.25GS/s A Ch2 / 1.5V 10.0mY % Bw 800ps/pt 0.0 0.5 1.0 1.5 2.0 2.5 3.0 Ch1 Ch2 5.0Y Βw I<sub>o</sub> - Output Current - A

Figure 9. SWICHING FREQUENCY vs. OUTPUT CURRENT

Figure 10. VOLTAGE RIPPLE AT OUTPUT

TEXAS INSTRUMENTS

www.ti.com.cn

#### **DESIGN GUIDE**

# **TPS54325-Q1** ZHCS048 – JUNE 2011

# Step By Step Design Procedure

To begin the design process, you must define these parameters for your application as follows:

- Input voltage range

- Output voltage

- Output current

- Output voltage ripple

- Input voltage ripple

## **Output Inductor Selection**

The inductance value is selected to provide approximately 30% peak to peak ripple current at maximum load. Larger ripple current increases output ripple voltage, improves S/N ratio and contributes to stable operation. Smaller ripple currents result in lower output voltage ripple. When using low ESR output capacitors output ripple voltage is usually low, so larger ripple currents are acceptable. The coefficient Kind represents the percentage of ripple current. The value of Kind must not be greater than 0.4. Use 0.3 when using low ESR output capacitors. Equation 2 can be used to calculate L1. Use 700 kHz for  $f_{SW}$ . Make sure the chosen inductor is rated for the peak current of Equation 4 and the RMS current of Equation 5.

$$L_o = \frac{V_{OUT}}{V_{IN(max)}} \bullet \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \bullet f_{SW} \bullet Kind}$$

(2)

$$Ilp - p = \frac{V_{OUT}}{V_{IN(max)}} \bullet \frac{V_{IN(max)} - V_{OUT}}{L_0 \bullet f_{SW}}$$

(3)

$$I_{lpeak} = I_o + \frac{Ilp - p}{2} \tag{4}$$

$$I_{Lo(RMS)} = \sqrt{I_o^2 + \frac{1}{12} Ilp - p^2}$$

(5)

#### **Output Capacitor Selection**

The capacitor value and ESR determines the amount of output voltage ripple. Recommended to use ceramic output capacitor. Using Equation 6 to Equation 8, an initial estimate for the capacitor value, ESR, and RMS current can be calculated. If the load transients are significant consider using the load step, instead of ripple current to calculate the maximum ESR. Minimum  $C_0$  should be over 20  $\mu$ F.

$$C_{o} > \frac{1}{8 \bullet f_{SW}} \bullet \frac{1}{\left(\frac{V_{O(ripple)}}{I_{(ripple)}} - R_{ESR}\right)}$$

$$R_{res} < \frac{V_{O(ripple)}}{I_{(ripple)}}$$

(6)

$$I_{ESR} \leftarrow I_{l(ripple)}$$

$$I_{I} = \frac{V_{OUT} \bullet (V_{IN} - V_{OUT})}{V_{OUT} \bullet (V_{IN} - V_{OUT})}$$

(7)

$$I_{CO(RMS)} = \sqrt{12} \bullet V_{IN} \bullet L_O \bullet f_{SW}$$

(8)

#### Input Capacitor Selection

The TPS54325-Q1 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. A ceramic capacitor over 10  $\mu$ F is recommended for the decoupling capacitor. The capacitor voltage rating needs to be greater than the maximum input voltage. In case of separate V<sub>CC</sub> and V<sub>IN</sub>, then a ceramic capacitor over 10  $\mu$ F is recommended for the V<sub>IN</sub> and also placing ceramic capacitor over 0.1  $\mu$ F for the V<sub>CC</sub> is recommended.

# **Bootstrap Capacitor Selection**

A 0.1-µF ceramic capacitor must be connected between the VBST to SW pin for proper operation. It is recommended to use a ceramic capacitor.

### **VREG5** Capacitor Selection

A 1-µF ceramic capacitor must be connected between the VREG5 to GND pin for proper operation. It is recommended to use a ceramic capacitor.

#### **Output Voltage Resistors Selection**

The output voltage is set with a resistor divider from the output node to the VFB pin. It is recommended to use 1% tolerance or better divider resistors. Start by using Equation 9 and Equation 10 to calculate  $V_{OUT}$ .

To improve efficiency at very light loads consider using larger value resistors, too high of resistance will be more susceptible to noise and voltage errors from the VFB input current will be more noticeable.

For output voltage from 0.76 V to 2.5 V:

$V_{OUT} = (0.763 + 0.0017 \cdot V_{OUT}) \cdot \left(1 + \frac{R1}{R2}\right)$

$$V_{OUT} = 0.765 \cdot \left(1 + \frac{R1}{R2}\right)$$

For output voltage over 2.5 V:

τ7

# THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be connected to an external heatsink. The thermal pad must be soldered directly to the printed board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD™ package and how to use the advantage of its heat dissipating abilities, refer to Technical Breif, PowerPAD™ Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD™ Made Easy, Texas Instruments Literature No. SLMA004.

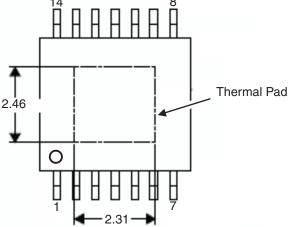

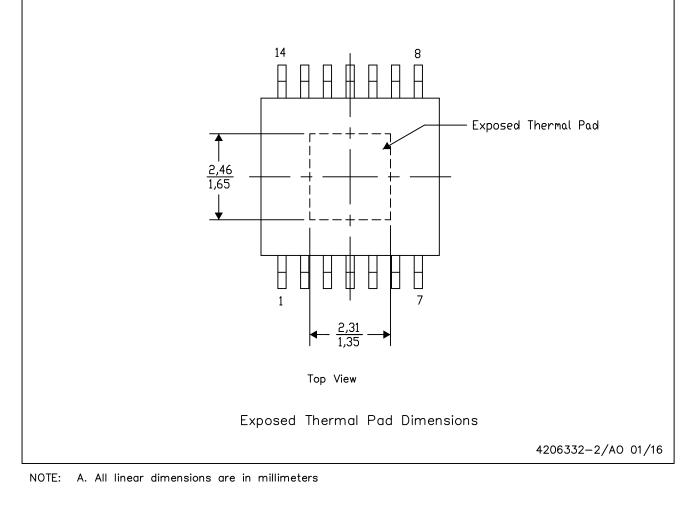

The exposed thermal pad dimensions for this package are shown in the following illustration.

<sup>2 31</sup> Figure 12. Thermal Pad Dimensions

(9)

(10)

www.ti.com.cn

#### LAYOUT CONSIDERATIONS

- 1. Keep the input switching current loop as small as possible.

- 2. Keep the SW node as physically small and short as possible to minimize parasitic capacitance and inductance and to minimize radiated emissions. Kelvin connections should be brought from the output to the feedback pin of the device.

- 3. Keep analog and non-switching components away from switching components.

- 4. Make a single point connection from the signal ground to power ground.

- 5. Do not allow switching current to flow under the device.

- 6. Keep the pattern lines for VIN and PGND broad.

- 7. Exposed pad of device must be connected to PGND with solder.

- 8. VREG5 capacitor should be placed near the device, and connected PGND.

- 9. Output capacitor should be connected to a broad pattern of the PGND.

- 10. Voltage feedback loop should be as short as possible, and preferably with ground shield.

- 11. Lower resistor of the voltage divider which is connected to the VFB pin should be tied to SGND.

- 12. Providing sufficient via is preferable for VIN, SW and PGND connection.

- 13. PCB pattern for VIN, SW, and PGND should be as broad as possible.

- 14. If VIN and VCC is shorted, VIN and VCC patterns need to be connected with broad pattern lines.

- 15. VIN Capacitor should be placed as near as possible to the device.

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | e Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|----------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| TPS54325TPWPRQ1  | ACTIVE        | HTSSOP       | PWP                  | 14   | 2000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 105   | 54325Q1                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

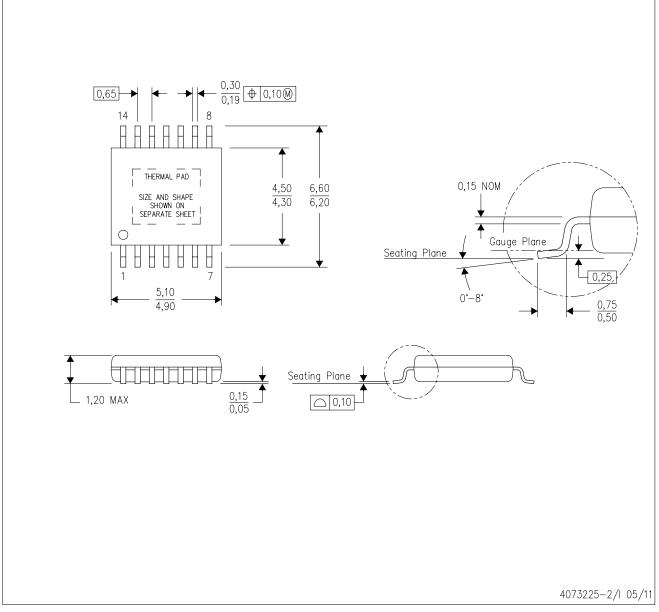

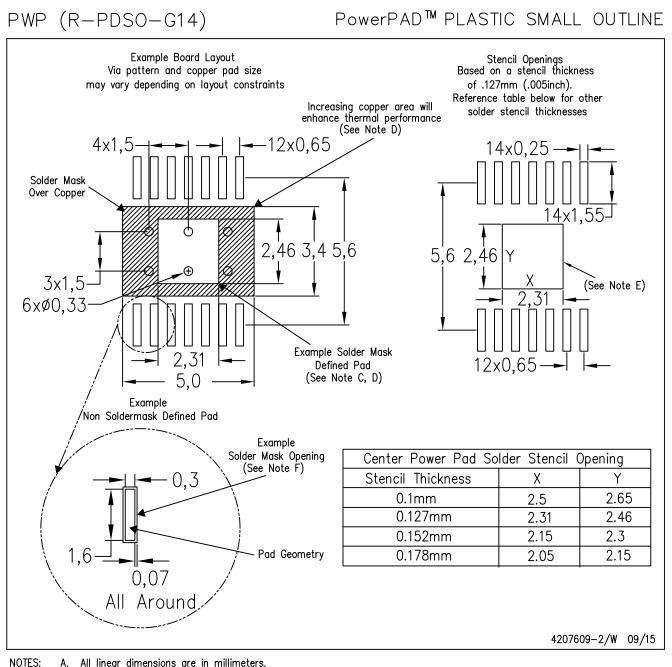

PWP (R-PDSO-G14)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in millimeters.

- This drawing is subject to change without notice. Β.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad

- Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G14) PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

PowerPAD is a trademark of Texas Instruments

NOTES:

A.

- This drawing is subject to change without notice. Β.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D. Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F.

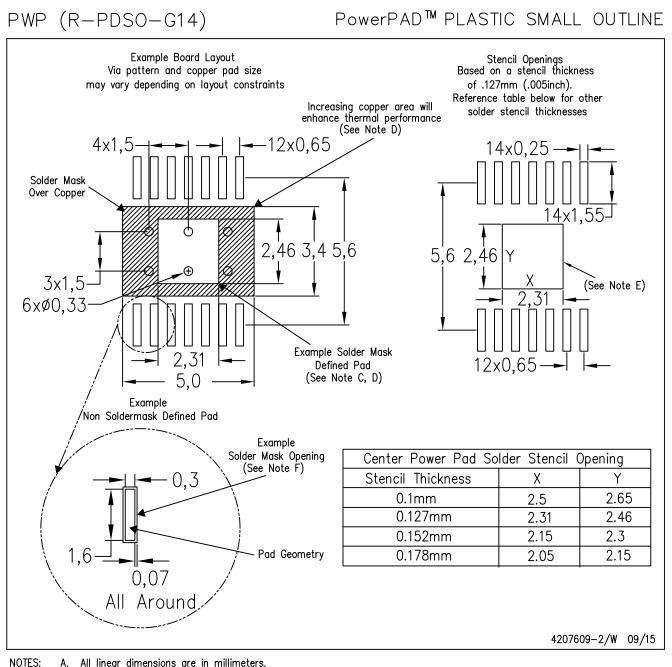

# PWP (R-PDSO-G14) PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE

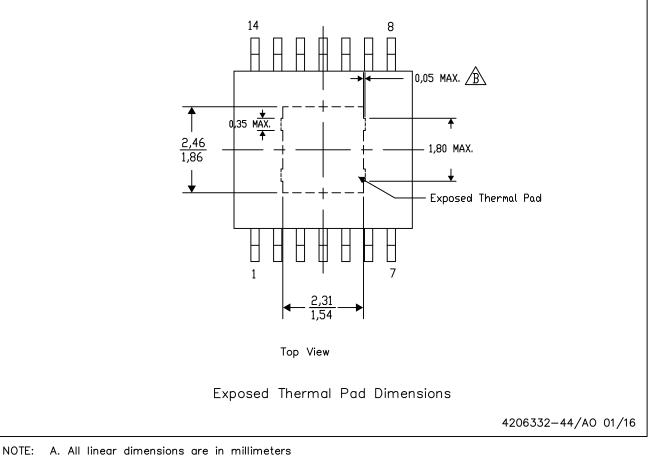

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

A. Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

NOTES:

A.

- This drawing is subject to change without notice. Β.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D. Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F.

#### 重要声明和免责声明

Ⅱ 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、 验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用 所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权 许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司