百盛新纪元半导体 电话:13534212799 00:2851339680

# High Efficiency 1.5MHz 1.2A Synchronous Step Down Converter

## Description

The FP6381A is a high efficiency, high frequency synchronous DC-DC step-down converter. The 100% duty cycle feature provides low dropout operation, extending battery life in portable systems.

The internal synchronous switch increases efficiency and eliminates the need for external Schottky diode. At shutdown mode, the input supply current is less than  $1\mu A$ .

The FP6381A fault protection includes cycle-by-cycle current limit, short circuit protection, UVLO and thermal shutdown. The Internal soft-start function prevents inrush current at turn-on.

The FP6381A is offered in SOT-23-5, TSOT-23-5 and SOT-23-6 Packages

#### Features

- Low  $R_{DS(ON)}$  for Internal Switch (Top/Bottom): 300/250m $\Omega$

- 2.5V~6V Input Voltage Range

- 0.6V Reference Voltage

- 1.2A Output Current

- 1.5MHz Switching Frequency

- Internal 1ms Soft-Start Time

- Internal Compensation Function

- 100% Dropout Operation

- Power Good Indicator Output (SOT-23-6 only)

- RoHS Compliant and Halogen Free

- SOT-23-5, TSOT-23-5 and SOT-23-6 Packages

### Applications

- Set Top Box

- LCD TV & Tablet

- AP Router & WiFi Dongle

- 3.5G & 4G Dongle

- USB3.0 & SSD storage

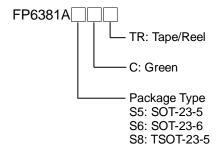

### **Ordering Information**

#### SOT-23-5 Marking

| 0            |              |

|--------------|--------------|

| Part Number  | Product Code |

| FP6381AS5CTR | FA2          |

SOT-23-6 Marking

| Part Number  | Product Code |

|--------------|--------------|

| FP6381AS6CTR | FC4          |

#### TSOT-23-5 Marking

| Part Number  | Product Code |

|--------------|--------------|

| FP6381AS8CTR | FF5          |

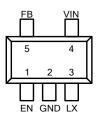

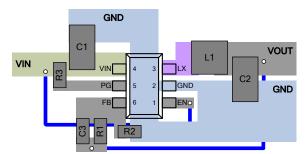

### **Pin Assignments**

#### S5 Package (SOT-23-5)

S6 Package (SOT-23-6)

S8 Package (TSOT-23-5)

Figure 1. Pin Assignment of FP6381A

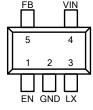

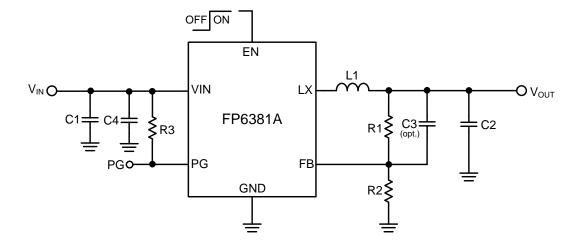

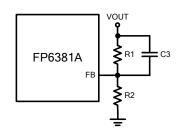

# **Typical Application Circuit**

Figure 2. Schematic Diagram

VIN=5V, the recommended BOM list is as below.

| V <sub>OUT</sub> | C1         | C4         | R1    | R2    | L1    | C2        |

|------------------|------------|------------|-------|-------|-------|-----------|

| 3.3V             | 4.7µF MLCC | 0.1µF MLCC | 453kΩ | 100kΩ | 2.2µH | 10µF MLCC |

| 2.5V             | 4.7µF MLCC | 0.1µF MLCC | 316kΩ | 100kΩ | 2.2µH | 10µF MLCC |

| 1.8V             | 4.7µF MLCC | 0.1µF MLCC | 200kΩ | 100kΩ | 2.2µH | 10µF MLCC |

| 1.5V             | 4.7µF MLCC | 0.1µF MLCC | 150kΩ | 100kΩ | 1.8µH | 10µF MLCC |

| 1.2V             | 4.7µF MLCC | 0.1µF MLCC | 100kΩ | 100kΩ | 1.8µH | 10µF MLCC |

| 1.05V            | 4.7µF MLCC | 0.1µF MLCC | 75kΩ  | 100kΩ | 1.5µH | 10µF MLCC |

Table 1. Recommended Component Values

# **Functional Pin Description**

| Pin Name | Pin No.<br>(SOT-23-5)<br>(TSOT-23-5) | Pin No.<br>(SOT-23-6) | Pin Function                                                                                                                                       |  |  |

|----------|--------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VIN      | 4                                    | 4                     | Power Supply Input Pin. Placed input capacitors as close as possible from VIN to GND to avoid noise influence.                                     |  |  |

| GND      | 2                                    | 2                     | Ground Pin.                                                                                                                                        |  |  |

| EN       | 1                                    | 1                     | Enable Control Pin. Pull high to turn the IC on, and pull low to disable the IC. Don't leave this pin floating.                                    |  |  |

| FB       | 5                                    | 6                     | Voltage Feedback Input Pin. Connect FB and VOUT with a resistive voltage divider. This IC senses feedback voltage via FB and regulates it at 0.6V. |  |  |

| PG       |                                      | 5                     | Open Drain Power Good Output Pin.                                                                                                                  |  |  |

| LX       | 3                                    | 3                     | Power Switching Output. Connect an external inductor to this switching node.                                                                       |  |  |

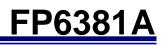

# **Block Diagram**

Figure 3. Block Diagram of FP6381A

# Absolute Maximum Ratings (Note 1)

| • VIN to GND                                                     |

|------------------------------------------------------------------|

| $\bullet$ LX to GND                                              |

| $\bullet$ EN, FB, PG to GND0.3V to V_{IN}                        |

| <ul> <li>Package Thermal Resistance, (θ<sub>JA</sub>)</li> </ul> |

| SOT-23-5 +250°C/W                                                |

| TSOT-23-5 +250°C/W                                               |

| SOT-23-6 +250°C/W                                                |

| <ul> <li>Package Thermal Resistance, (θ<sub>JC</sub>)</li> </ul> |

| SOT-23-5 +130°C/W                                                |

| TSOT-23-5 +130°C/W                                               |

| SOT-23-6 +110°C/W                                                |

| <ul> <li>Maximum Junction Temperature (T<sub>J</sub>)</li></ul>  |

| • Lead Temperature (Soldering, 10sec.)+260°C                     |

| • Storage Temperature (T <sub>S</sub> )                          |

# Recommended Operating Conditions (Note 2)

| • Supply Voltage (V <sub>IN</sub> )                                                 | - +2.5V to +6V |

|-------------------------------------------------------------------------------------|----------------|

| • Operation Temperature Range (T <sub>OPR</sub> )                                   | -40°C to +85°C |

| Note 2 : The device is not guaranteed to function outside its operating conditions. |                |

# **Electrical Characteristics**

(V<sub>IN</sub>=5V, V<sub>OUT</sub>=2.5V, T<sub>A</sub>=25°C, unless otherwise specified.)

| Parameter                                  | Symbol              | Conditions                                   | Min   | Тур  | Max   | Unit |

|--------------------------------------------|---------------------|----------------------------------------------|-------|------|-------|------|

| Shutdown Current                           | I <sub>SHDN</sub>   | EN=0V                                        |       | 0.1  | 1     | μA   |

| Quiescent Current                          | lq                  | V <sub>FB</sub> =0.65V, I <sub>OUT</sub> =0A |       | 80   |       | μA   |

| Reference Voltage                          | V <sub>REF</sub>    |                                              | 0.588 | 0.6  | 0.612 | V    |

| FB Input Leakage Current                   | I <sub>FB</sub>     | V <sub>FB</sub> =V <sub>IN</sub>             |       | 0.01 | 1     | μA   |

| P-Channel MOSFET On-Resistance<br>(Note 3) | R <sub>DS(ON)</sub> |                                              |       | 300  |       | mΩ   |

| N-Channel MOSFET On-Resistance<br>(Note 3) | R <sub>DS(ON)</sub> |                                              |       | 250  |       | mΩ   |

| P-Channel Current Limit (Note 3)           | I <sub>LIM</sub>    |                                              | 1.6   |      |       | А    |

| EN High-Level Input Voltage                | VIH                 |                                              | 1.5   |      |       | V    |

| EN Low-Level Input Voltage                 | VIL                 |                                              |       |      | 0.4   | V    |

| Under Voltage Lockout Voltage              | UVLO                |                                              |       | 2.4  |       | V    |

| UVLO Hysteresis                            | V <sub>HYS</sub>    |                                              |       | 0.2  |       | V    |

| Oscillation Frequency                      | Fosc                | I <sub>OUT</sub> =200mA                      | 1.2   | 1.5  | 1.8   | MHz  |

| Minimum On Time                            |                     |                                              |       | 50   |       | ns   |

| Maximum Duty Cycle                         |                     |                                              | 100   |      |       | %    |

| Internal Soft Start Time                   | T <sub>SS</sub>     |                                              |       | 1    |       | ms   |

| PG Rising Threshold                        | V <sub>PG (H)</sub> | V <sub>FB</sub> Rising                       |       | 90   |       | %    |

| PG Sink Current                            | I <sub>PG</sub>     | V <sub>PG</sub> =0.1V                        |       | 1    |       | mA   |

| LX Discharge Resistance                    |                     |                                              |       | 100  |       | Ω    |

| Thermal Shutdown Temperature<br>(Note 3)   | T <sub>SD</sub>     |                                              |       | 150  |       | °C   |

Note 3 : Guarantee by design.

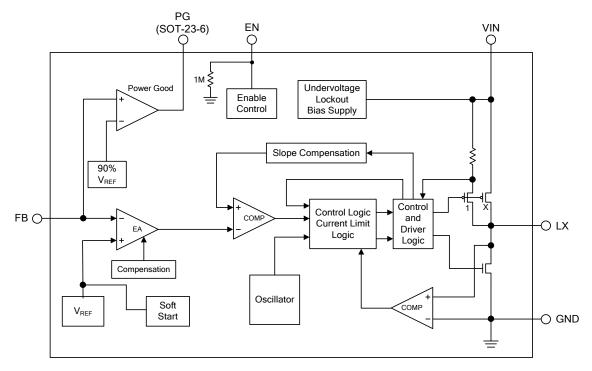

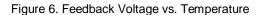

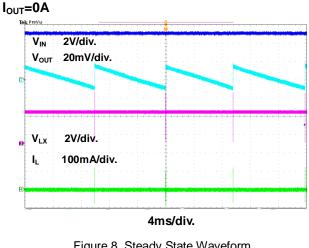

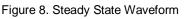

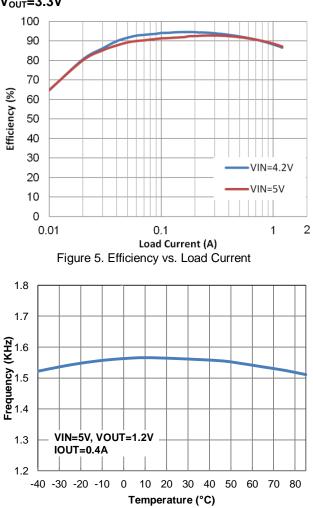

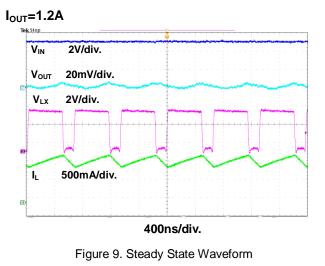

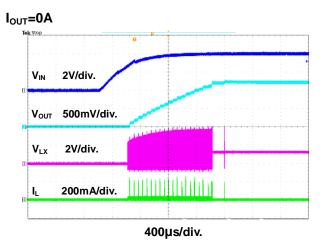

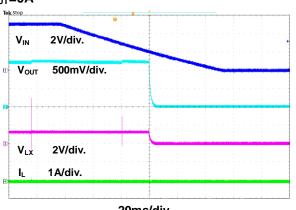

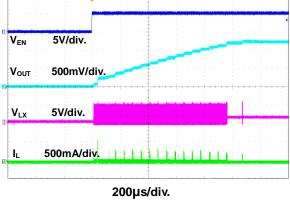

## **Typical Performance Curves**

V<sub>IN</sub>=5V, C1=4.7µF//0.1µF, C2=10µF, C3=22pF, L1=1.8µH, TA=+25°C, unless otherwise noted. V<sub>OUT</sub>=1.2V Vout=3.3V

# FP6381A

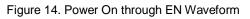

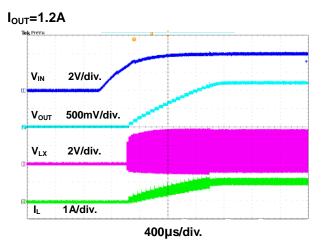

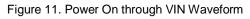

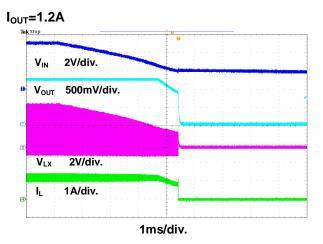

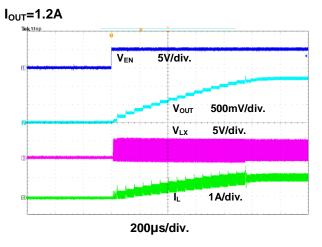

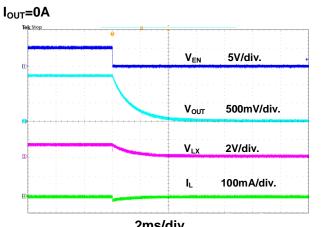

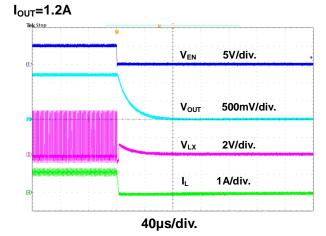

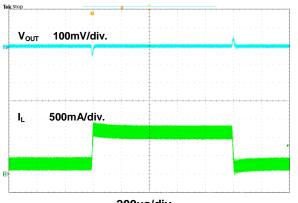

# **Typical Performance Curves (Continued)**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, C1=4.7µF//0.1µF, C2=10µF, C3=22pF, L1=1.8µH, TA=+25°C, unless otherwise noted.

Figure 10. Power On through VIN Waveform

20ms/div.

Figure 12. Power Off through VIN Waveform

Figure 13. Power Off through VIN Waveform

Figure 15. Power On through EN Waveform

# **tipower**

# **FP6381A**

# **Typical Performance Curves (Continued)**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, C1=4.7µF//0.1µF, C2=10µF, C3=22pF, L1=1.8µH, TA=+25°C, unless otherwise noted.

2ms/div.

Figure 16. Power Off through EN Waveform

Figure 17. Power Off through EN Waveform

#### Iout=0.3A to 1.2A

200µs/div.

Figure 18. Load Transient Waveform

# fitipower

# **Function Description**

The FP6381A is a high efficiency, internal compensation and constant frequency current mode step-down synchronous DC/DC converter. It has integrated high-side ( $300m\Omega$ , typ.) and low-side ( $250m\Omega$ , typ.) power switches, and provides 1.2A continuous load current. It regulates input voltage from 2.5V to 6V, and down to an output voltage as low as 0.6V.

#### **Control Loop**

Slope compensated current mode PWM control provides stable switching and cycle-by-cycle current limit for superior load, line response, protection of the internal main switch and synchronous rectifier. The FP6381A switches at a constant frequency (1.5MHz) and regulates the output voltage. During each cycle, comparator modulates the PWM the power transferred to the load by changing the inductor peak current based on the feedback error voltage. During normal operation, the main switch is turned on for a certain time to ramp the inductor current at each rising edge of the internal oscillator, and switched off when the peak inductor current is above the error voltage. When the main switch is off, the synchronous rectifier will be turned on immediately and stay on until next cycle starts.

#### Enable

The FP6381A EN pin provides digital control to turn on/off the regulator. When the voltage of EN exceeds the threshold voltage, the regulator will start the soft start function. If the EN pin voltage is below the shutdown threshold voltage, the regulator will turn into the shutdown mode and the shutdown current will be smaller than  $1\mu$ A. For auto start-up operation, connect EN to VIN.

#### Soft Start

The FP6381A employs internal soft start function to reduce input inrush current during start up. The internal soft start time will be 1ms.

#### **Under Voltage Lockout**

When the FP6381A is power on, the internal circuits will be held inactive until  $V_{IN}$  voltage exceeds the UVLO threshold voltage. And the regulator will be disabled when  $V_{IN}$  is below the UVLO threshold voltage. The hysteretic of the UVLO comparator is 200mV (typ).

#### **Over Current Protection**

The FP6381A over current protection function is implemented by using cycle-by-cycle current limit architecture. The inductor current is monitored by measuring the high-side MOSFET series sense resistor voltage. When the load current increases, the inductor current will also increase. When the peak inductor current reaches the current limit threshold, the output voltage will start to drop. When the over current condition is removed, the output voltage will return to the regulated value.

#### **Short Circuit Protection**

The FP6381A provides short circuit protection function to prevent the device damaged from short condition. When the short condition occurs and the feedback voltage drops lower than 40% of the regulation level, the oscillator frequency will be reduced to prevent the inductor current increasing beyond the current limit. In the meantime, the current limit will also be reduced to lower the short current. Once the short condition is removed, the frequency and current limit will return to normal.

#### **Over Temperature Protection**

The FP6381A incorporates an over temperature protection circuit to protect itself from overheating. When the junction temperature exceeds the thermal shutdown threshold temperature, the regulator will be shutdown. And the hysteretic of the over temperature protection is 30°C (typ).

#### **PG Signal Output**

PG pin is an open-drain output and requires a pull up resistor. PG is actively held low in soft-start, standby and shutdown. It is released when the output voltage rises above 90% of nominal regulation point.

## **Application Information**

#### **Output Voltage Setting**

The output voltage  $V_{OUT}$  is set by using a resistive divider from the output to FB. The FB pin regulated voltage is 0.6V. Thus the output voltage is:

$$V_{OUT}=0.6V \times \left(1+\frac{R1}{R2}\right)$$

Table 2 lists recommended values of R1 and R2 for most used output voltage.

| Table 2 | Recommended Resistance Values |  |

|---------|-------------------------------|--|

|---------|-------------------------------|--|

| V <sub>OUT</sub> | R1    | R2    |

|------------------|-------|-------|

| 3.3V             | 453kΩ | 100kΩ |

| 2.5V             | 316kΩ | 100kΩ |

| 1.8V             | 200kΩ | 100kΩ |

| 1.5V             | 150kΩ | 100kΩ |

| 1.2V             | 100kΩ | 100kΩ |

Place resistors R1 and R2 close to FB pin to prevent stray pickup.

#### **Input Capacitor Selection**

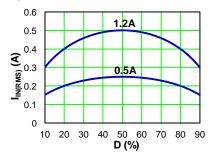

The use of the input capacitor is filtering the input voltage ripple and the MOSFETS switching spike voltage. Because the input current to the step-down converter is discontinuous, the input capacitor is required to supply the current to the converter to keep the DC input voltage. The capacitor voltage rating should be 1.25 to 1.5 times greater than the maximum input voltage. The input capacitor ripple current RMS value is calculated as:

$$I_{\text{IN(RMS)}} = I_{\text{OUT}} \times \sqrt{D \times (1-D)}$$

$$D = \frac{V_{\text{OUT}}}{V_{\text{IN}}}$$

Where D is the duty cycle of the power MOSFET.

This function reaches the maximum value at D=0.5 and the equivalent RMS current is equal to  $I_{OUT}/2$ . The following diagram is the graphical representation of above equation.

A low ESR capacitor is required to keep the noise minimum. Ceramic capacitors are better, but tantalum or low ESR electrolytic capacitors may also suffice.

#### **Output Capacitor Selection**

The output capacitor is used to keep the DC output voltage and supply the load transient current. When operating in constant current mode, the output ripple is determined by four components:

$$V_{RIPPLE}(t) = V_{RIPPLE(C)}(t) + V_{RIPPLE(ESR)}(t) + V_{RIPPLE(ESL)}(t) + V_{NOISE}(t)$$

The following figures show the form of the ripple contributions.

$V_{RIPPLE(ESR)}(t)$ +

(t)  $V_{RIPPLE(ESL)}(t)$ +

(t)  $V_{RIPPLE(C)}(t)$ +

(t)  $V_{RIPPLE(C)}(t)$ +

(t)  $V_{NOISE}(t)$ =  $V_{RIPPLE}(t)$ (t)

FP6381A

## **Application Information (Continued)**

$$V_{\text{RIPPLE(ESR)}} = \frac{V_{\text{OUT}}}{F_{\text{OSC}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \text{ESR}$$

$$V_{\text{RIPPLE(ESL)}} = \frac{\text{ESL}}{L + \text{ESL}} \times V_{\text{IN}}$$

$$V_{\text{RIPPLE(C)}} = \frac{V_{\text{OUT}}}{8 \times F_{\text{OSC}}^2 \times L \times C_{\text{OUT}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

Where  $F_{\rm OSC}$  is the switching frequency, L is the inductance value,  $V_{\rm IN}$  is the input voltage, ESR is the equivalent series resistance value of the output capacitor, ESL is the equivalent series inductance value of the output capacitor and the  $C_{\rm OUT}$  is the output capacitor.

Low ESR capacitors are preferred to use. Ceramic, tantalum or low ESR electrolytic capacitors can be used depending on the output ripple requirements. When using the ceramic capacitors, the ESL component is usually negligible.

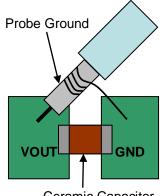

It is important to use the proper method to eliminate high frequency noise when measuring the output ripple. The figure shows how to locate the probe across the capacitor when measuring output ripple. Remove the scope probe plastic jacket in order to expose the ground at the tip of the probe. It gives a very short connection from the probe ground to the capacitor and eliminates noise.

Ceramic Capacitor

#### **Inductor Selection**

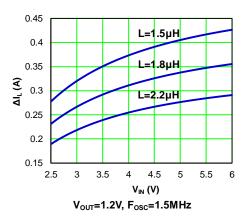

The output inductor is used for storing energy and filtering output ripple current. But the trade-off condition often happens between maximum energy storage and the physical size of the inductor. The first consideration for selecting the output inductor is to make sure that the inductance is large enough to keep the converter in the continuous current mode. That will lower ripple current and result in lower output ripple voltage. The  $\Delta I_{L}$  is inductor peak-to-peak ripple current:

$$\Delta I_{L} = \frac{V_{OUT}}{F_{OSC} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The following diagram is an example to graphically represent  $\Delta I_{\text{L}}$  equation.

A good compromise value between size and efficiency is to set the peak-to-peak inductor ripple current  $\Delta I_{L}$  equal to 30% of the maximum load current. But setting the peak-to-peak inductor ripple current  $\Delta I_{L}$  between 20%~50% of the maximum load current is also acceptable. Then the inductance can be calculated with the following equation:

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times F_{OSC} \times \Delta I_{L}}$$

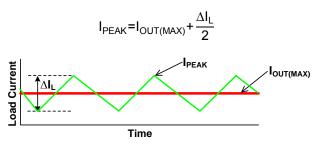

To guarantee sufficient output current, peak inductor current must be lower than the FP6381A high-side MOSFET current limit. The peak inductor current is shown as below:

## **Application Information (Continued)**

#### Feedforward Capacitor Selection

Internal compensation function allows users saving time in design and saving cost by reducing the number of external components. The use of a feedforward capacitor C6 in the feedback network is recommended to improve transient response or higher phase margin.

For optimizing the feedforward capacitor, knowing the cross frequency is the first thing. The cross frequency (or the converter bandwidth) can be determined by using a network analyzer. When getting the cross frequency with no feedforward capacitor identified, the value of feedforward capacitor C6 can be calculated with the following equation:

$$C3 = \frac{1}{2\pi \times F_{CROSS}} \times \sqrt{\frac{1}{R1} \times \left(\frac{1}{R1} + \frac{1}{R2}\right)}$$

Where  $F_{CROSS}$  is the cross frequency.

To reduce transient ripple, the feedforward capacitor value can be increased to push the cross frequency to higher region. Although this can improve transient response, it also decreases phase margin and causes more ringing. In the other hand, if more phase margin is desired, the feedforward capacitor value can be decreased to push the cross frequency to lower region. In general, the feedforward capacitor range is between 10pF to 330pF.

#### **PCB Layout Recommendation**

The device's performance and stability are dramatically affected by PCB layout. It is recommended to follow these general guidelines shown as below:

- 1. Place the input capacitors and output capacitors as close to the device as possible. The traces which connect to these capacitors should be as short and wide as possible to minimize parasitic inductance and resistance.

- 2. Place feedback resistors close to the FB pin.

- 3. Keep the sensitive signal (FB) away from the switching signal (LX).

- 4. Multi-layer PCB design is recommended.

Figure 19. Recommended Layout Diagram

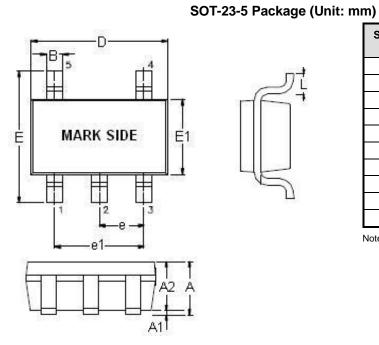

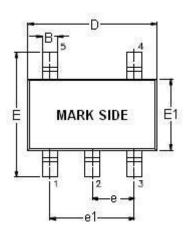

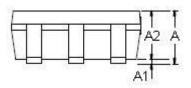

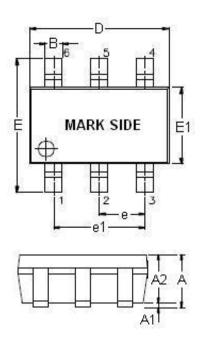

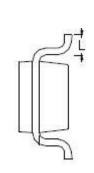

# **Outline Information**

| SYMBOLS | DIMENSION IN MILLIMETER |      |  |  |  |

|---------|-------------------------|------|--|--|--|

| UNIT    | MIN                     | MAX  |  |  |  |

| А       | 0.90                    | 1.45 |  |  |  |

| A1      | 0.00                    | 0.15 |  |  |  |

| A2      | 0.90                    | 1.30 |  |  |  |

| В       | 0.30                    | 0.50 |  |  |  |

| D       | 2.80                    | 3.00 |  |  |  |

| Е       | 2.60                    | 3.00 |  |  |  |

| E1      | 1.50                    | 1.70 |  |  |  |

| e       | 0.90                    | 1.00 |  |  |  |

| e1      | 1.80                    | 2.00 |  |  |  |

| L       | 0.30                    | 0.60 |  |  |  |

Note : Followed From JEDEC MO-178-C.

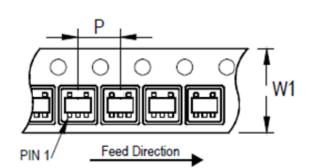

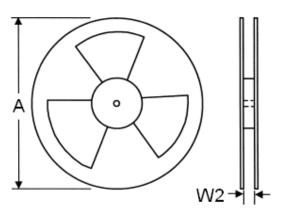

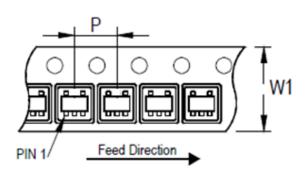

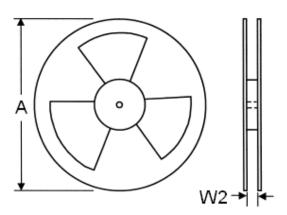

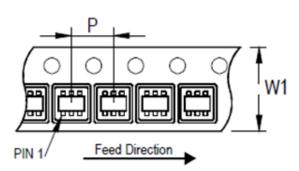

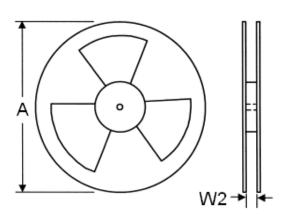

## **Carrier Dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Ca∨ity | Units per Reel |

|-----------|--------------|---------------|-----|------------|--------------|----------------|

| (W1) mm   | (P) mm       | in            | mm  | (W2) mm    | Length mm    |                |

| 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

FP6381A-0.5-SEP-2015

# **Outline Information (Continued)**

TSOT-23-5 Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETER |      |  |

|---------|-------------------------|------|--|

| UNIT    | MIN                     | MAX  |  |

| A       | 0.70                    | 0.90 |  |

| A1      | 0.00                    | 0.10 |  |

| A2      | 0.70                    | 1.00 |  |

| В       | 0.30                    | 0.50 |  |

| D       | 2.80                    | 3.00 |  |

| E       | 2.60                    | 3.00 |  |

| E1      | 1.50                    | 1.70 |  |

| е       | 0.90                    | 1.00 |  |

| e1      | 1.80                    | 2.00 |  |

| L       | 0.30                    | 0.60 |  |

# **Carrier Dimensions**

| [ | Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|---|-----------|--------------|---------------|-----|------------|--------------|----------------|

|   | (W1) mm   | (P)mm        | in            | mm  | (W2) mm    | Length mm    |                |

|   | 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

# **Outline Information (Continued)**

SOT-23-6 Package (Unit: mm)

|         |      | IENSION IN MILLIMETER |  |  |  |

|---------|------|-----------------------|--|--|--|

| SYMBOLS |      |                       |  |  |  |

| UNIT    | MIN  | MAX                   |  |  |  |

| A       | 0.90 | 1.45                  |  |  |  |

| A1      | 0.00 | 0.15                  |  |  |  |

| A2      | 0.90 | 1.30                  |  |  |  |

| В       | 0.30 | 0.50                  |  |  |  |

| D       | 2.80 | 3.00                  |  |  |  |

| E       | 2.60 | 3.00                  |  |  |  |

| E1      | 1.50 | 1.70                  |  |  |  |

| е       | 0.90 | 1.00                  |  |  |  |

| e1      | 1.80 | 2.00                  |  |  |  |

| L       | 0.30 | 0.60                  |  |  |  |

Note : Followed From JEDEC MO-178-C.

### **Carrier Dimensions**

| Γ | Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Ca∨ity | Units per Reel |

|---|-----------|--------------|---------------|-----|------------|--------------|----------------|

|   | (W1) mm   | (P) mm       | in            | mm  | (W2) mm    | Length mm    |                |

|   | 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |