## 100V, 5A, Synchronous Buck Control

#### 1 Features

- 12V to 100V wide operating input range

- 5A continuous output current capability

- Integrated 120V, 17mΩ high side and 120V, 17mΩ low side power MOSFET switches

- Adjustable Frequency from 50kHz to 500kHz Operation

- Precision Reference Voltage (1.2 V)

- Programmable Soft-Start with Pre-biased Load Capability

- Programmable EN Off Delay Function

- Programmable Over-Load Protection with 0.2s blank timer and Hiccup

- Programmable Cycle-by-Cycle Current Limiting Protection

- Programmable Input Under-Voltage Lockout Protection with Latch

- Programmable Input Over-Voltage Protection with

Latch

- Output Over-Voltage Protection

- Over-Temperature Protection

- QFN6\*6mm-48L

## 3 Description

PL8905 is a high voltage Buck Control designed for high performance synchronous Buck DC/DC applications with input voltages up to 100V.

PL8905 integrates a high efficiency synchronous step-down switching regulator, which includes a 120V,  $17m\Omega$  high side and a 120V,  $17m\Omega$  low side MOSFETs to provide 5A continuous load current over12V to 100V wide operating input voltage.

PL8905 switching frequency is programmable from 50 kHz up to 500 kHz allowing the flexibility to tune for efficiency and size. The output voltage can be precisely regulated using the internally 1.2 V reference voltage for low voltage applications.

Protection features include user programmable under voltage lockout, over voltage lockout and over current protection. The supply current drops below 10µA in shutdown mode. PL8905 is a good choice for car infotainment application, telecom bus converter, etc.

### 2 Applications

- 48 V Non-Isolated DC-DC Converter

- Car applications

- Telecom Bus Converters

- General purpose

- USB Type-C Power Delivery

- Industrial DC-DC Motor Drivers

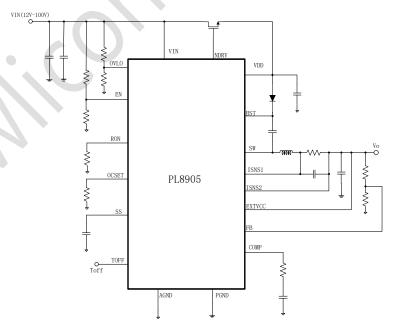

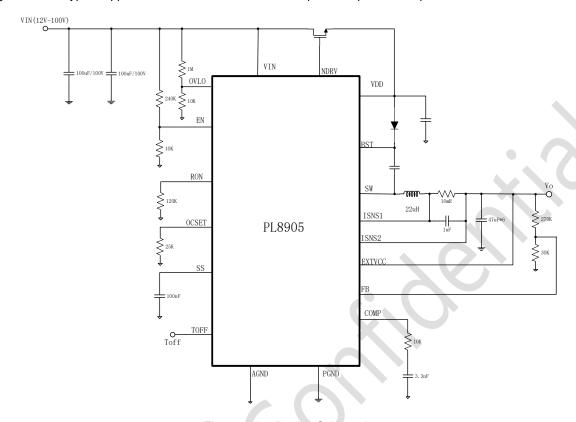

## 4 Typical Application Schematic

Fig. 1 Application Schematic

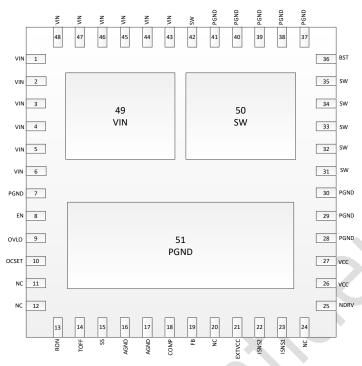

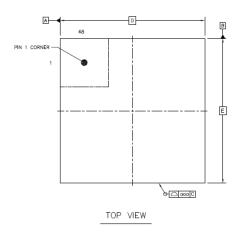

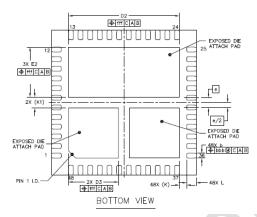

## 5 Pin Configuration and Functions

Fig. 2 QFN6\*6-48L Package (Top View)

| Pin    |                                          | Description                                                                                                                                                                                                                                                                                             |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | Number                                   | Description                                                                                                                                                                                                                                                                                             |

| VIN    | 1,2,3,4,5,6,<br>43,44,45,46,47,<br>48,49 | Input voltage.                                                                                                                                                                                                                                                                                          |

| EN     | 8                                        | Enable pin.                                                                                                                                                                                                                                                                                             |

| OVLO   | 9                                        | An external voltage divider is used to set the over voltage threshold levels.                                                                                                                                                                                                                           |

| OCSET  | 10                                       | Current limit set point. A resistor from this pin to GND will set the positive and negative current limit threshold.                                                                                                                                                                                    |

| RON    | 13                                       | Connect this pin to GND by a resistor to set the switching frequency.                                                                                                                                                                                                                                   |

| TOFF   | 14                                       | This pin provides user programmable shutdown delay time function. Connect to GND: No Delay Connect to VCC: 20s Floating: 10s                                                                                                                                                                            |

| SS     | 15                                       | This pin provides user programmable soft-start function. External capacitor connected from this pin to ground sets the startup time of the output voltage.                                                                                                                                              |

| AGND   | 16,17                                    | Signal ground for internal reference and control circuitry.                                                                                                                                                                                                                                             |

| COMP   | 18                                       | Output of error amplifier. An external resistor and capacitor network is typically connected from this pin to ground to provide loop compensation.                                                                                                                                                      |

| FB     | 19                                       | Feedback Input. FB senses the output voltage. Connect FB with a resistor divider connected between the output and ground. FB is a sensitive node. Keep FB away from noisy signal, such as SW and BST pin.                                                                                               |

| EXTVCC | 21                                       | External Power Input to an Internal LDO linear regulator Connected to VCC. This LDO supplies VCC power from EXTVCC, bypassing the external NDRV LDO whenever EXTVCC is higher than 10V. Do not exceed 30V on this pin. Do not connect EXTVCC to a voltage greater than VIN. Connect to GND if not used. |

| ISNS2  | 22                                       | Inductor current sense input 2.                                                                                                                                                                                                                                                                         |

| ISNS1  | 23                                       | Inductor current sense input 1.                                                                                                                                                                                                                                                                         |

| NDRV   | 25                                       | Drive Output for External Pass Device of the NDRV LDO Linear Regulator for VCC. Connect this pin to the gate of an external NMOS or NPN pass device.                                                                                                                                                    |

| VCC    | 26,27                                    | This pin provides power for the internal blocks of the IC. A minimum of 4.7uFcapacitor must be connected from this pin to ground.                                                                                                                                                                       |

| SW     | 31,32,33,34,35,                          | Switch Node. Connect this pin to the switching node of inductor.                                                                                                                                                                                                                                        |

|      | 42,50                                |                                                                                                                                                                                                 |

|------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BST  | 36                                   | This pin powers the high side driver and must be connected to a voltage higher than input voltage. A minimum of 0.1uF, high frequency capacitor must be connected from this pin to switch node. |

| PGND | 7,28,29,30,<br>37,38,39,<br>40,41,51 | Power Ground. This pin serves as a separate ground for the MOSFET driver and should be connected to the system's power ground plane.                                                            |

| NC   | 11,12,20,24                          | Not Connected.                                                                                                                                                                                  |

## **6 Device Marking Information**

| Part Number | Order Information | Package     | Package Qty | Top Marking    |

|-------------|-------------------|-------------|-------------|----------------|

| PL8905      | PL8905IQN48       | QFN6x6 - 48 | 2500        | 8905<br>RAAYMD |

PL8905: Part Number

RAABB: Lot Number. R: Year; AABB: Manufacturing Code

## **Specifications**

# 7.1 Absolute Maximum Ratings<sup>(Note1)</sup>

|                 | PARAMETER                                                                          | MIN  | MAX                   | Unit |

|-----------------|------------------------------------------------------------------------------------|------|-----------------------|------|

|                 | V <sub>IN</sub> to GND                                                             | -0.3 | 100                   |      |

|                 | V <sub>FB</sub> , V <sub>OVLO</sub> , V <sub>UVLO</sub> to GND                     | -0.3 | 6                     |      |

| Input Voltages  | V <sub>TOFF</sub> to GND                                                           | -0.3 | 12                    | V    |

| Input Voltages  | V <sub>ISNS1,2</sub> to GND                                                        | -0.3 | 65                    | V    |

|                 | V <sub>EN</sub> to GND                                                             | -0.3 | 100                   |      |

|                 | V <sub>EXTVCC</sub> to GND                                                         | -0.3 | 30                    |      |

|                 | V <sub>VDD</sub> to GND                                                            | -0.3 | 12                    |      |

| Output Voltages | V <sub>RON</sub> , V <sub>OCSET</sub> , V <sub>SS</sub> , V <sub>COMP</sub> to GND | -0.3 | 6                     | V    |

| Output Voltages | V <sub>BST</sub> to V <sub>SW</sub>                                                | -0.3 | 12                    | V    |

|                 | V <sub>SW</sub> to GND                                                             | -3   | V <sub>IN</sub> + 0.3 |      |

## 7.2 Handling Ratings

| PARAMETER        | DEFINITION                | MIN | MAX  | UNIT |

|------------------|---------------------------|-----|------|------|

| T <sub>ST</sub>  | Storage Temperature Range | -65 | 150  | °C   |

| TJ               | Junction Temperature      |     | +150 | °C   |

| T∟               | Lead Temperature          |     | +260 | °C   |

| V                | HBM Human body model      |     | 2    | kV   |

| V <sub>ESD</sub> | CDM Charger device model  |     | 500  | V    |

## 7.3 Recommended Operating Conditions (Note 2)

|                 | PARAMETER                                                                          | MIN  | MAX                  | Unit           |  |

|-----------------|------------------------------------------------------------------------------------|------|----------------------|----------------|--|

|                 | V <sub>IN</sub> to GND                                                             | 12   | 100                  |                |  |

|                 | V <sub>FB</sub> , V <sub>OVLO</sub> , V <sub>UVLO</sub> to GND                     | -0.3 | 5                    | ]              |  |

| Input Voltages  | V <sub>TOFF</sub> to GND                                                           | -0.3 | 10                   | V              |  |

| Input Voltages  | V <sub>ISNS1,2</sub> to GND                                                        | -0.3 | 60                   | V              |  |

|                 | V <sub>EN</sub> to GND                                                             | -0.3 | 100                  |                |  |

|                 | V <sub>EXTVCC</sub> to GND                                                         | -0.3 | 30                   | ]              |  |

|                 | V <sub>VDD</sub> to GND                                                            | -0.3 | 10                   |                |  |

| Output Valtages | V <sub>RON</sub> , V <sub>OCSET</sub> , V <sub>SS</sub> , V <sub>COMP</sub> to GND | -0.3 | 5                    | ] <sub>v</sub> |  |

| Output Voltages | V <sub>BST</sub> to V <sub>SW</sub>                                                | -0.3 | 10                   | ]              |  |

|                 | V <sub>SW</sub> to GND                                                             | -3   | V <sub>IN</sub> +0.3 |                |  |

| Temperature     | Operating junction temperature range, T <sub>J</sub>                               | -40  | +125                 | °C             |  |

## 7.4 Thermal Information(Note 4)

| Symbol          | Description                            | ETSSOP-20 | Unit |  |

|-----------------|----------------------------------------|-----------|------|--|

| $\theta_{JA}$   | Junction to ambient thermal resistance | 40        | °C/W |  |

| θ <sub>JC</sub> | Junction to case thermal resistance    | 23        | C/VV |  |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The device function is not guaranteed outside of the recommended operating conditions.3) Measured on approximately 1" square of 1 oz copper.

## **7.5 Electrical Characteristics**(Typical at Vin = 12V, T<sub>J</sub>=25°C, unless otherwise noted.)

| SYMBOL                | PARAMETER                                                                      | CONDITION                                                             | MIN  | TYP | MAX  | UNIT |

|-----------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|-----|------|------|

| VIN                   | Input Supply Operating Voltage Range                                           |                                                                       | 12   |     | 100  | V    |

| VOUT                  | Regulated Output Voltage Set Point                                             |                                                                       | 1.2  |     | 60   | V    |

| MOSFET                |                                                                                |                                                                       | 1    |     |      |      |

| R <sub>DS(ON)_H</sub> | High-Side Switch On-Resistance                                                 | $I_{OUT} = 1A$ , $V_{OUT} = 5V$                                       |      | 17  |      | mΩ   |

| R <sub>DS(ON)_L</sub> | Low-Side Switch On-Resistance                                                  | $I_{OUT} = 1A$ , $V_{OUT} = 5V$                                       |      | 17  |      | mΩ   |

| REFERENC              | CE VOLTAGE                                                                     |                                                                       | 1    |     |      |      |

| lα                    | Statics Current                                                                | Open Loop, VFB = 1.25V,<br>No Switching, VIN=48V ,<br>TJ=25℃          |      | 400 |      | uA   |

| I <sub>SHUTDOWN</sub> | EN Shutdown Supply Current                                                     | Close Loop, VEN=0V,<br>VIN=48V                                        |      | 20  | X    |      |

| REFERENC              | CE VOLTAGE                                                                     |                                                                       | -    |     |      |      |

|                       | Feedback Voltage                                                               |                                                                       |      | 1.2 |      | Ιv   |

| $V_{FB}$              |                                                                                |                                                                       | 1.5  | 1.2 | +1.5 | %    |

|                       | Accuracy                                                                       |                                                                       | -1.5 |     | +1.5 | 70   |

| SUPPLY V              | OLTAGE (Vcc)                                                                   | T 2                                                                   |      |     |      |      |

| $V_{DD}$              | V <sub>DD</sub> Regulator Output                                               | Supply by NDRV LDO                                                    | 9    | 9.5 | 10   |      |

|                       | LTAGE LOCKOUT                                                                  | Supply by EXTVCC LDO                                                  | 9.5  | 10  | 10.5 |      |

|                       | V <sub>DD</sub> Under Voltage Lockout                                          | X                                                                     |      |     |      | 1    |

| $V_{DD\_UVLO}$        | Voltage(V <sub>DD</sub> increasing)                                            | -40°C≤ T <sub>J</sub> ≤ 125°C                                         |      | 8   |      | V    |

| $V_{DD\_UVLOH}$       | V <sub>DD</sub> Under Voltage Hysteresis                                       |                                                                       |      | 670 |      | mV   |

| V <sub>BST_UVLO</sub> | V <sub>BST</sub> Under Voltage Lockout<br>Voltage(V <sub>BST</sub> increasing) | -40°C≤ T <sub>J</sub> ≤ 125°C                                         |      | 5.6 |      | V    |

| V <sub>BST_UVLO</sub> | V <sub>BST</sub> Under Voltage Hysteresis                                      | 70                                                                    |      | 860 |      | mV   |

| V <sub>IN_UVLO</sub>  | VIN Under Voltage Lockout<br>Voltage(V <sub>IN</sub> increasing)               |                                                                       |      | 6.5 |      | V    |

| V <sub>IN_UVLOH</sub> | VIN Under Voltage Hysteresis                                                   |                                                                       |      | 650 |      | mV   |

| V <sub>EN_UVLO</sub>  | EN Under Voltage Lockout Voltage(V <sub>EN</sub> increasing)                   |                                                                       |      | 1.2 |      | V    |

| V <sub>EN_UVLOH</sub> | EN Under Voltage Hysteresis                                                    |                                                                       |      | 200 |      | mV   |

|                       | TAGE LOCKOUT                                                                   |                                                                       |      | 200 |      | 1111 |

| REF <sub>IN_OVP</sub> | Reference of VIN Over Voltage Lockout Voltage(V <sub>IN</sub> increasing)      |                                                                       |      | 1.2 |      | V    |

| HYS <sub>IN_OV</sub>  | Reference Hysteresis of VIN Over                                               |                                                                       |      | 200 |      | mV   |

| CONTROL               | Voltage Lockout Voltage                                                        |                                                                       |      |     |      |      |

| I(Source/<br>Sink)    | Source/Sink Current                                                            |                                                                       |      | 300 |      | uA   |

| gm                    | Trans-conductance                                                              |                                                                       |      | 3   |      | mS   |

| SOFT-STA              |                                                                                | 1                                                                     |      |     |      |      |

| I <sub>SS</sub>       | Soft-Start Current                                                             | SS = 0 V                                                              | 15   | 20  | 25   | uA   |

| VSNS LIMI             | T                                                                              | -                                                                     | -    |     |      | -    |

| Vocset                | OCSET voltage                                                                  | -40°C≤ T <sub>J</sub> ≤ 125°C                                         |      | 1.2 |      | V    |

| VLIMH                 | On Duty ISNS1-ISNS2 Limit                                                      | R <sub>OCSET</sub> = 25k Ohm,<br>VLIMH=1.2/R <sub>OCSET</sub> *25K/10 |      | 120 |      | mV   |

| VLIML                 | Off Duty ISNS1-ISNS2 Limit                                                     | R <sub>OCSET</sub> = 25k Ohm,<br>VLIML=1.2/R <sub>OCSET</sub> *20K/10 |      | 96  |      | mV   |

| T <sub>OVERLOAD</sub> | Over Load Protection Blank Time                                                | V LIIVIL - 1.2/NOCSET ZURV IU                                         |      | 200 |      | ms   |

| Frequency             |                                                                                |                                                                       |      |     |      |      |

| F <sub>SW</sub>       | Switching Frequency                                                            | Fsw=Vout/(Rh*500p)<br>Or Fsw=1/(RL*50p)                               | 50   | 200 | 500  | kHz  |

| TON <sub>MIN</sub>  | Minimum On Time                      |              | 140 | ns |

|---------------------|--------------------------------------|--------------|-----|----|

| TOFF <sub>MIN</sub> | Minimum Off Time                     |              | 400 | ns |

| Toff Timer          |                                      |              |     |    |

|                     | Toff Time Delay                      | Toff = GND   | 0   | S  |

| T <sub>OFF</sub>    |                                      | Toff = Float | 10  | S  |

|                     |                                      | Toff = VCC   | 20  | S  |

| OUTPUT D            | RIVERS                               |              |     |    |

| Tdelay1             | Top Gate Off to Bottom Gate On Delay |              | 70  | ns |

| Tdelay2             | Bottom Gate Off to Top Gate On Delay |              | 70  | ns |

## Note:

<sup>4)</sup> Guaranteed by design, not tested in production.

## **8 Detailed Description**

#### 8.1 Overview

PL8905 is a high voltage Buck Control designed for high performance synchronous Buck DC/DC applications with input voltages up to 100V.

PL8905 integrates a high efficiency synchronous step-down switching regulator, which includes a 120V,  $17m\Omega$  high side and a 120V,  $17m\Omega$  low side MOSFETs to provide 5A continuous load current over12V to 100V wide operating input voltage.

The PL8905 adopts adaptive constant on time peak current mode control at the moderate to heavy load currents and operates in the PFM mode at the light load current. With this control scheme, the PL8905 provides the excellent line and load transient response with the minimal output capacitor. The external loop compensation brings the flexibility to use a wider range of the inductor and output capacitor combinations.

The PL8905 supports the adjustable switching frequency up to 500kHz. This device implements user programmable cycle-by-cycle current limit with 200ms over load timer to protect the device from thermal run away. If the overload condition is triggered, this part will stop switching until EN is toggled. This device also implements user programmable over voltage lockout protection and over temperature protection to ensure reliably operation.

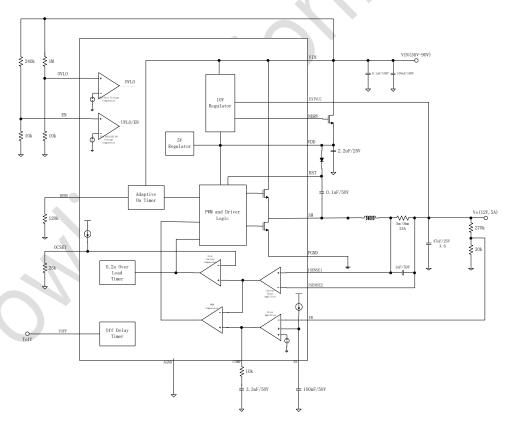

## 8.2 Functional Block Diagram

Fig. 3 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Enable and OVLO

When the EN pin is pulled high above 1.2V, this part is enabled. When the EN pin is pulled below 1.0V, this part goes into the shutdown mode and stops operation.

When the OVLO pin is pulled high above 1.2V, the PL8905 is disabled and it will not resume switching even if OVLO falls below 1.0V unless EN is toggled.

#### 8.3.2 Under-voltage Lockout

This controller stops switching when the input voltage drops below 5.85V or VDD is below 7.33V. It resumes operation when input voltage is larger than 6.5V and VDD is larger than 8V.

#### 8.3.3 Cycle-by-Cycle Current Limit and Over Load Protection

The PL8905 provides cycle-by-cycle current limit to protect power MOSFET during on duty and also off duty. It will immediately turn off high side MOSFET once on duty current limit is triggered or prolongs the off duty until the inductor current is lower than off duty current limit. Hiccup protection will be triggered if the over current condition endures more than 200ms. And the switching will be resumed after 16 soft start procedures.

#### 8.3.4 Programmable Switching Frequency

This controller features a programmable switching frequency ranging from 50kHz to 500kHz.

The frequency setting by RON is calculated as below:

$$F_{SW} = \frac{V_{OUT}}{R_{ON}(k\Omega) \times 0.5} (MHz)$$

(1)

#### 8.3.5 Error Amplifier

The PL8905 has a trans-conductance amplifier and compares the feedback voltage with the internal voltage reference (or the internal soft start voltage during startup phase). The trans-conductance of the error amplifier is 3 mA / V typically. The loop compensation components are required to be placed between the COMP terminal and ground to balance the loop stability and the transient response time.

#### 8.3.6 VCC Regulators

The PL8905 contains two VDD regulators that provide power supply for low side gate driver and boot-strap high side gate drive. One is the NDRV regulator which regulates VDD to 9.5V. The other one is the 10V low dropout LDO powered by EXTVCC which is current limited to 60mA. The VDD load current should be evaluated if NDRV regulator is not used.

#### 8.3.7 Bootstrap Voltage (BST)

The PL8905 has an integrated bootstrap regulator, and requires a small ceramic capacitor between the BST pin and SW pin to provide the gate drive voltage for the high-side FET. The bootstrap capacitor is charged when the BST-SW voltage is below regulation. The value of this ceramic capacitor should be above 100 nF. A ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating of 25 V or higher is recommended because of the stable characteristics over temperature and DC biased voltage.

#### 8.3.8 Thermal Shutdown

A thermal shutdown is implemented to prevent the damage due to the excessive heat and power dissipation. Typically, the thermal shutdown occurs at the junction temperature exceeding 150°C. When the thermal shutdown is triggered, the device stops switching and recover when the junction temperature falls below 130°C.

## 9 Application and Implementation

#### 9.1 Setting the switching Frequency

The switching frequency of the PL8905 can be programmed as equation 1. For a target switching frequency of 200 kHz, The calculated value is 120 k $\Omega$ .

#### 9.2 Setting the Output Current Limit

The cycle-by-cycle current limit of the PL8905 is configured by combination of Rocset between OCSET and AGND and sense resistor Rsns in serial with inductor. The cycle-by-cycle current limit is determined as follows:

$$I_{LIML} = \frac{2.4}{R_{OCSET} (k\Omega) \times R_{SNS} (\Omega)} (A)$$

(2)

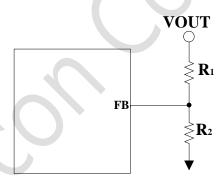

#### 9.3 Setting the Output Voltage

Choose R1 and R2 to program the proper output voltage. To minimize the power consumption under light load, it is desirable to choose large resistance values for both R1 and R2. A value between 10k and 1M is recommended for both resistors. If R1=200k is chosen, then R2 can be calculated to be:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right) \tag{3}$$

Fig. 4

#### 9.4 Selecting the Inductor

1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the maximum average input current. The inductance is calculated as:

$$L = \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \frac{V_{\text{IN}} - V_{\text{OUT}}}{0.4 \times F_{\text{SW}} \times I_{\text{OUT}\_\text{MAX}}}$$

(4)

where  $F_{SW}$  is the switching frequency and  $I_{OUT\_MAX}$  is the maximum load current.

PL8905 is less sensitive to the ripple current variations. Consequently, the final choice of inductance can be slightly off the calculation value without significantly impacting the performance.

2) The saturation current rating of an inductor must be selected to guarantee an adequate margin to the peak inductor

current under full load conditions.

3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<10mohm to achieve a good over -all efficiency.

#### 9.5 Selecting the Output Capacitors

The Output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken in to account when selecting these capacitors. For the best performance, it is recommended to use X5R or better grade ceramic capacitor.

#### 9.6 Selecting the Input Capacitors

Multilayer ceramic capacitors are an excellent choice for the input decoupling of the step-down converter as they have extremely low ESR and are available in small footprints. Input capacitors should be located as close as possible to the device. While a 10-µF input capacitor is sufficient for the most applications, larger values may be used to reduce input current ripple.

Take care when using only ceramic input capacitors. When a ceramic capacitor is used at the input and the power is being supplied through long wires, such as from a wall adapter, a load step at the output can induce ringing at the VIN pin. This ringing can couple to the output and be mistaken as loop instability or could even damage the part. Additional "bulk" capacitance (electrolytic or tantalum) in this circumstance, should be placed between CIN and the power source lead to reduce ringing that can occur between the inductance of the power source leads and CIN.

#### 9.7 Selecting the Bootstrap Capacitor

The bootstrap capacitor between the BST and SW pin supplies the gate current to charge the high-side FET device gate during each cycle's turn-on and also supplies charge for the bootstrap capacitor. The recommended value of the bootstrap capacitor is  $0.1\mu\text{F}$  to  $1\mu\text{F}$ . CBST should be a good quality, low ESR, ceramic capacitor located at the pins of the device to minimize potentially damaging voltage transients caused by trace inductance. A value of  $0.1\mu\text{F}$  was selected for this design example.

### 9.8 Selecting the VCC Capacitors

The primary purpose of the VCC capacitor is to supply the peak transient currents of the driver and bootstrap capacitor as well as provide stability for the VCC regulator. The value of CVCC should be at least 10 times greater than the value of CBST, and should be a good quality, low ESR, ceramic capacitor. CVCC should be placed close to the pins of the IC to minimize potentially damaging voltage transients caused by the trace inductance. A value of 4.7µF was selected for this design example.

## 9.9 Design Example

The Figure 5 is the typical application schematic for 36 to 90-V input to output 12-Voutput converter.

Figure 5. Application Schematic

## 10 Packaging Informatio

|                     |          | SYMBOL | MIN      | NOM       | MAX   |

|---------------------|----------|--------|----------|-----------|-------|

| TOTAL THICKNESS     |          | A      | 0.7      | 0.75      | 0.8   |

| STAND OFF           |          | A1     | 0        | 0.02      | 0.05  |

| MOLD THICKNESS      |          | A2     |          | 0.55      |       |

| L/F THICKNESS       |          | A3     |          | 0.203 REF |       |

| LEAD WIDTH          |          | ь      | 0.15     | 0.2       | 0.25  |

| BODY SIZE           | X        | D      |          | 6 BSC     |       |

| BODT SIZE           | Y        | E      |          | 6 BSC     |       |

| LEAD PITCH          |          | e      |          | 0.4 BSC   |       |

|                     | X        | D2     | 4.5      | 4.6       | 4.7   |

| EP SIZE             | l ^ [    | D3     | 1.975    | 2.075     | 2.175 |

|                     | Y        | E2     | 1.975    | 2.075     | 2.175 |

| LEAD LENGTH         |          | L      | 0.3      | 0.4       | 0.5   |

| LEAD TIP TO EXPOSED | PAD EDGE | K      | 0.3 REF  |           |       |

| PAD TO PAD          |          | K1     | 0.45 REF |           |       |

| PACKAGE EDGE TOLERA | NCE      | aaa    | 0.1      |           |       |

| MOLD FLATNESS       |          | ccc    | 0.1      |           |       |

| COPLANARITY         |          | eee    | 0.08     |           |       |

| LEAD OFFSET         |          | bbb    | 0.07     |           |       |

| EXPOSED PAD OFFSET  |          | fff    | 0.1      |           |       |

|                     |          |        |          |           |       |

|                     |          |        |          |           |       |

|                     |          |        |          |           |       |

|                     |          | 1      |          |           |       |

#### **IMPORTANT NOTICE**

Powlicon Inc. assumes no responsibility for any errors which may appear in this document. Powlicon Inc. reserves the right to change devices or specifications detailed herein at any time without notice. Powlicon Inc. does not assume any liability arising out of the application or use of any product described herein; neither it does it convey any license under its patent rights, nor the rights of others. Powlicon Inc. products are not authorized for use as critical components in life support devices or systems without written approval letter from the Chief Executive Officer of Powlicon Inc.. The use of products in such applications shall assume all risks of such use and will agree to not hold against Powlicon Inc. for all damages.