## **High Efficiency 4-Switch Buck-Boost Controller**

#### 1 Features

- Buck-Boost Controller for Step-Up/Step-Down DC/DC Conversion

- Dynamical programming of Output current and Output voltage using PWM signal or analog signal

- 2V to 32 V wide output range

- Comprehensive protection features including Output Short Protection (OSP), Cycle-by-Cycle input and output Peak Current Limit, thermal regulation, thermal shutdown, input UVLO, input OVP, output OVP etc.

- Adjustable Switching Frequency using resistor

- Frequency dithering for good EMI performance

- Integrated 2-A MOSFET Gate Drivers

- Input or Output Average Current Limiting with stable CC loop

- 5V/55mA low I<sub>g</sub> LDO to power system MCU

- Available in QFN4x4-32 Package

### 2 Applications

- Automotive Start-Stop Systems

- Industrial PC Power Supplies

- USB Power Delivery

- Car charger

- HUB Power

### 3 Description

PL5501 is a synchronous 4-switch Buck-Boost controller capable of regulating the output voltage at above or below the input voltage. PL5501 operates over a wide input voltage range of 3.6 V to 32 V (36 V maximum) to support a variety of applications.

PL5501 employs Constant ON time control in buck, boost and buck-boost operation modes for superior load and line regulation. The switching frequency could be set to 150kHz, 300kHz, 600kHz or 1200kHz based on different resistor value between FREQ pin and GND pin. The device also features a programmable soft-start function and offers all kinds of protection features including cycle-by-cycle current limiting, input under voltage lockout (UVLO), output over voltage protection (OVP), input Over Voltage Protection, thermal shutdown and output short protection etc.

VADJ, IADJ pins are used to program output VBUS voltage and output current limit, provides voltage control loop, constant current loop, thermal regulation loop, temperature sensing, which makes PL5501 an excellent option for USB Power Delivery (PD) application.

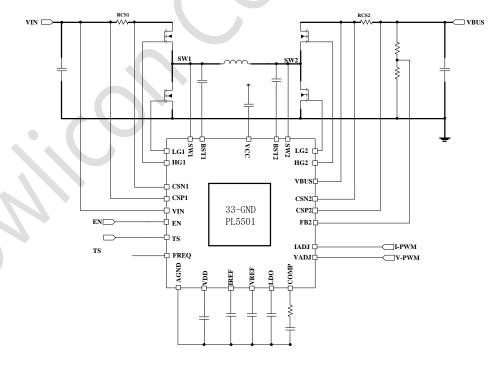

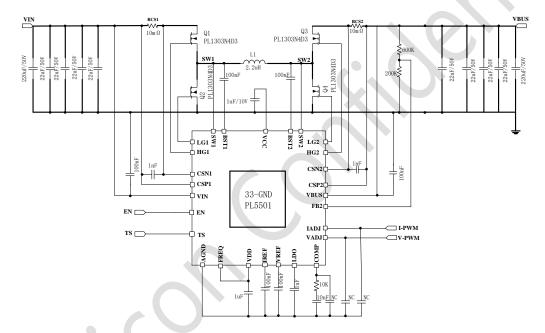

## **4 Typical Application Schematic**

Fig. 1 Application Schematic

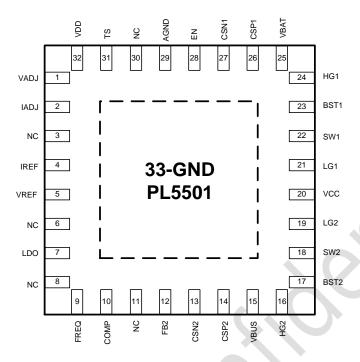

## **5 Pin Configuration and Functions**

Fig. 2 Pin-Function (QFN4X4-32)

| Pin             |      | Description                                                                                                                                                                                                                                             |  |  |  |  |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Number          | Name | Description                                                                                                                                                                                                                                             |  |  |  |  |

| 1               | VADJ | Connect a 0-2V analog voltage or a PWM signal to program voltage reference on VREF pin. Connect this pin to VDD will force VREF to constant 2V.                                                                                                         |  |  |  |  |

| 2               | IADJ | Connect a 0-2V analog voltage or a PWM signal to program voltage reference on IREF pin. Connect this pin to VDD will force IREF to 2V.                                                                                                                  |  |  |  |  |

| 3,6,8,11,<br>30 | NC   |                                                                                                                                                                                                                                                         |  |  |  |  |

| 4               | IREF | Reference voltage for input and output current limiting loop.                                                                                                                                                                                           |  |  |  |  |

| 5               | VREF | Voltage reference for voltage control loop                                                                                                                                                                                                              |  |  |  |  |

| 7               | LDO  | Low quiescent current 5V/55mA LDO. Directly powered from VIN pin. LDO can be used as power supply for application processor such as MCU. When EN is low, only this LDO will be active to power MCU and keep low quiescent current for the whole system. |  |  |  |  |

| 9               | FREQ | Connect to GND to set the switching frequency at 150kHz. Connect this pin to VDD to set switching frequency at 300kHz. Connect to a resistor divider between VDD and GND to set frequency to 600k and 1200k Hz.                                         |  |  |  |  |

| 10              | COMP | Error Amplifier output.                                                                                                                                                                                                                                 |  |  |  |  |

| 12              | FB2  | VBUS voltage feedback. Connect a resistor divider between VBUS and GND to FB2 to program VBUS voltage.                                                                                                                                                  |  |  |  |  |

| 13              | CSN2 | The minus input of output current sense.                                                                                                                                                                                                                |  |  |  |  |

| 14              | CSP2 | The positive input of output current sense.                                                                                                                                                                                                             |  |  |  |  |

| 15              | VBUS | Connect this pin to the output voltage.                                                                                                                                                                                                                 |  |  |  |  |

| 16              | HG2  | High side MOSFET driver 2.                                                                                                                                                                                                                              |  |  |  |  |

| 17              | BST2 | Boost pin for high side MOSFET driver 2.                                                                                                                                                                                                                |  |  |  |  |

| 18              | SW2  | Connect this pin to the Switching point 2 of the power stage.                                                                                                                                                                                           |  |  |  |  |

| 19              | LG2  | Low side MOSFET driver output 2.                                                                                                                                                                                                                        |  |  |  |  |

| 20              | VCC  | 6.6V power supply for high side and low side driver                                                                                                                                                                                                     |  |  |  |  |

| 21              | LG1  | Low side MOSFET driver output1.                                                                                                                                                                                                                         |  |  |  |  |

| 22              | SW1  | Connect this pin to the Switching point1 of the power stage.                                                                                                                                                                                            |  |  |  |  |

| 23              | BST1 | Boost pin for high side MOSFET driver1.                                                                                                                                                                                                                 |  |  |  |  |

| 24              | HG1  | High side MOSFET driver1.                                                                                                                                                                                                                               |  |  |  |  |

| 25              | VIN  | Connect this pin to the Input voltage.                                                                                                                                                                                                                  |  |  |  |  |

| 26              | CSP1 | The positive input of input current sense.                                                                                                                                                                                                              |  |  |  |  |

| 27 | CSN1 | The minus input of input current sense.                                                                                                                                                                  |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 | EN   | Logic High will enable the converter. Logic Low will disable the whole PL5501 except LDO. Only LDO is working to power system MCU when EN is low. EN is pulled high internally by a high value resistor. |

| 29 | AGND | Signal Ground.                                                                                                                                                                                           |

| 31 | TS   | temperature sense                                                                                                                                                                                        |

| 32 | VDD  | 5.4V power supply for PL5501 control core.                                                                                                                                                               |

## **6 Device Marking Information**

| Part Number | Order Information | Package     | Package Qty | Top Marking    |

|-------------|-------------------|-------------|-------------|----------------|

| PL5501      | PL5501IQN32       | QFN4x4 - 32 | 4000        | 5501<br>RAAYMD |

PL5501: Part Number

RAAYMD: RAA: LOT NO.; YMD: Package Date

## 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(Note1)</sup>

| PARAMETER                                   | MIN  | MAX | Unit |

|---------------------------------------------|------|-----|------|

| VIN, VBUS, CSN1, CSN2, CSP1, CSP2, SW1, SW2 | -0.3 | 40  |      |

| HG1, BST1 to SW1                            | -0.3 | 7   |      |

| HG2, BST2 to SW2                            | -0.3 | 7   |      |

| LG1, LG2, VCC to GND                        | -0.3 | 7   |      |

| CSP1 to CSN1                                | -0.3 | 0.6 | V    |

| CSP2 to CSN2                                | -0.3 | 0.6 |      |

| VIN to CSP1, CSN1                           | -0.3 | 0.6 |      |

| VBUS to CSP2, CSN2                          | -0.3 | 0.6 |      |

| Other Pins to GND                           | -0.3 | 6   |      |

## 7.2 Handling Ratings

| PARAMETER        | DEFINITION                | MIN | MAX  | UNIT |

|------------------|---------------------------|-----|------|------|

| T <sub>ST</sub>  | Storage Temperature Range | -65 | 150  | °C   |

| TJ               | Junction Temperature      | X   | +150 | °C   |

| TL               | Lead Temperature          |     | +260 | °C   |

| V <sub>ESD</sub> | HBM Human body model      |     | 2    | kV   |

## 7.3 Recommended Operating Conditions (Note 2)

|                | PARAMETER                                            | MIN | MAX  | Unit |

|----------------|------------------------------------------------------|-----|------|------|

| Input Voltages | VIN                                                  | 3.6 | 32   | V    |

| Temperature    | Operating junction temperature range, T <sub>J</sub> | -40 | +125 | °C   |

## 7.4 Thermal Information<sup>(Note 3)</sup>

| Symbol          | Description                            | QFN4X4-32 | Unit |

|-----------------|----------------------------------------|-----------|------|

| $\theta_{JA}$   | Junction to ambient thermal resistance | 44        | °C   |

| θ <sub>JC</sub> | Junction to case thermal resistance    | 9         | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The device function is not guaranteed outside of the recommended operating conditions.

- 3) Measured on approximately 1" square of 1 oz copper.

## **7.5 Electrical Characteristics** (Typical at VIN = 12V, $T_J = 25$ °C, unless otherwise noted.)

| Supply voltages               | PARAMETER                                      | CONDITION                        | MIN    | TYP      | MAX  | UNIT     |

|-------------------------------|------------------------------------------------|----------------------------------|--------|----------|------|----------|

| VIN                           | Input voltage                                  |                                  | 3.6    |          | 32   | V        |

| 1 \/INI                       | VIN Shutdown Current                           | EN=0V, VIN=7.2V                  |        | 15       |      | uA       |

| $I_{Q_{-}}VIN$                | VIN Supply Current                             | No Switching, FB=2.1V            |        | 1000     |      | uA       |

| VBUS                          | Bus line voltage                               |                                  | 3.6    |          | 32   | V        |

| I <sub>Q</sub> _VBUS          | VBUS Shutdown Current                          | EN=0V, VBUS=7.2V                 |        | 15       |      | uA       |

|                               | VBUS Supply Current                            | No Switching                     |        | 1200     |      | uA       |

| V <sub>VCC</sub>              | Driver power supply voltage                    | VIN =15V                         |        | 6.6      |      | V        |

| $V_{VDD}$                     | Control core power supply voltage              | VIN =15V                         |        | 5.4      |      | V        |

| $V_{LDO}$                     | LDO output voltage                             | VIN =15V                         |        | 5        |      | V        |

| I <sub>LDO</sub>              | LDO output current                             | V <sub>LDO</sub> =5V             |        |          | 55   | mA       |

| UVLO/EN                       | 1                                              |                                  |        |          |      |          |

| VIN UV                        | VIN UVLO Rising                                |                                  |        | 3.5      |      | V        |

| - · · ·                       | UVLO Hysteresis                                |                                  |        | 300      |      | mV       |

| VBUS_uv                       | VIN UVLO Rising                                |                                  |        | 3.5      |      | V        |

| 0,                            | UVLO Hysteresis                                |                                  |        | 300      | 1.0  | mV       |

| $V_{EN\_UV}$                  | Operation Threshold                            |                                  | 1.1    | 1.2      | 1.3  | V        |

|                               | Hysteresis                                     |                                  |        | 200      |      | mV       |

| Control loop                  | LVEDO                                          | FD0lt.s.r.s                      | 1 4 00 |          | 0.04 | \ /      |

| V <sub>FB2</sub>              | VFB2 regulation voltage                        | FB2 voltage                      | 1.96   | 2        | 2.04 | VC       |

| G <sub>mEA</sub>              | Error amplifier gm                             | \/FD_\/DEE:400;;\/               | V .    | 450      |      | uS       |

| Isink                         | COMP source current                            | VFB=VREF+100mV<br>VFB=VREF-100mV |        | 15<br>20 |      | uA<br>   |

| ISOURCE                       | COMP source current                            | FB2 in regulation                |        | 20       | 100  | uA<br>nA |

| I <sub>FB2</sub>              | FB2 bias current                               | FB2 in regulation                |        |          | 100  | ΠA       |

| Frequency                     |                                                |                                  |        |          |      |          |

|                               | Switching Frequency                            | FREQ 0-0.4V, short FREQ          |        | 150      |      | KHz      |

|                               |                                                | pin to GND.                      | 150    |          |      | 13112    |

| F <sub>SW</sub>               |                                                | FREQ 1.8-5.4V, short             |        | 300      |      | KHz      |

| 1 200                         | - Cwitching Frequency                          | FREQ pin to VDD.                 |        |          |      |          |

|                               |                                                | FREQ 0.4-0.85V                   |        | 600      |      | KHZ      |

|                               |                                                | FREQ 0.85-1.8V                   |        | 1200     |      | KHZ      |

| Current Limit                 |                                                | T =                              | 1      |          | 1    |          |

| I <sub>CCLIM_VIN</sub>        | VIN average current Limit, V <sub>CSP1</sub> - | Boost mode                       |        | 80       |      | mV       |

| -OOLIM_VIIV                   | V <sub>CSN1</sub>                              | Buck mode                        |        | 40       |      | mV       |

| ICCLIM BUS                    | Bus average current Limit,                     |                                  |        | 40       |      | mV       |

|                               | V <sub>CSP2</sub> - V <sub>CSN2</sub>          |                                  |        |          |      |          |

| NMOS Driver                   |                                                |                                  |        |          |      |          |

| (Note 4)                      | Driver peak source current                     | VBST-VSW=6.6V                    |        | 2        |      | Α        |

| I <sub>HDRV1,2</sub> (Note 4) | Driver peak sink current                       | VBST-VSW=6.6V                    |        | 2        |      | Α        |

|                               |                                                |                                  |        |          |      |          |

| I <sub>LDRV1,2</sub> (Note 4) | Driver peak source current                     | VCC=6.6V                         |        | 2        |      | Α        |

| -LDRV1,2                      | Driver peak sink current                       | VCC=6.6V                         |        | 2        |      | Α        |

| V <sub>BSTUV</sub>            | UVLO                                           |                                  |        | 2        |      | V        |

| V B510V                       | UVLO Hysteresis                                |                                  |        | 300      |      | mV       |

| <b>Output Protection</b>      | ı                                              |                                  |        |          |      |          |

| V <sub>OVP</sub>              | Output over voltage threshold                  |                                  |        | 110      |      | %        |

| $V_{UVP}$                     | Output under voltage threshold                 |                                  |        | 50       |      | %        |

| VADJ, IADJ                    |                                                |                                  |        |          |      |          |

| *                             | VPWM low voltage                               | I                                | I      |          | 0.4  | V        |

| V <sub>TH_VADJ</sub> (Note 4) | VPWM high voltage                              |                                  | 2.5    |          | 0.4  | V        |

|                               | IPWM low voltage                               |                                  | 2.0    |          | 0.4  | V        |

| V <sub>TH_IADJ</sub> (Note 4) |                                                |                                  | 2.5    |          | 0.4  | V        |

| T <sub>SD</sub> (Note 4)      | ·                                              |                                  | 2.5    | 150      |      |          |

| (Note 4)                      | Thermal Shutdown Threshold                     |                                  | -      | 150      |      |          |

| T <sub>HYS</sub> (Note 4)     | Thermal Shutdown Hysteresis                    |                                  |        | 20       |      | °C       |

### Notes:

4) Guaranteed by design

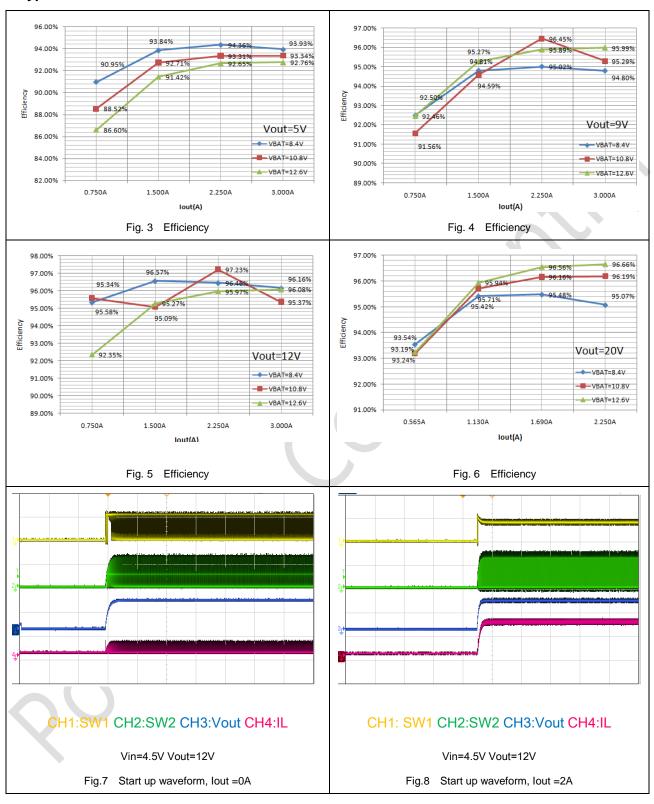

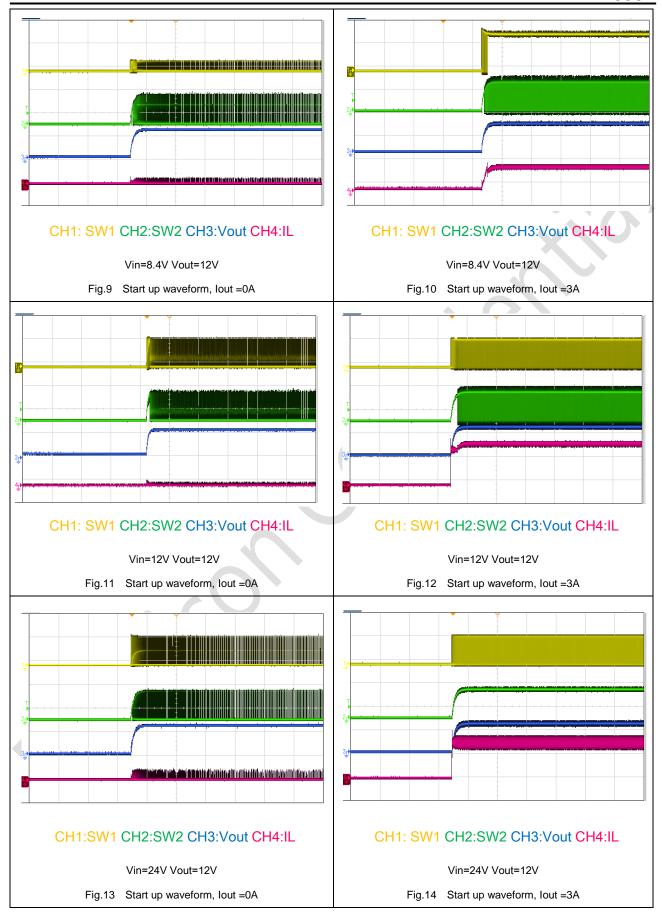

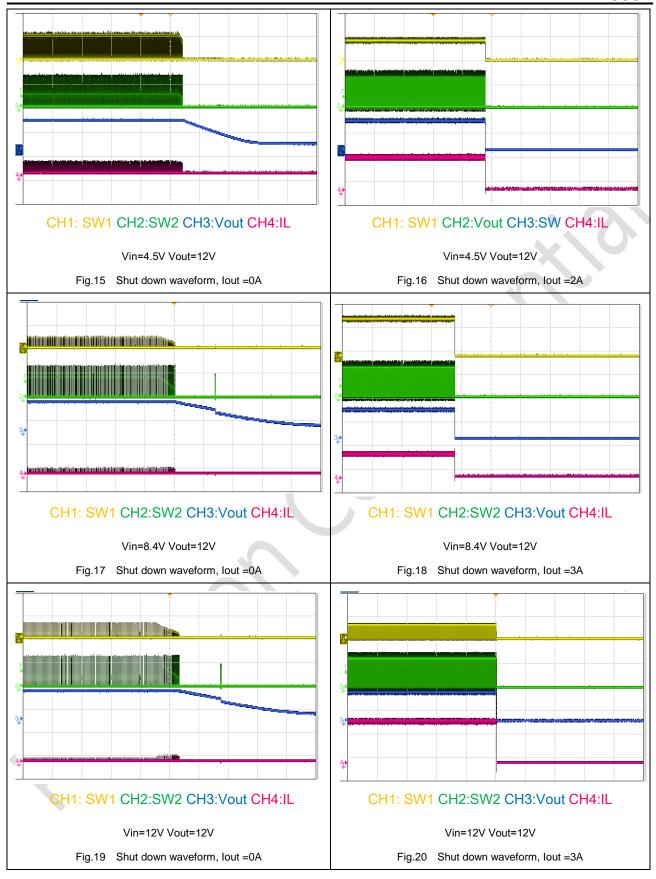

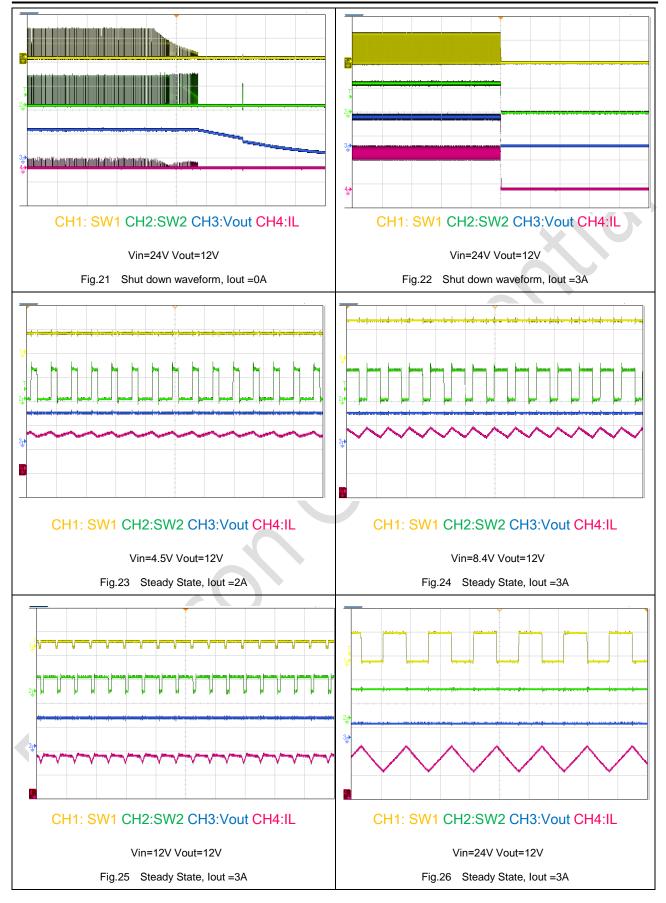

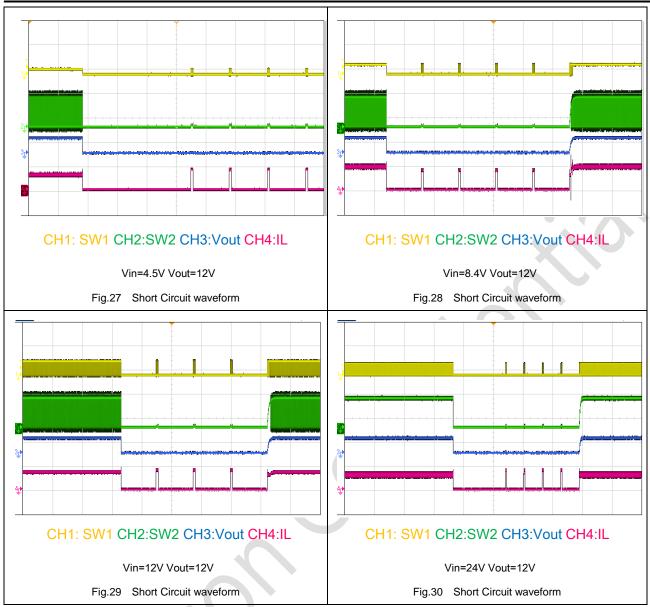

## **8 Typical Characteristics**

### 9 Detailed Descriptions

#### 9.1 Overview

PL5501 is a synchronous 4-switch Buck-Boost controller capable of regulating the output voltage at, above, or below the input voltage. PL5501 operates over a wide input voltage range of 3.6 V to 32 V (36 V maximum) to support a variety of applications. It operates in buck mode when  $V_{IN}$  is greater than  $V_{OUT}$  and in the boost mode when  $V_{IN}$  is less than  $V_{OUT}$ . When  $V_{IN}$  is close to  $V_{OUT}$ , the device operates in a proprietary buck-boost mode. The control scheme provides smooth operation for any input/output combination within the specified operating range.

#### 9.2 Enable/UVLO

When EN is greater than 1.2V operating threshold, the control loop starts to work and regulate output to target voltage. When EN pin is below the standby threshold (1.1V typical), PL5501 stops working with only LDO is active to power MCU. EN is pulled high to 4V internally using a 2Meg resistor.

#### 9.3 Over current Protection and short circuit protection

PL5501 provides cycle-by-cycle current limit to protect against over current and short circuit conditions. When VOUT is drop to UV threshold, PL5501 will go into hiccup mode to lower down power consumption.

#### 9.4 Average Input/Output Current Limiting

PL5501 provides optional average current limiting capability to limit either the input or the output current. The average current limiting circuit uses an additional current sense resistor connected in series with the input supply or output voltage of the converter. A current sense gm amplifier with inputs at the CSP1 and CSN1 pins monitors the voltage across the sensing resistor and compares it with an internal 40 mV reference. If the drop across the sense resistor is greater than 40 mV, the gm amplifier regulates COMP voltage to lower down input or output current. The target constant current is given by Equation 1:

$$I_{CL(AVG)} = \frac{40 \, mV}{R_{SNS}} \tag{1}$$

The average current loop can be disabled by shorting CSP1 to CSN1 or CSP2 to CSN2.

#### 9.5 Frequency Setting (FREQ) and frequency dithering

PL5501 switching frequency can be programmed at 150 kHz, 300 kHz or 600 kHz and 1200 kHz by voltage at FREQ pin to GND. When FREQ is connected to AGND, the switching frequency is set at 150 kHz. When FREQ is connected to VDD, the switching frequency is set at 300 kHz. A voltage divider between VDD and GND pin can be used to program switching frequency if 600 kHz or 1200 kHz is required.

#### 9.6 Integrated Gate Drivers

PL5501 provides four N-channel MOSFET gate drivers: two floating high-side gate drivers at the HG1 and HG2 pins, and two ground referenced low-side drivers at the LG1 and LG2 pins. Each driver is capable of sourcing 2 A and sinking 2 A peak current. In buck operation, LG1 and HG1 are switched by the PWM controller while HG2 remains continuously on. In boost operation, LG2 and HG2 are switched while HG1 remains continuously on. In DCM buck operation, LG1 and HG2 are turned off when the inductor current drops to zero (diode emulation).

The gate drive output HG2 remains off before the first high side switch is turned on to prevent reverse current flow from a pre-biased output..

#### 9.7 Thermal Shutdown

PL5501 is protected by a thermal shutdown circuit that shuts down the device when the internal junction temperature exceeds 160°C (typical). The soft-start capacitor is discharged when thermal shutdown is triggered and the gate drivers are disabled. The converter automatically restarts when the junction temperature drops by the thermal shutdown hysteresis of 15°C below the thermal shutdown threshold.

#### 9.8 VREF and IREF

VREF pin is the final reference voltage used in the voltage regulation loop. When VADJ is connected to VDD, When VADJ is connected to a PWM signal, PWM signal will first be chopped to 2V and filter out using an internal resistor and external capacitor on VREF pin. The capacitor on VREF pin is also acting as soft-start capacitor at power up or in output voltage transition period. It is recommend using a relatively large capacitor such as 470nF for VREF pin and IREF pin.

The same mechanism works for IADJ and IREF pin.

9.9 TS:

PL5501 is provides external over temperature protection function. PL5501 works normally when TS pin voltage is between 2.6V-3.8V,When TS pin is below the 2.6V, PL5501 stops working.

### 10 Applications and Implementation

The typical application on the first page is a basic PL5501 application circuit. External component selection is driven by the load requirement, and begins with the selection of RS1, RS2 and the inductor value. Next, the power MOSFETs need to be selected. Finally, C<sub>IN</sub> and C<sub>OUT</sub> are selected. This circuit can be configured for operation up to an input voltage of 32V.

#### 10.1 R<sub>cs</sub> Selection

As shown in Figures 32, input/output current sense resistor RCS1/RCS2 should be placed between the bulk capacitor for VIN/VBUS and the decoupling capacitor. A low pass filter formed by RF and CF is recommended to reduce the switching noise and stabilize the current loop. If input/output current limit is not desired, then CSP1/CSN1 and CSP2/CSN2 pins should be shorted to either VIN or VBUS. Place CSP1/CSN1, CSP2/CSN2 symmetrically and keep them away switching signals such as BST1, BST2, SW1, SW2, VIN, VBUS etc.

#### 10.2 Inductor Selection

The operating frequency and inductor selection are interrelated in that higher operating frequencies allow the use of smaller inductor and capacitor values. The inductor value has a direct effect on ripple current. The inductor current ripple  $\Delta I_L$  is typically set to 20% to 40% of the maximum inductor current in the boost region at  $V_{IN(MIN)}$ .

For a given ripple, the inductance terms in continuous mode are as follows:

$$L_{\text{BOOST}} > \frac{V_{\text{IN(MIN)}}^2 (V_{\text{OUT}} - V_{\text{IN(MIN)}})^* 1000}{f^* \Delta l_1 * V_{\text{OUT}}^2} \text{uH}$$

(3)

$$L_{\text{BUCK}} > \frac{V_{\text{OUT}}^*(V_{\text{IN}(\text{MAX})} - V_{\text{OUT}})^* 1000}{f^* \Delta I_L^* V_{\text{IN}(\text{MAX})}} \text{ uH}$$

(4)

where: f is operating frequency, kHz

V<sub>IN(MIN)</sub> is minimum input voltage, V

V<sub>IN(MAX)</sub> is maximum input voltage, V

V<sub>OUT</sub> is output voltage, V

∆I<sub>L</sub> is maximum inductor ripple current, A, usually select 20~40% maximum output current.

For high efficiency, choose an inductor with low core loss, such as ferrite. Also, the inductor should have low DC resistance to reduce the I2R losses, and must be able to handle the peak inductor current without saturating. To minimize radiated noise, use a toroid, pot core or shielded bobbin inductor.

#### 10.3 C<sub>IN</sub> and C<sub>OUT</sub> Selection

In the boost region, input current is continuous. In the buck region, input current is discontinuous. In the buck region, the selection of input capacitor  $C_{IN}$  is driven by the need to filter the input square wave current. Use a low ESR capacitor sized to handle the maximum RMS current. For buck operation, the input RMS current is given by:

$$I_{CIN} = I_{OUT(MAX)} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(5)

This input current has a maximum at  $V_{IN} = 2V_{OUT}$ ,  $I_{CIN(MAX)} = I_{OUT(MAX)}/2$ .

In the boost region, C<sub>OUT</sub> must be capable of reducing the output voltage ripple because of the discontinuous output current. The effects of ESR (equivalent series resistance) and the bulk capacitance must be considered when choosing the right capacitor for a given output ripple voltage. The steady ripple due to charging and discharging the bulk capacitance is given by:

$$\Delta V_{\text{(BOOST,Cap)}} = \frac{I_{\text{OUT}(\text{MAX})}^{*}(V_{\text{OUT}}^{*}V_{\text{IN(MIN)}})}{C_{\text{OUT}}^{*}V_{\text{OUT}}^{*}f} V$$

(6)

where C<sub>OUT</sub> is the output filter capacitor.

The steady ripple due to the voltage drop across the ESR is given by:

$$\Delta V_{(BOOST,ESR)} = I_{OUT(MAX,BOOST)} *ESR$$

(7)

In buck mode, V<sub>OUT</sub> ripple is given by:

$$\Delta V_{OUT} \leq \Delta I_L^* \left( ESR + \frac{1}{8^* f^* C_{OUT}} \right)$$

(8)

Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements.

#### 10.4 Power MOSFET Selection and Efficiency Considerations

PL5501 requires four external N-channel power MOSFETs, two for the top switches (switches Q1 and Q3, shown in Figure 32) and two for the bottom switches (switches Q2 and Q4, shown in Figure 32). Important parameters for the power MOSFETs are the breakdown voltage  $V_{BR, DSS}$ , threshold voltage  $V_{GS,TH}$ , on-resistance  $R_{DS(ON)}$ , input capacitance  $C_{iSS}$  and maximum current  $I_{DS(MAX)}$ . The drive voltage is set by the 6.6V VCC supply to make the MOSFET's selection more flexible.

#### 10.5 Output voltage setting

The PL5501 output voltage is set by an external feedback resistive divider carefully placed across the output capacitor. The 1% resistance accuracy of this resistor divider is preferred. The resultant feedback signal is compared with the internal precision 2V voltage reference by the error amplifier. The output voltage is given by the equation:

$$V_{OUT} = 2V * \left(1 + \frac{R_1}{R_2}\right) \tag{9}$$

Where R<sub>1</sub> is the upper resistor and R<sub>2</sub> is the lower resistor in the feedback network.

### 11 PCB Layout

#### 11.1 Guideline

Layout is a critical portion of good power supply design. The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

- 1. The feedback network, resistor R1 and R2, should be kept close to the FB2 pin. Keep VBUS sensing path away from noisy nodes and preferably through a layer on the other side of shielding layer.

- The input /output bypass capacitor must be placed as close as possible to the VIN/VBUS pin and ground. Grounding for both the input and output capacitors should consist of localized top side planes that connect to the GND pin and PAD. It is a good practice to place a ceramic cap near the VINand VBUS pin to reduce the high frequency injection current.

- 3. The inductor L should be placed close to the SW1 and SW2 pin to reduce magnetic and electrostatic noise.

- 4. Current sensing pairs (CSP1,CSN1), (CSP2,CSN2) need to be placed carefully, Layout the lines symmetrically and keep them away from noisy nodes such as BST1,BST2, SW1, SW2, HG1,HG2, LG1,LG2 etc. Connect these nodes directly to the two terminals of current sensing resistors Rcs1, Rcs2 to form an accurate Kelvin connection.

#### 11.2 Application Examples

Fig. 31 Schematic

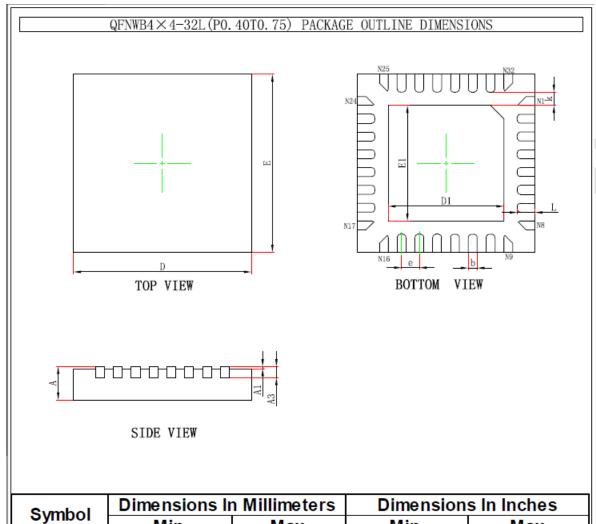

### 12 Packaging Information

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |  |  |  |

|--------|---------------------------|-------|----------------------|-------|--|--|--|--|

| Symbol | Min.                      | Max.  | Min.                 | Max.  |  |  |  |  |

| Α      | 0.700                     | 0.800 | 0.028                | 0.031 |  |  |  |  |

| A1     | 0.000                     | 0.050 | 0.000                | 0.002 |  |  |  |  |

| A3     | 0.203                     | REF.  | 0.008REF.            |       |  |  |  |  |

| D      | 3.900                     | 4.100 | 0.154                | 0.161 |  |  |  |  |

| E      | 3.900                     | 4.100 | 0.154                | 0.161 |  |  |  |  |

| D1     | 2.500                     | 2.700 | 0.098                | 0.106 |  |  |  |  |

| E1     | 2.500                     | 2.700 | 0.098                | 0.106 |  |  |  |  |

| k      | 0.300                     | REF.  | 0.012                | REF.  |  |  |  |  |

| b      | 0.150                     | 0.250 | 0.006                | 0.010 |  |  |  |  |

| е      | 0.400BSC.                 |       | 0.016                | BSC.  |  |  |  |  |

| L      | 0.300                     | 0.500 | 0.012                | 0.020 |  |  |  |  |

#### **IMPORTANT NOTICE**

Powlicon Inc. assumes no responsibility for any error which may appear in this document. Powlicon Inc. reserves the right to change devices or specifications detailed herein at any time without notice. Powlicon Inc. does not assume any liability arising out of the application or use of any product described herein; neither it does it convey any license under its patent rights, nor the rights of others. Powlicon Inc. products are not authorized for use as critical components in life support devices or systems without written approval letter from the Chief Executive Officer of Powlicon Inc. The use of products in such applications shall assume all risks of such use and will agree to not hold against Powlicon Inc. for any damage.