10/28/2022

# **Transition-Mode PFC Controller with THD Enhanced**

## REV: 00

# **General Description**

The LD7597 is a current mode PFC controller operating on critical conduction (CRM) or discontinuous (DCM) mode. It built in THDi improved circuit for all operating mode. It's based on DCM operation with frequency limitation method to improve the efficiency at light load condition.

The device is also integrated several functions of protection, such as over voltage protection (OVP), brown-in/out protection, saturation protection, under voltage protection (UVP), over temperature protection (OTP), GND open protection and over current protection (OCP) with high / low line compensation. Therefore it can protect the system from damage due to occasional failure.

# Features

- Critical conduction (CRM) or Discontinuous (DCM) Mode of PFC Pre-Regulator

- Peak Current Mode Control

- DCM operation with frequency limitation method

- Near-Unity Power Factor

- Ultra-Low THDi at Light Load Condition

- Line / Load Transient Enhance

- Brown-In/Out Detection on MULT pin

- ACOVP protection on MULT pin

- OVP (Output Overvoltage Protection) on INV pin

- UVP (Output Under-voltage Protection) on INV pin

- Saturation protection on CS pin

- GND open protection

- Internal OTP (Over Temperature Protection)

- 450/-850mA Driving Capability

# Applications

- Lighting Ballasts (LED, Fluorescent)

- All Off Line Appliances Requiring Power Factor Correction

Leadtrend Technology Corporation www.leadtrend.com.tw LD7597-DS-00 October 2022

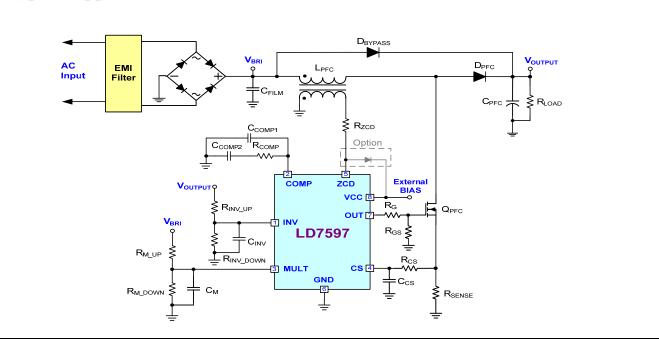

# **Typical Application for Boost PFC**

10/28/2022

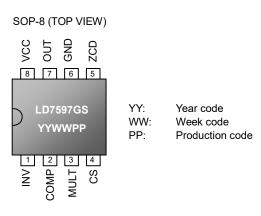

# **Pin Configuration**

# **Ordering Information**

| Part number | Package |               | Top Mark | Shipping          |

|-------------|---------|---------------|----------|-------------------|

| LD7597GS    | SOP-8   | Green package | LD7597GS | 2500 /tape & reel |

The LD7597GS is RoHS compliant/ Green Packaged.

# **Protection Mode**

| Part number | UVLO(on) | UVLO(off) | BNO  | SATP | ACOVP | OCP            | GNDOP | Int. OTP |

|-------------|----------|-----------|------|------|-------|----------------|-------|----------|

| LD7597      | 12.0V    | 7.5V      | Auto | Auto | Auto  | Cycle by Cycle | Auto  | Auto     |

# **Pin Descriptions**

| Pin | Name   | Function descriptions                                                                      |

|-----|--------|--------------------------------------------------------------------------------------------|

| 4   |        | Output voltage feedback control. Built in output over voltage protection (OVP) and under   |

| 1   | INV    | voltage protection (UVP) function.                                                         |

| 2   | COMP   | This pin is connected to the compensation network for power factor correction. The type II |

|     | COIVII | compensation is recommended                                                                |

| 3   | MULT   | Multiplier input pin. Built in BNI/BNO and input overvoltage protection (ACOVP) function.  |

| 4   | CS     | This pin is used to monitor the current of MOSFET.                                         |

| 5   | ZCD    | This pin is used for zero current detection.                                               |

| 6   | GND    | Ground.                                                                                    |

| 7   | OUT    | Gate drive output to drive the external MOSFET.                                            |

| 8   | VCC    | Supply voltage pin.                                                                        |

LD7597 10/28/2022

10/28/2022

# **Absolute Maximum Ratings**

| Supply Voltage VCC                                       | -0.3V ~ 30V                 |

|----------------------------------------------------------|-----------------------------|

| OUT                                                      | -0.3V ~ VCC +0.3V           |

| ZCD                                                      | -0.3V ~ 36V                 |

| ZCD source current                                       | 5mA                         |

| COMP, INV, MULT                                          | -0.3V ~ 6.0V                |

| CS                                                       | -0.3V ~ 6.0V                |

| Maximum Junction Temperature                             | -40°C ~150°C <sup>(1)</sup> |

| Storage Temperature Range                                | -65°C to 150°C              |

| Package Thermal Resistance (SOP-8, $\theta_{JA}$ )       | 160°C/W                     |

| Power Dissipation (SOP-8, at Ambient Temperature = 85°C) | 250mW                       |

| Lead temperature (Soldering, 10sec)                      | 260°C                       |

| ESD Voltage Protection, Human Body Model                 | 2.5 kV                      |

|                                                          |                             |

Note1: For system application, refer to recommended operating conditions.

### Caution:

Stress exceeding maximum ratings may damage the device. Maximum ratings are stress ratings only. Functional operation above the recommended operating conditions is not implied. Extended exposure to stress above recommended operating conditions may affect device reliability.

# **Recommended Operating Conditions**

| Item                           | Min. | Max. | Unit |

|--------------------------------|------|------|------|

| Operating Junction Temperature | -40  | 125  | °C   |

| VCC Capacitance                | 22   | 100  | μF   |

| COMP Capacitance               | 0.1  | 4.7  | μF   |

| MULT pin Filter Capacitance    | 100  | 1000 | pF   |

| INV pin Filter Capacitance     | 0.1  | 100  | nF   |

| ZCD detection Resistor         | 30   | 100  | kohm |

| ZCD source current             |      | 3    | mA   |

| CS pin Filter Capacitance      |      | 220  | pF   |

Note :

- 1. Exceeding these ratings may damage the device.

- 2. When operation at harsh environment condition, as temperature and humidity or climate change ...etc. Please pay attention to impedance variation between pin to pin or ground to avoid ripple remover closing loop and being failure.

- 3. The recommended operating conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Leadtrend does not recommend exceeding them or designing to absolute maximum ratings.

- 4. In selection of these external components, make sure that their values including temperature & tolerance characteristics are satisfied with the recommended ranges.

10/28/2022

# **Electrical Characteristics**

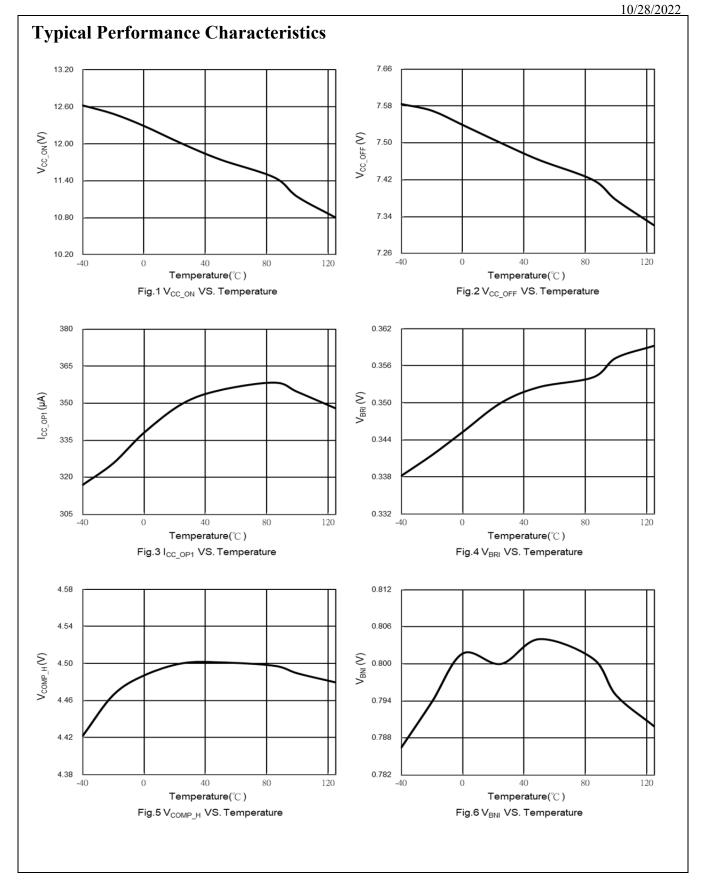

(VCC=14.0V,  $T_A = 25^{\circ}C$  unless otherwise specified.)

| PARAMETER                                            | CONDITIONS                                | SYMBOL                 | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------|-------------------------------------------|------------------------|-------|-------|-------|-------|

| VCC Pin                                              |                                           |                        |       |       |       | •     |

| Startup current                                      | V <sub>VCC</sub> < V <sub>CC_ON</sub>     | Icc_st                 |       | 1     | 3     | μA    |

|                                                      | V <sub>COMP</sub> =0V,no switching        | ICC_OP1                |       | 350   | 1500  | μA    |

| Operating current<br>(with no load on OUT pin)       | *; 50kHz switching<br>frequency condition | I <sub>CC_OP2</sub>    |       | 2.5   | 3.0   | mA    |

|                                                      | V <sub>INV</sub> =0V                      | I <sub>CC_OPA2</sub>   |       | 65    | 120   | μA    |

| UVLO (off)                                           |                                           | V <sub>CC_OFF</sub>    | 7.0   | 7.5   | 8.0   | V     |

| UVLO (on)                                            |                                           | V <sub>CC_ON</sub>     | 11    | 12    | 13.0  | V     |

| Idle mode breaking time                              | *; Re-cycle time                          | T <sub>BRE</sub>       | 40    | 60    | 80    | ms    |

| COMP Pin                                             | -                                         |                        |       | L.    |       |       |

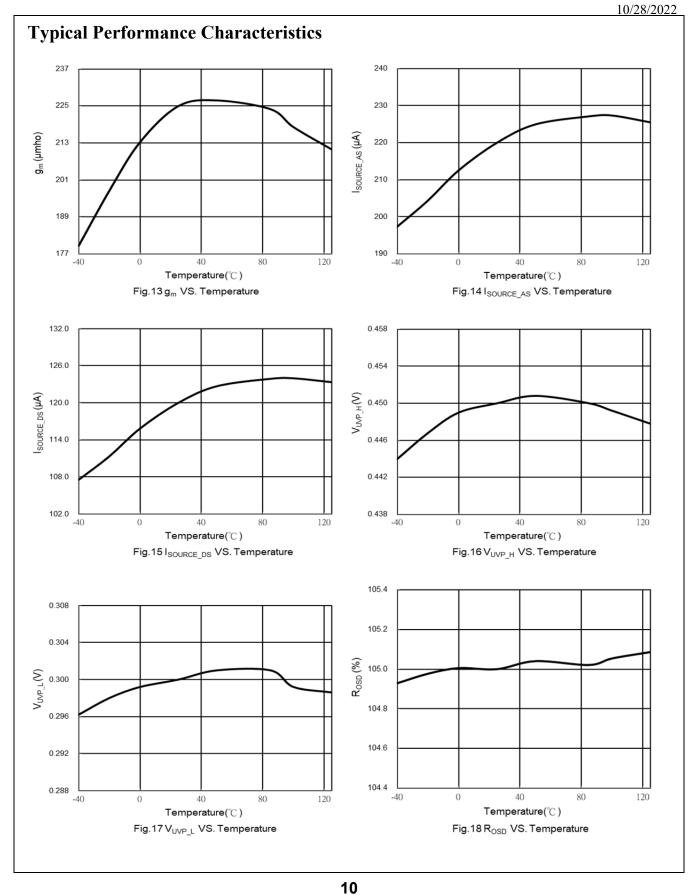

| Transconductance amplifier                           |                                           | Яm                     | 150   | 225   | 300   | μmho  |

| Maximum clamp voltage                                | *; V <sub>FB</sub> =2V                    | V <sub>COMP_H</sub>    | 4.27  | 4.5   | 4.73  | V     |

| Burst mode in threshold voltage                      |                                           | V <sub>BRI</sub>       | 0.25  | 0.35  | 0.45  | V     |

| Maximum switching frequency                          | *                                         | f <sub>SW MAX</sub>    | 340   | 400   | 460   | kHz   |

| Source current at USD is triggered during soft start | *; During soft start                      | I <sub>SOURCE_DS</sub> | 90    | 120   | 150   | μA    |

| Source current at USD is triggered after soft start  | After soft start                          | I <sub>SOURCE_AS</sub> | 180   | 220   | 260   | μA    |

| Maximum on time limit by $V_{\text{COMP}}$           | V <sub>COMP</sub> =4.50V                  | T <sub>ON_MAX</sub>    | 26    | 30    | 36    | μs    |

| Minimum on time limit by V <sub>COMP</sub>           | *; V <sub>COMP</sub> =0.55V               | T <sub>ON_MIN</sub>    | 3.5   | 5.0   | 6.5   | μs    |

| INV Pin                                              |                                           |                        |       |       |       |       |

| Internal reference voltage of error                  | Tj=25 °C                                  | V <sub>REF</sub>       | 2.475 | 2.500 | 2.525 | V     |

| Amplifier                                            | Tj=-40~125 °C                             | V <sub>REF</sub>       | 2.410 | 2.500 | 2.590 | V     |

| Undershoot detector (USD) threshold ratio            | Percentage of V <sub>REF</sub>            | R <sub>USD</sub>       | 94.0  | 96.0  | 97.5  | %     |

| Hysteresis of USD                                    | *; Percentage of V <sub>REF</sub>         | $\triangle R_{USD_H}$  | 1.0   | 2.0   | 3.0   | %     |

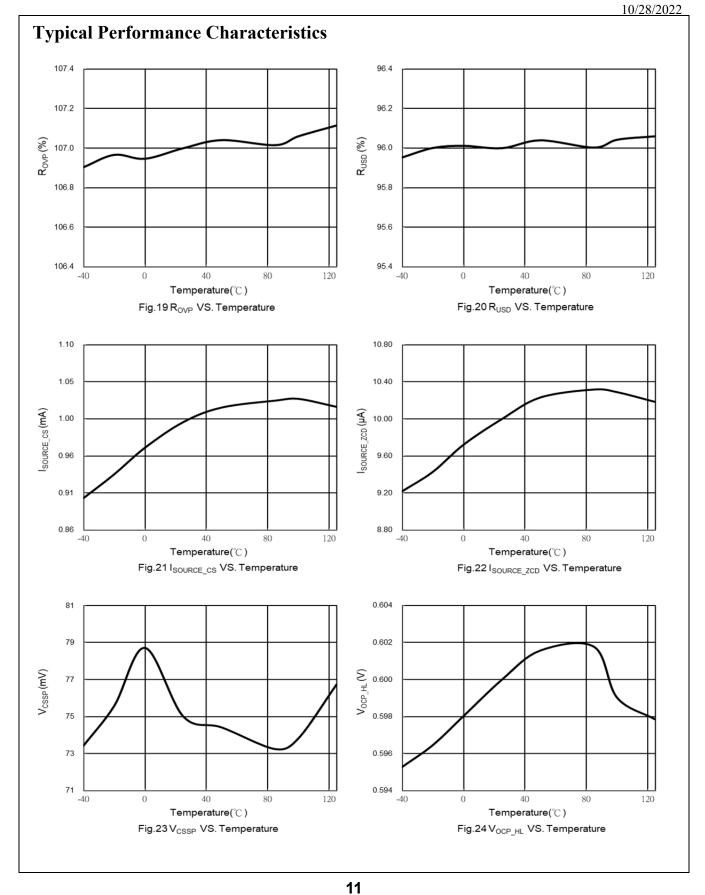

| Overshoot detector (OSD) threshold ratio             | Percentage of V <sub>REF</sub>            | R <sub>OSD</sub>       | 103.5 | 105.0 | 106.5 | %     |

| Hysteresis of OSD                                    | *; Percentage of V <sub>REF</sub>         | ∆R <sub>osd_h</sub>    | 1.0   | 2.0   | 3.0   | %     |

| OVP threshold ratio                                  | Percentage of V <sub>REF</sub>            | R <sub>OVP</sub>       | 103.2 | 107.0 | 110.8 | %     |

| Hysteresis of OVP                                    | *; Percentage of V <sub>REF</sub>         | R <sub>OVP_H</sub>     |       | Rosd  |       | %     |

| UVP released threshold voltage                       | V <sub>INV</sub> rising                   | V <sub>UVP_H</sub>     | 0.40  | 0.45  | 0.50  | V     |

| UVP triggered threshold voltage                      | V <sub>INV</sub> failing                  | V <sub>UVP_L</sub>     | 0.25  | 0.30  | 0.35  | mV    |

| Sink current of INV pin                              | *                                         | Isink_inv_t            | 100   | 200   | 300   | nA    |

10/28/2022

| PARAMETER                               | CONDITIONS                                     | SYMBOL                       | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|------------------------------------------------|------------------------------|------|------|------|-------|

| MULT Pin                                |                                                |                              |      |      |      |       |

| Brown in (BNI) threshold voltage        | assuming 1/Km=144                              | V <sub>BNI</sub>             | 740  | 800  | 860  | mV    |

| De-bounce time of BNI                   | *                                              | T <sub>DEB_BNI</sub>         | 20   | 30   | 40   | ms    |

| Brown out (BNO) threshold voltage       | assuming 1/Km=144                              | V <sub>BNO</sub>             | 630  | 700  | 770  | mV    |

| De-bounce time of BNO                   | *                                              | T <sub>DEB_BNO</sub>         | 40   | 60   | 80   | ms    |

| High line detected threshold voltage    | *                                              | $V_{HL}$                     | 1.51 | 1.65 | 1.79 | V     |

| Low line detected threshold voltage     | *                                              | V <sub>LL</sub>              | 1.33 | 1.45 | 1.57 | V     |

| Source current of MULT pin              | *                                              | I <sub>SOURCE_MU</sub>       | 100  | 200  | 300  | nA    |

| Cain of multiplian                      |                                                | KG <sub>MULT_HL</sub>        | 0.08 | 0.09 | 0.10 | 1/V   |

| Gain of multiplier                      |                                                | KG <sub>MULT_LL</sub>        | 0.27 | 0.30 | 0.33 | 1/V   |

| ACOVP threshold voltage                 |                                                | VACOVP                       | 3.1  | 3.2  | 3.3  | V     |

| Hysteresis of ACOVP                     | *                                              | V <sub>ACOVP_H</sub>         |      | -100 | _    | mV    |

| ACOVP de-bounce time                    | *                                              | T <sub>DEB_ACO</sub>         |      | 150  |      | μs    |

| CS Pin                                  |                                                |                              |      |      |      | -     |

| Source current of CS pin before startup | Pulse width =160µs<br>watchdog, before startup | I <sub>SOURCE_CS</sub>       | 0.86 | 1.00 | 1.1  | mA    |

| CSSP threshold voltage                  | Before startup                                 | V <sub>CSSP</sub>            | 50   | 75   | 100  | mV    |

| CSOP threshold voltage                  | *; Before startup                              | V <sub>CSOP</sub>            | 1.9  | 2.0  | 2.1  | V     |

|                                         | *; LL condition                                | $V_{SATP_{LL}}$              | 1.45 | 1.60 | 1.78 | V     |

| SATP threshold voltage                  | *; HL condition                                | $V_{SATP_{HL}}$              | 0.75 | 0.85 | 0.95 | V     |

| Quala hu avala limitation throat ald    |                                                | $V_{\text{OCP}_{\text{HL}}}$ | 0.54 | 0.60 | 0.66 | V     |

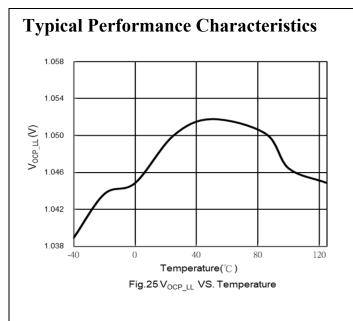

| Cycle by cycle limitation threshold     | *                                              | $V_{OCP\_LL}$                | 0.95 | 1.05 | 1.15 | V     |

| LEB for cycle by cycle limitation       | From OUT pin is rising.                        | T <sub>LEB_OCP</sub>         | 280  | 350  | 420  | ns    |

| LEB for SATP                            | *; From OUT pin is rising.                     | $T_{LEB}_{SATP}$             | 80   | 150  | 220  | ns    |

10/28/2022

| VCC=14.0V, $T_A = 25^{\circ}C$ unless other        |                                                                                   |                      |       |       |       |       |

|----------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-------|-------|-------|-------|

| PARAMETER                                          | CONDITIONS                                                                        | SYMBOL               | MIN   | TYP   | MAX   | UNITS |

| ZCD Pin                                            | Г                                                                                 |                      |       |       |       | 1     |

| Source current of ZCD pin before Startup           | Pulse width =160μs<br>watchdog before startup                                     | Isource_zcd          | 8.5   | 10.0  | 11.1  | μA    |

| ZCDOP threshold voltage                            | Before startup                                                                    | V <sub>ZCDOP</sub>   | 1.9   | 2.0   | 2.1   | V     |

| ZCDSP threshold voltage                            | Before startup                                                                    | V <sub>ZCDSP</sub>   | 120   | 175   | 235   | mV    |

| Zero current detection high threshold voltage      | *; Rising                                                                         | V <sub>QRDH</sub>    | 0.675 | 0.750 | 0.825 | V     |

| Zero current detection triggered threshold voltage | *; Falling                                                                        | V <sub>QRDL</sub>    | 0.20  | 0.25  | 0.30  | V     |

| Time out for normal operating                      | *; $V_{ZCD} \ge V_{QRDH}$ once during $V_{OUT}$ is low and w/o $V_{QRDL}$ signal. | TO1                  | 30    | 35    | 40    | μs    |

| Time out for abnormal condition                    | $V_{ZCD} < V_{QRDH}$ during $V_{OUT}$ is low.                                     | TO2                  | 150   | 200   | 250   | μs    |

| Time out for SATP                                  | *; $V_{CS} \ge V_{SATP_XL}$ , From<br>$T_{LEB_SATP}$ to OUT pin is<br>falling.    | тоз                  | 400   | 800   | 1200  | μs    |

| Blanking time for QRD                              | *; After gate-off.                                                                | T <sub>BLA</sub>     | 0.5   | 1.0   | 1.5   | μs    |

| OUT Pin                                            |                                                                                   |                      |       |       |       |       |

| Output low level                                   | *; VCC=12V, I <sub>SINK</sub> =20mA                                               | V <sub>OL</sub>      |       |       | 0.5   | V     |

| Output high level                                  | *; VCC=12V,I <sub>SOURCE</sub> =20mA                                              | V <sub>OH</sub>      |       | 11.3  |       | V     |

| Output high clamp level                            | *; VCC=18V                                                                        | V <sub>O_CLAMP</sub> |       | 13.5  |       | V     |

| Rising time                                        | *; VCC=14V, CL=1nF                                                                | Tr                   |       | 76    |       | ns    |

| Falling time                                       | *;VCC=14V, C <sub>L</sub> =1nF                                                    | T <sub>f</sub>       |       | 26    |       | ns    |

| Internal OTP                                       |                                                                                   |                      |       |       |       |       |

| OTP trip level                                     | *                                                                                 | T <sub>OTP</sub>     |       | 140   |       | °C    |

| Hysteresis of OTP                                  | *                                                                                 | $\Delta T_{OTP}$     |       | 20    |       | °C    |

\*: Guaranteed by design.

Leadtrend Technology Corporation www.leadtrend.com.tw LD7597-DS-00 October 2022

Leadtrend Technology Corporation www.leadtrend.com.tw LD7597-DS-00 October 2022

Leadtrend Technology Corporation www.leadtrend.com.tw LD7597-DS-00 October 2022

Leadtrend Technology Corporation www.leadtrend.com.tw LD7597-DS-00 October 2022

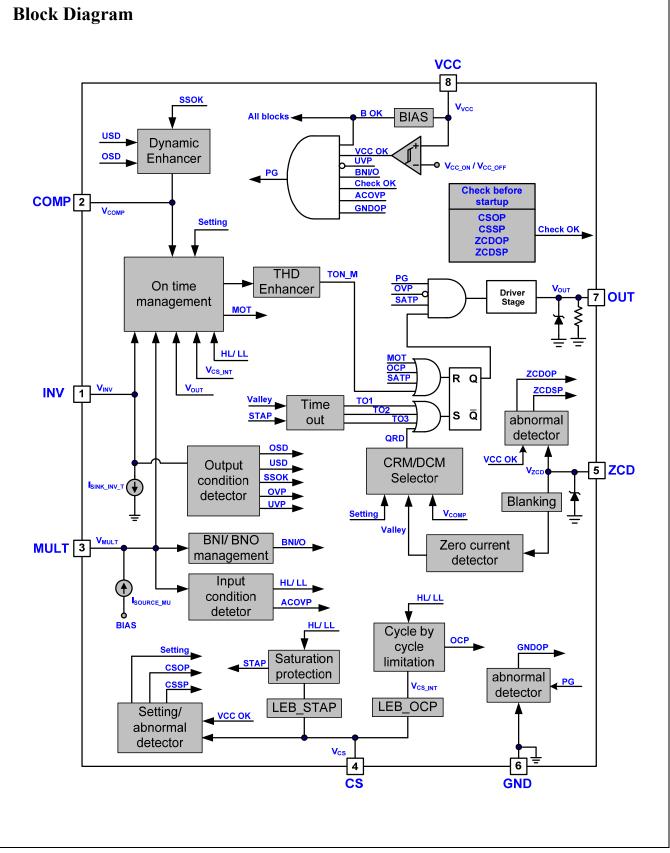

# Application Information Operation Overview

LD7597 is designed for power factor correction with boost topology. It's achieved the high efficiency across the all operating range of line and load with DCM operation and frequency limitation method. Base on the current mode control algorithm with THD improved function, LD7597 could operate as transition mode at full load condition or DCM mode at light load condition with ultra-low THD.

## Zero Current Detection (ZCD)

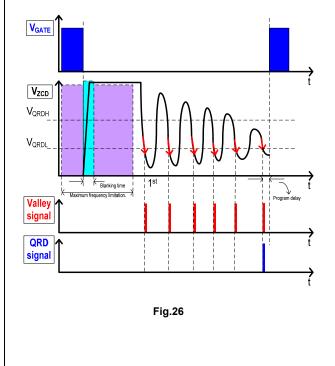

The block of zero current detection will detect auxiliary winding signal to drive MOSFET. As shown in Fig.26. During gate off, if  $V_{ZCD}$  is higher than  $V_{QRDH}$  (0.75V, typ. Level trigger once) then each time lower under  $V_{QRDL}$  (0.25V, typ. falling edge trigger) as valley signal, the current of inductor will be closed zero at first valley. According to  $V_{COMP}$  level, valley signal will be selected and became QRD signal to turn on MOSFET again. For typical application (output=390~450V), Recommended the turn ratio of transformer is around 10.

# ZCD check after VCCOK

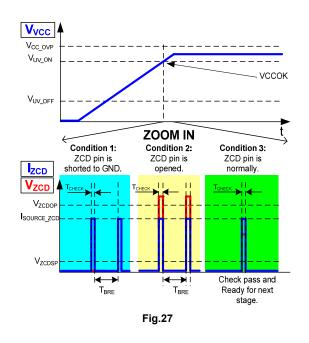

As shown in Fig.27. After VCCOK ( $V_{VCC} \ge V_{CC_ON}$ , 12.0V, typ.), LD7597 provides an internal constant current source ( $I_{SOURCE_ZCD}$ , 10µA, typ.) for ZCD pin about 160µs ( $T_{CHECK}$ , typ.).  $V_{ZCD}$  is detected to check the condition of soldered. If  $V_{ZCD}$  is higher than  $V_{ZCDOP}$  (2.0V, typ.), ZCDOP is triggered. LD7597 operates into idle mode and re-check again after  $T_{BRE}$  (60ms, typ.). If  $V_{ZCD}$  is lower than  $V_{ZCDSP}$  (175mV, typ.), ZCDSP is triggered. LD7597 operates into idle mode and re-check again after  $T_{BRE}$ . Once  $V_{ZCDSP}$

LD7597

10/28/2022

## **Time Out function**

13

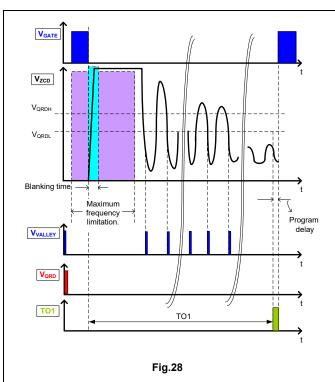

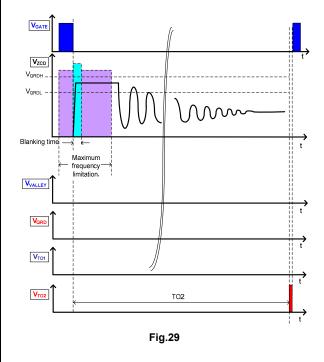

During gate off time, if valley signal is triggered but without QRD signal, the time-out 1 function is active. The switching period is limited at TO1 ( $35\mu$ s, typ.). As shown in Fig.28. The other condition, during off time, if valley signal is not triggered, the time-out 2 function is active. The switching period is limited at TO2 ( $200\mu$ s, typ.). As shown in Fig.29.

## 10/28/2022

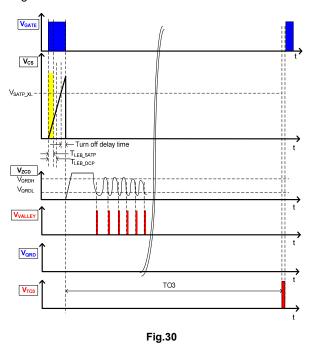

When OUT pin is rising and after  $T_{LEB\_SATP}$ , once  $V_{CS}$  is higher than  $V_{SATP\_XL}$  (1.6V at HL, 0.85 at LL). OUT pin is off immediately and TO3 function (Saturation protection,

STAP) is active, the switching period is limited at TO3 (800µs, typ.) to prevent any damaged. As shown in Fig.30.

# **Current Sense**

## CS setting and Check before startup

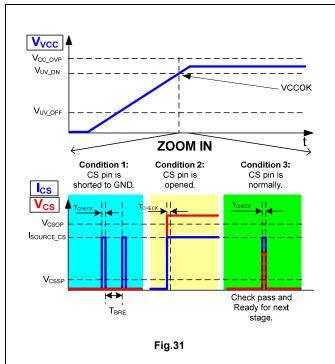

After VCCOK, LD7597 provides an internal constant current source ( $I_{SOURCE_CS}$ , 1mA, typ.) for CS pin about 160µs ( $T_{CHECK}$ , typ.), this V<sub>CS</sub> is detected to set operation at transition mode or DCM mode of V<sub>COMP</sub> threshold level and check the condition of soldered. If V<sub>CS</sub> setting voltage is lower than V<sub>CSSP</sub> (75mV, typ.) CSSP is triggered. LD7597 operates into idle mode and re-setting again after T<sub>BRE</sub>. If V<sub>CS</sub> is higher than V<sub>CSOP</sub> (2.0V, typ.), CSOP is triggered. V<sub>CS</sub> is always pulled high until fault condition is removed and LD7597 recheck CS pin condition again. If V<sub>CSSP</sub><V<sub>CS</sub><V<sub>CSOP</sub>, CS check is pass and LD7597 is ready to operates into next stage. As shown in Fig.31.

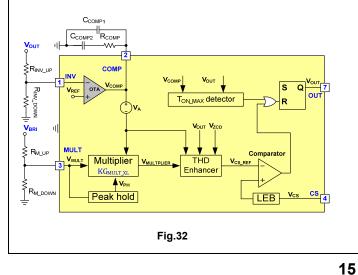

# Current Mode Control and THD Compensation

LD7597 is current mode control PFC controller. Different to traditional current mode PFC controller is the error amplifier. It uses the transconductance amplifier to replace the operational amplifier. That will increase the operable range of COMP pin and suit for LED application. As shown in Fig.32. For DCM operation, LD7597 built in the internal compensation circuit to modify on time to achieve the high PF and low THD.

LD7597

10/28/2022

According to the function block and ignore the THD enhancer, obtained the following equations,

$$\begin{split} V_{CS\_REF} &\approx V_{MULTIPLIER} \\ &\approx V_{MULT} \times (V_{COMP} - V_A) \times KG_{MULT\_XL} \ (eq.1) \end{split}$$

Where:  $KG_{MULT_XL}$  is gain of multiplier, if low line input  $K_{GMULT_LL}=0.3$  (typ.), if high line input  $K_{GMULT_HL}=0.09$  (typ.).  $V_A=0.5V$  (typ.).

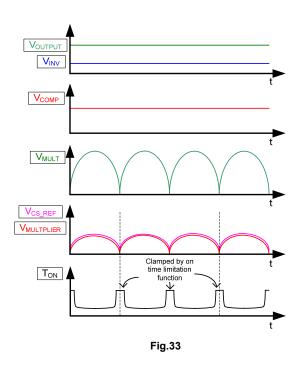

Due to the THD improved function, LD7597 is operating at VOT (Variable On-time) method. As shown in fig 33.

The output voltage is defined as below.

$$V_{OUTPUT} = V_{REF} \times \frac{R_{INV\_DOWN} + R_{INV\_UP}}{R_{INV\_DOWN}}$$

(eq.2)

Where V<sub>REF</sub>=2.5V (typ.).

Recommended resistance of  $R_{INV_DOWN}$  range is 20k~33k ohm.

## **On Time Limitation**

Due to LD7597 operates at VOT method and it turns on the MOSFET almost 100 percent duty cycle near the zero crossing of input AC voltage. That will cause the current distortion by spike. So add another on time limitation function is necessary which is controlled by  $V_{COMP}$ , obtained the following equations,

$$T_{ON\_MAX} = \left(6.311 \frac{\mu s}{v} \times V_{COMP}\right) + 1.6\mu s \text{ (eq.3)}$$

From the equation 3, the maximum on time is  $30\mu$ s (typ.) at V<sub>COMP</sub> equals to 4.5V. The maximum on time is 5.0 $\mu$ s (typ.) at V<sub>COMP</sub> equals to 0.55V.

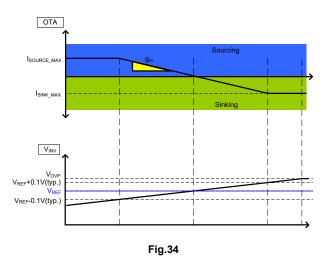

#### Transconductance Amplifier

As shown in Fig.34. Gain of OTA is  $225\mu$ mho (typ.) at the range of V<sub>INV</sub> is from V<sub>REF</sub>-0.1V (typ.) to V<sub>REF</sub>+0.1V (typ.). The maximum sink (I<sub>SINK\_MAX</sub>) and source (I<sub>SOURCE\_MAX</sub>) current is  $22.5\mu$ A (typ.). The non-inverting input terminal of OTA is connected to the reference voltage (V<sub>REF</sub>, 2.5V, typ.).

## **Function of MULT Pin**

#### Source current for MULT pin open status

LD7597 provides an internal constant source current ( $I_{SOURCE_MU}$ ) about 200nA (typ.) for MULT pin open protection. Once it is open, MULT pin is pulled high

16

# LD7597

10/28/2022

immediately. ACOVP is triggered after de-bounce time and auto-recovery when the fault condition is removed.

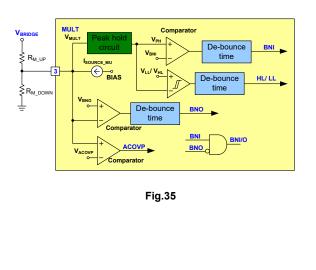

#### Peak holding and brown in/ out function

LD7597 implements the peak voltage holding function on MULT pin. The peak voltage of MULT pin ( $V_{PH}$ ) is used for brown in and high/low line detection. As shown in Fig.35.

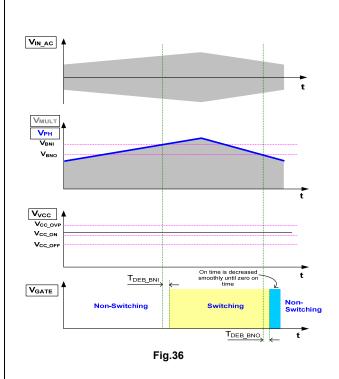

## **BNO/BNI** function

As shown in Fig.36. If  $V_{PH}$  is higher than  $V_{BNI}$  (800mV, typ.) with de-bounce time  $T_{DEB_BNI}$  (30ms, typ.), the BNI is triggered and if others check (ZCD, CS, UVP check) are pass, LD7597 operates into next stage and gate begin switching. If  $V_{MULT}$  is lower than  $V_{BNO}$  (700mV, typ.) with de-bounce time  $T_{DEB_BNO}$  (60ms, typ.), the on time will decreased smoothly until zero on time to avoid the false triggered of BNI again.

## HL/LL detect function

The HL/LL condition is defined by V<sub>PH</sub>. If V<sub>PH</sub> is higher than V<sub>HL</sub> (1.65V, typ.) with de-bounce time 1ms (max.), the HL condition is triggered and LD7597 changes the key parameters for high line input. Once V<sub>PH</sub> is lower than V<sub>LL</sub> (1.45V, typ.) with de-bounce time 25ms (typ.), the LL condition is triggered and LD7597 changes the key parameters for low line input.

# **Dynamic Improved and OVP of INV Pin**

## Sink current for INV pin open status

Internal constant current source  $(I_{SINK\_INV\_T})$  always provides about 200nA (typ.) for INV pin open protection. Once it is open, INV pin is pulled low to ground immediately. UVP is triggered and LD7597 operates into idle mode.

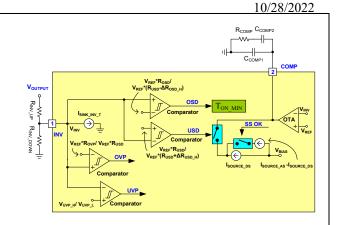

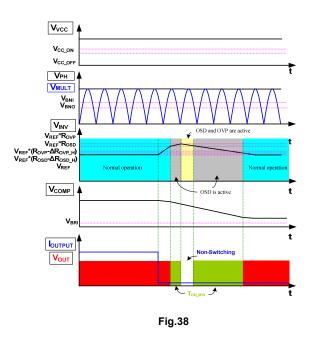

## Dynamic improved (Overshoot detector, OSD)

As shown in Fig.37 and Fig.38. The inverting input of OSD comparator is connected to  $V_{REF_OSD}$  ( $R_{OSD}*V_{REF}$ ), if  $V_{INV}$  is higher than  $V_{REF_OSD}$ , OSD is triggered,  $T_{ON}$  is minimum to limit output voltage rising until the  $V_{INV}$  is lower than ( $(R_{OSD}-\triangle R_{OSD_H})*V_{REF}$ ).

LD7597

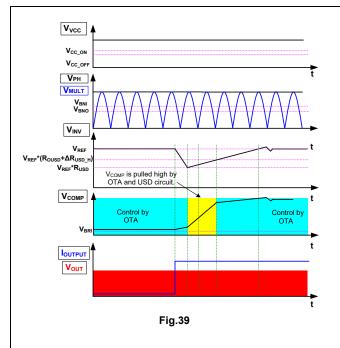

## Dynamic improved (Undershoot detector, USD)

The non-inverting input of USD comparator is connected to  $V_{REF\_USD}$  ( $R_{USD}*V_{REF}$ ). During soft start, once USD is triggered,  $I_{SOUCRE\_DS}$  (120µA, typ.) is active to pull  $V_{COMP}$  high until the  $V_{INV}$  is lower than (( $R_{USD}+ \triangle R_{USD\_H}$ )\*  $V_{REF}$ ). After soft start ( $V_{INV}$ >  $V_{REF\_USD}$ ),  $I_{SOUCRE\_AS}$  (220µA, typ.) is active and waiting to the next USD is occurred. As shown in Fig.39.

17

10/28/2022

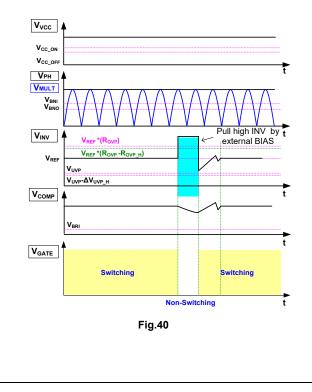

## Over voltage protection

As shown in Fig.40. If  $V_{INV}$  is higher than  $V_{OVP}$  ( $R_{OVP}^*V_{REF}$ ), OVP is triggered. LD7597 is gate off immediately until  $V_{INV}$  is lower than ( $R_{OSD}^* V_{REF}$ ). During OVP is triggered,  $V_{COMP}$  is pulled low by OTA circuit.

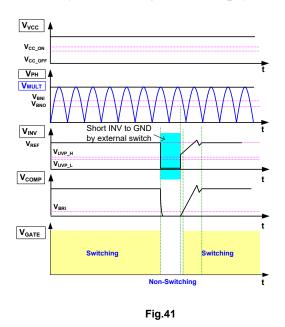

## Under voltage protection

As shown in Fig.41. After VCCOK, if  $V_{INV}$  is lower than  $V_{UVP_{L}}$  (0.3V, typ.), UVP is triggered, LD7597 is gate off immediately until  $V_{INV}$  is higher than  $V_{UVP_{-H}}$  (0.45V, typ).

### **Over current protection**

LD7597 provides the cycle by cycle current limitation by monitor CS pin. After  $T_{LEB\_OCP}$  (350ns, typ.), if V<sub>CS</sub> is higher than V<sub>OCP\_XL</sub>, OCP is triggered. The gate is off immediately until next switching cycle. V<sub>OCP\_XL</sub> is defined as table.1.

|         | LL condition | HL condition |

|---------|--------------|--------------|

| Vocp_xL | 1.05V (typ.) | 0.6V (typ.)  |

Table.1

18

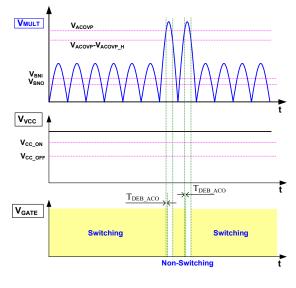

## AC over voltage protection

If  $V_{MULT} \ge V_{ACOVP}$  with de-bounce time  $T_{DEB\_ACO}$  (150µs, typ.), ACOVP is detected, LD7597 will gate off immediately to prevent from any damage until the internal signal  $V_{MULT}$  is lower than  $V_{ACOVP}$  - $V_{ACOVP\_H}$ . As shown in Fig.42.

Fig.42

#### Internal Over Temperature Protection (int. OTP)

When the junction temperature reaches 140°C approximately, the thermal sensor signals would stop IC's switching. If the IC's junction temperature cools by 20°C or VCC restart again.

19

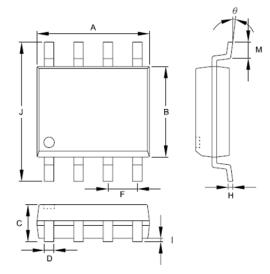

# **Package Information** SOP-8

|        | Dimensions i | n Millimeters | Dimensions in Inch |       |  |

|--------|--------------|---------------|--------------------|-------|--|

| Symbol | MIN          | МАХ           | MIN                | МАХ   |  |

| А      | 4.801        | 5.004         | 0.189              | 0.197 |  |

| В      | 3.810        | 3.988         | 0.150              | 0.157 |  |

| С      | 1.346        | 1.753         | 0.053              | 0.069 |  |

| D      | 0.330        | 0.508         | 0.013              | 0.020 |  |

| F      | 1.194        | 1.346         | 0.047              | 0.053 |  |

| н      | 0.178        | 0.254         | 0.007              | 0.010 |  |

| I      | 0.102        | 0.254         | 0.004              | 0.010 |  |

| J      | 5.791        | 6.198         | 0.228              | 0.244 |  |

| М      | 0.406        | 1.270         | 0.016              | 0.050 |  |

| θ      | 0°           | 8°            | 0°                 | 8°    |  |

LD7597 10/28/2022

# **Revision History**

| REV. | Date       | Change Notice          |

|------|------------|------------------------|

| 00   | 10/28/2022 | Original Specification |

# **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice.

Customers should verify the datasheets are current and complete before placing order.

10/28/2022