# Low Quiescent Current Boost Converter

### **Description**

The FP6722 is a high efficiency hysteretic current mode topology synchronous boost DC/DC converter which could operate from single/dual-cell NiCd, NiMH or alkaline battery such as input voltage below 0.7V. The converter output voltage can be adjusted from 1.8V to a maximum of 5.5V by an external resistor divider. Besides the converter includes a 0.5 $\Omega$  N-channel MOSFET switch and 0.7 $\Omega$  P-channel synchronous rectifier. So no external Schottky diode is required and could get better efficiency near 94%.

The FP6722 is available in a space-saving SOT-23-6 package for portable application.

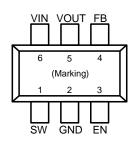

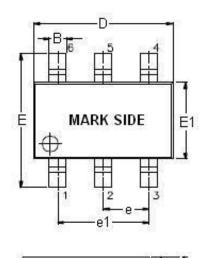

# **Pin Assignments**

S6 Package (SOT-23-6)

Figure 1. Pin Assignment of FP6722

### **Features**

- Low IQ, 5.5μA Max Quiescent Current

- Operating Input Voltage from 0.7V to 5.5V

- Feedback Voltage 500mV

- 500mA Switching Current Limit

- Hysteresis switching frequency

- Adjustable Output Voltage from 1.8V to 5.5V

- Input Under Voltage Lockout

- Very Low Shutdown Current at 0.2uA

- ± 2.6% Output Voltage Accuracy

- Output Overvoltage Protection

- Over-Temperature Protection

- Pass-Through Function during Shutdown

- SOT-23-6 Package

### **Applications**

- Handheld Instrument

- Cordless Phone

- Wireless Handset

- GPS Receiver

- Battery Powered Applications

- 1 to 3 Cell Alkaline, NiCd or NiMH

- 1 Cell Li-Ion or Li-Primary

- White or Status LEDs

- Smartphones

# **Ordering Information**

#### SOT-23-6 Marking

| Part Number | Product Code |  |  |

|-------------|--------------|--|--|

| FP6722S6    | FX9          |  |  |

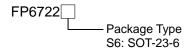

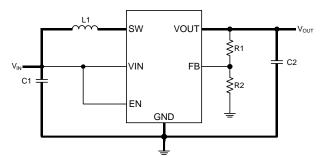

# **Typical Application Circuit**

Figure 2. Typical Application Circuit of FP6722

# **Functional Pin Description**

| Pin Name | Pin No. | Pin Function                                                                                                                                                                          |  |  |  |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| sw       | 1       | Switch input pin which is connected to inductor.                                                                                                                                      |  |  |  |  |

| GND      | 2       | Ground pin.                                                                                                                                                                           |  |  |  |  |

| EN       | 3       | Chip-enable input. The converter will work when this pin is connected to logic high. It will shut off when this pin is connected to logic low.                                        |  |  |  |  |

| FB       | 4       | The feedback input for adjusting output voltage. This pin connects resistor divider that output voltage could be adjusted from 1.8V to 5.5V. The feedback voltage is typical at 0.5V. |  |  |  |  |

| VOUT     | 5       | Output voltage pin.                                                                                                                                                                   |  |  |  |  |

| VIN      | 6       | Input voltage pin.                                                                                                                                                                    |  |  |  |  |

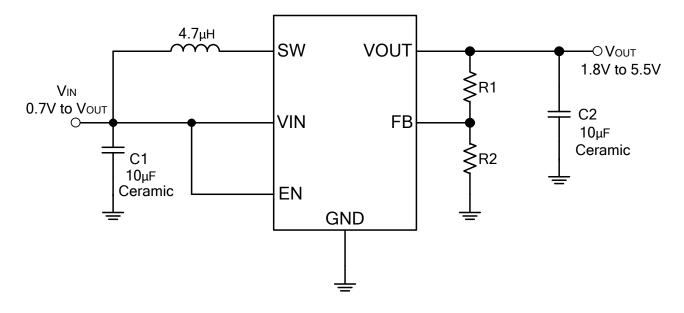

# **Block Diagram**

Figure 3. Block Diagram of FP6722

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage (VIN ,VOUT, EN, FB)                                                       | -0.3V to +6V      |

|--------------------------------------------------------------------------------------------------|-------------------|

| • SW Voltage (SW)                                                                                | -0.3V to +6V      |

| • Power Dissipation @T <sub>A</sub> =25°C, SOT-23-6 (P <sub>D</sub> )                            | 0.5W              |

| $\bullet$ Package Thermal Resistance, SOT-23-6 ( $\theta_{\text{JA}})$                           | 250°C/W           |

| • Maximum Junction Temperature (T <sub>J</sub> )                                                 | +150°C            |

| • Storage Temperature Range (T <sub>S</sub> )                                                    | -65°C to +150°C   |

| • Lead Temperature (Soldering, 10 sec.) (T <sub>LEAD</sub> )                                     | +260°C            |

| Note 1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage | ge to the device. |

# **Recommended Operating Conditions**

- Input Voltage (V<sub>IN</sub>) ------+0.7V to V<sub>OUT</sub>

FP6722-Preliminary 0.3-MAR-2019

# **Electrical Characteristics**

( $V_{IN}$ =1.2V, EN= $V_{IN}$ ,  $T_A$ =25°C, unless otherwise specified.)

| Parameter                                       | Symbol              | Conditions                                           | Min                  | Тур  | Max                  | Unit |

|-------------------------------------------------|---------------------|------------------------------------------------------|----------------------|------|----------------------|------|

| Start-up Voltage                                | V <sub>ST</sub>     | $R_{Load} {\ge} 150 \Omega$                          |                      |      | 0.7                  | V    |

| Output Voltage Range                            | V <sub>OUT</sub>    | V <sub>IN</sub> <v<sub>OUT 1.8</v<sub>               |                      |      | 5.5                  | V    |

| Over Voltage Protection                         | Vovp                |                                                      | 5.5                  | 6.2  |                      | V    |

| Shutdown Current from Power Source              | I <sub>SD</sub>     | EN=0V                                                |                      | 0.2  | 0.5                  | μΑ   |

| Quiescent Current (VIN)                         | ] ,                 | $V_{EN}=V_{IN}=1.2 \text{ V}, V_{OUT}=3.3 \text{V},$ |                      | 0.5  | 0.9                  | μΑ   |

| Quiescent Current (Vout)                        | - I <sub>Q</sub>    | Non-switching                                        |                      | 5.5  |                      | uA   |

| Switch Current Limit (Note 2)                   | I <sub>LIM</sub>    | V <sub>OUT</sub> =3.3V , V <sub>IN</sub> =1.2V       |                      | 0.5  |                      | Α    |

| Feedback Voltage                                | V <sub>FB</sub>     |                                                      | 487                  | 500  | 513                  | mV   |

| FB Input Bias Current                           | I <sub>FB</sub>     |                                                      |                      | 0.01 | 0.1                  | μΑ   |

| NMOS Switch ON Resistance                       | R <sub>DS(ON)</sub> | V <sub>OUT</sub> =3.3V                               |                      | 0.5  |                      | Ω    |

| PMOS Switch ON Resistance                       | R <sub>DS(ON)</sub> | V <sub>OUT</sub> =3.3V                               |                      | 0.7  |                      | Ω    |

| Under voltage lockout threshold for<br>Turn off | Vuvlo               | V <sub>IN</sub> decreasing                           |                      | 0.5  | 0.7                  | V    |

| EN Input Low Voltage                            | VIL                 | V <sub>IN</sub> <1.5V                                |                      |      | V <sub>IN</sub> ×0.2 | V    |

| EN Input High Voltage                           | V <sub>IH</sub>     | V <sub>IN</sub> <1.5V                                | V <sub>IN</sub> ×0.8 |      |                      | V    |

| EN Input Low Voltage                            | V <sub>IL</sub>     | 1.5V <v<sub>IN&lt;5V</v<sub>                         |                      |      | 0.4                  | V    |

| EN Input High Voltage                           | V <sub>IH</sub>     | 1.5V <v<sub>IN&lt;5V</v<sub>                         | 1.2                  |      |                      | V    |

| EN Input Current                                |                     | EN=GND or V <sub>IN</sub>                            |                      | 0.01 | 0.1                  | μΑ   |

| Over-Temperature Protection (Note 2)            | T <sub>SD</sub>     |                                                      |                      | 150  |                      | °C   |

| Over-Temperature Protection                     | $\Delta T_{SD}$     | Hysteresis                                           |                      | 20   |                      | °C   |

Note 2: Not production tested.

# **Typical Performance Curves**

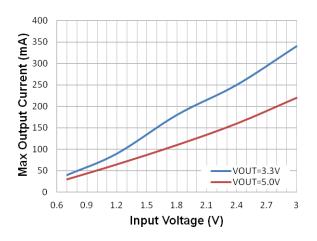

Figure 4. Maximum Output Current vs. Input Voltage

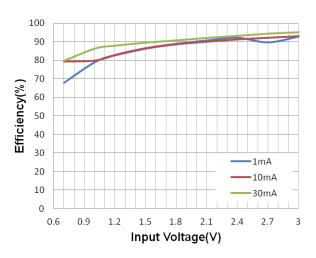

Figure 6. Efficiency vs. Input Voltage (V<sub>OUT</sub>=3.3V)

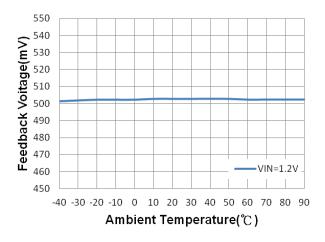

Figure 8. Feedback Voltage vs. Temperature(V<sub>OUT</sub>=3.3V)

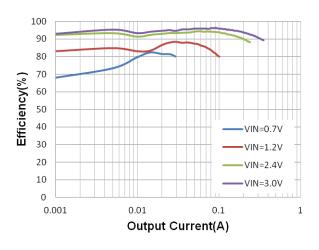

Figure 5. Efficiency vs. Output Current (V<sub>OUT</sub>=3.3V)

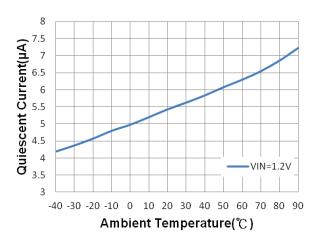

Figure 7. Quiescent Current vs. Temperature (V<sub>OUT</sub>=3.3V)

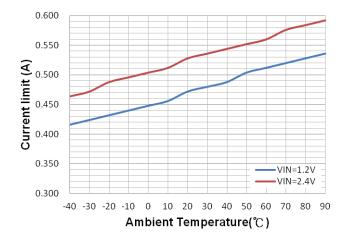

Figure 9. Current Limit vs. Temperature (V<sub>OUT</sub>=3.3V)

FP6722-Preliminary 0.3-MAR-2019

# **Typical Performance Curves (Continued)**

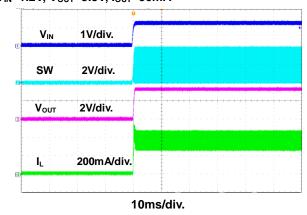

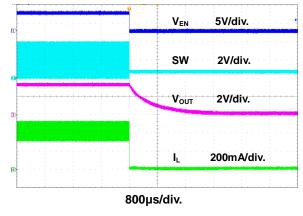

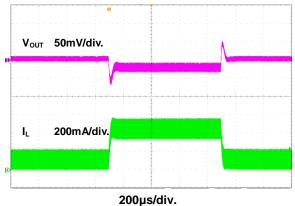

### V<sub>IN</sub>=1.2V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=90mA

Figure 10. Power On through V<sub>IN</sub> Waveform

### V<sub>IN</sub>=1.2V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=90mA

Figure 11. Power Off through V<sub>IN</sub> Waveform

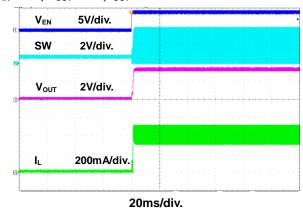

### $V_{IN}$ =0.7V, $V_{OUT}$ =3.3V, $I_{OUT}$ =50mA

Figure 12. Power On through EN Waveform

### $V_{IN}$ =0.7V, $V_{OUT}$ =3.3V, $I_{OUT}$ =50mA

Figure 13. Power Off through EN Waveform

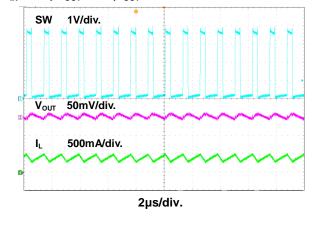

### $V_{IN}$ =1.2V, $V_{OUT}$ =3.3V, $I_{OUT}$ =90mA

Figure 14. Switching Waveform

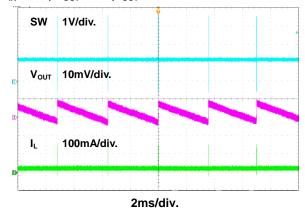

### $V_{IN}$ =1.2V, $V_{OUT}$ =3.3V, $I_{OUT}$ =0mA

Figure 15. Switching Waveform

# **Typical Performance Curves (Continued)**

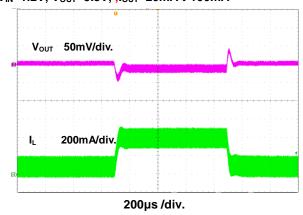

### $V_{IN}=1.2V$ , $V_{OUT}=3.3V$ , $I_{OUT}=20mA \rightarrow 100mA$

Figure 16. Load Transient Response

### $V_{IN}=2.4V$ , $V_{OUT}=3.3V$ , $I_{OUT}=60mA \rightarrow 250mA$

Figure 17. Load Transient Response

### **Application Information**

#### **Controller Circuit**

The FP6722 is a high performance, highly efficiency synchronous boost converter. The device is controlled by a hysteretic current mode controller. This controller regulates the output voltage by keeping the inductor ripple current constant in the range of 200mA and adjusting the offset of this inductor current depending on the output load. In case the required average input current is lower than the average inductor current defined by this constant ripple the inductor current gets discontinuous to keep the efficiency high at low load conditions.

#### **Synchronous Rectifier**

The device integrates an N-channel and a P-channel MOSFET transistor to realize a synchronous rectifier. There is no additional Schottky diode required. Because the device uses a integrated low  $R_{\rm DS(ON)}$  PMOS switch for rectification, the power conversion efficiency reaches 94%.

### **Device Enable**

The device will be shut down when EN is set to GND. In this mode, the regulator stops switching, all internal control circuitry will be turned off.

The device is put into operation when EN is set high. During start-up of the converter, the duty cycle is limited in order to avoid high peak currents drawn from the battery. The limit is set internally by the current limit circuit.

### Adjustable Output Voltage

The accuracy of the output voltage is determined by the accuracy of the internal voltage reference, the controller topology, and the accuracy of the external resistor. The reference voltage has an accuracy of ±2.6%. The tolerance of the resistors in the feedback divider determines the total system accuracy.

### **Design Procedure**

The FP6722 boost converter family is intended for systems that are powered by a single-cell NiCd or NiMH battery with a typical terminal voltage between 0.7V to 1.6V. It can also be used in systems that are powered by two-cell NiCd or NiMH batteries with a typical stack voltage between 1.8V to 5.5V. Additionally, single or dual-cell, primary and secondary alkaline battery cells can be the power source in systems where the FP6722 is used.

### **Application Information (Continued)**

### **Programming the Output Voltage**

The output voltage of the FP6722 can be adjusted with an external resistor divider. The typical value of the voltage on the FB pin is 500mV in fixed frequency operation. The maximum allowed value for the output voltage is 5.5V. The current through the resistive divider should be about 100 times greater than the current into the FB pin. The typical current into the FB pin is 0.1 $\mu$ A, and the voltage across R2 is typically 500mV. Based on those two values, the recommended value for R1 is in the range of  $1M\Omega$ . From that, the value of resistor R2, depending on the needed output voltage (Vo), can be calculated using Equation 1.

$$R2 = \left(\frac{V_{FB} \times R1}{V_{OUT} - V_{FB}}\right) = \left(\frac{0.5V \times 1M\Omega}{V_{OUT} - 0.5V}\right) \dots (1)$$

#### **Inductor Selection**

A boost converter normally requires two main passive components for storing energy during the conversion. A boost inductor is required and a storage capacitor at the output. To select the boost inductor, it is recommended to keep the possible peak inductor current below the current limit threshold of the power switch in the chosen configuration.

The second parameter for choosing the inductor is the desired current ripple in the inductor. Normally, it is advisable to work with a ripple of less than 20% of the average inductor current. A smaller ripple reduces the magnetic hysteresis losses in the inductor, as well as output voltage ripple and EMI. But in the same way, regulation time at load changes rises. In addition, a larger inductor increases the total system cost. With those parameters, it is possible to calculate the value for the inductor by using Equation 2.

$$L = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{\Delta I_L \times f \times V_{OUT}} \dots (2)$$

Parameter f is the switching frequency and  $\Delta I_L$  is the ripple current in the inductor, i.e, 20% x  $I_L$ . With this calculated value and currents, it is possible to choose a suitable inductor. Care must be taken that load transients and losses in the circuit can lead to higher currents. Also, the losses in the inductor caused by magnetic hysteresis losses and copper losses are a major parameter for total circuit efficiency.

### **Capacitor Selection**

The major parameter necessary to define the output capacitor is the maximum allowed output voltage ripple of the converter. This ripple is determined by two parameters of the capacitor, the capacitance and the ESR. It is possible to calculate the minimum capacitance needed for the defined ripple, supposing that the ESR is zero, by using Equation 3.

$$C_{MIN} = \frac{I_{OUT} \times (V_{OUT} - V_{IN})}{f \times \Delta V \times V_{OUT}} \dots (3)$$

Parameter f is the switching frequency and  $\triangle V$  is the maximum allowed ripple.

The total ripple is larger due to the ESR of the output capacitor. This additional component of the ripple can be calculated using Equation 4.

$$\Delta V_{ESR} = I_{OUT} \times R_{ESR}$$

.....(4)

The total ripple is the sum of the ripple caused by the capacitance and the ripple caused by the ESR of the capacitor. It is possible to improve the design by enlarging the capacitor or using smaller capacitors in parallel to reduce the ESR or by using better capacitors with lower ESR, like ceramics. Tradeoffs must be made between performance and costs of the converter circuit.

A  $10\mu F$  input capacitor is recommended to improve transient behavior of the regulator. A ceramic or tantalum capacitor with a 100nF in parallel placed close to the IC is recommended.

#### **Thermal Information**

The maximum junction temperature ( $T_J$ ) of the FP6722 devices is recommended to 150°C. The thermal resistance of the SOT-23-6 package is  $\theta_{JA}$ =250°C/W. Specified regulator operations are assured to ambient temperature ( $T_A$ ) of 25°C. Therefore, the maximum power dissipation is about 500mW. More power can be dissipated if the maximum ambient temperature of the application is lower.

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{JA}} = \frac{150^{\circ}\text{C} - 25^{\circ}\text{C}}{250^{\circ}\text{C/W}} = 500 \text{mW}$$

# **Application Information (Continued)**

### **Layout Considerations**

As for all switching power supplies, the layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the regulator could show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path as indicated in bold in Figure 18. The input capacitor, output capacitor and the inductor should be placed as close to the IC as possible. Use a common ground node as shown in Figure 18 to minimize the effects of ground noise. The feedback divider should be placed as close to the IC as possible.

Figure 18. Layout Diagram

# **Outline Information**

SOT-23-6 Package (Unit: mm)

| SYMBOLS | S DIMENSION IN MILLIMETER |      |  |  |

|---------|---------------------------|------|--|--|

| UNIT    | MIN                       | MAX  |  |  |

| Α       | 0.90                      | 1.45 |  |  |

| A1      | 0.00                      | 0.15 |  |  |

| A2      | 0.90                      | 1.30 |  |  |

| В       | 0.30                      | 0.50 |  |  |

| D       | 2.80                      | 3.00 |  |  |

| E       | 2.60                      | 3.00 |  |  |

| E1      | 1.50                      | 1.70 |  |  |

| е       | 0.90                      | 1.00 |  |  |

| e1      | 1.80                      | 2.00 |  |  |

| L       | 0.30                      | 0.60 |  |  |

Note: Followed From JEDEC MO-178-C.

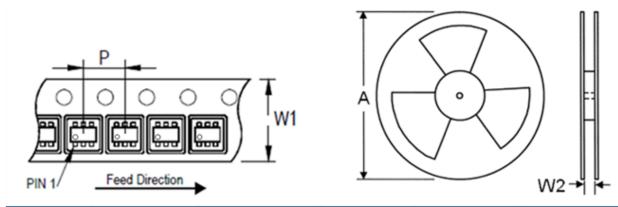

### **Carrier Dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|-----------|--------------|---------------|-----|------------|--------------|----------------|

| (W1) mm   | (P) mm       | in            | mm  | (W2) mm    | Length mm    |                |

| 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

**Life Support Policy**Fitipower's products are not authorized for use as critical components in life support devices or other medical systems.