# K32W1480

# K32W14x Product Family

Ultra-low-power, Highly Secure, Multiprotocol Wireless MCU

Rev. 3 — 12/2022

K32W1480VFTBT K32W1480VFTBR

Data Sheet: Technical Data

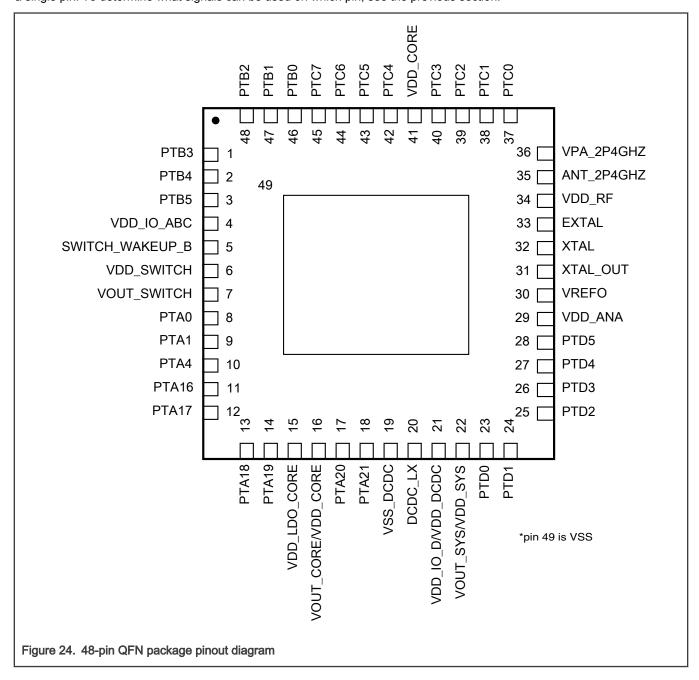

48HVQFN

7 x 7 x 0.85 mm; Pitch 0.5 mm

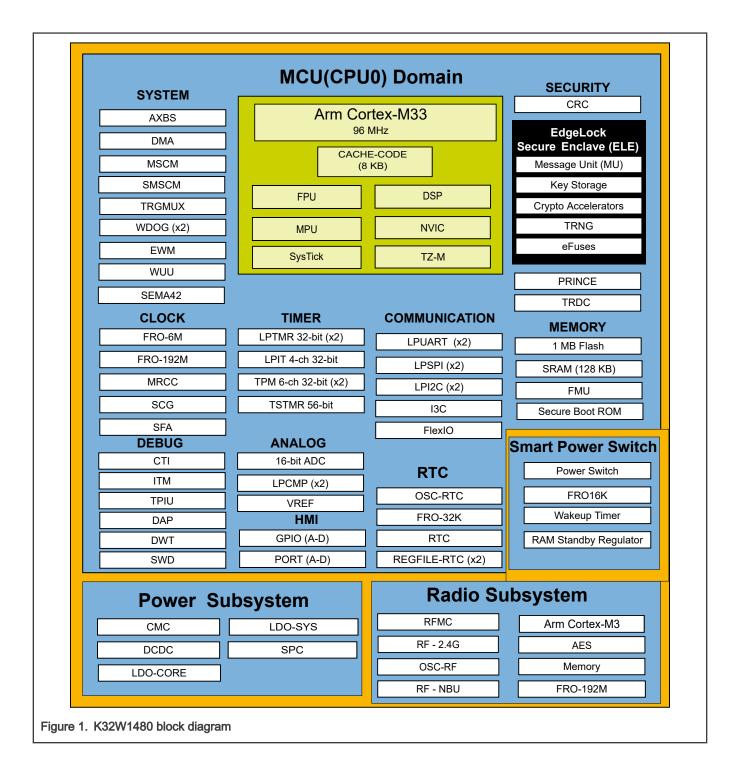

The K32W14x product family is a low-power, highly secure, single chip multiprotocol wireless MCU that integrates a high performance Bluetooth Low Energy version 5.3 radio and an IEEE 802.15.4 radio supporting Thread, Matter and Zigbee. The K32W14x implements a tri-core architecture to isolate the connectivity, computing and security capabilities.

The multiprotocol radio is energy efficient, supports full simultaneous dual-PAN to enable Thread and Zigbee, and designed for Wi-Fi coexistence. The radio is supported with tested software stacks for Matter, Thread, Zigbee and Bluetooth Low Energy for standalone and hosted applications to enable a range of IoT and industrial applications.

The K32W14x integrates a state-of-the-art, scalable security architecture including Arm<sup>®</sup> TrustZone<sup>®</sup>-M, a resource domain controller and an isolated EdgeLock<sup>™</sup> Secure Enclave supporting hardware cryptographic accelerators, random number generators, key generation, storage and management, and secure debug. Flash memory contents can optionally be stored as encrypted data and then decrypted on-the-fly enabling protection of sensitive data and algorithms.

The K32W14x implements a flexible power efficient architecture to extend battery life and reduce energy footprint in IoT devices

#### Application core

- Up to 96 MHz Arm Cortex<sup>®</sup>-M33 core

- TrustZone-M, IEEE 754 FPU, DSP, MPU, NVIC, SysTick

- 8 KB Code Cache to improve performance and efficiency

- 1 MB flash memory

- 128 KB SRAM

- · Secure Boot ROM

- Bluetooth LE Controller stack and transceiver drivers contained in on-chip radio memory, preserving more onchip system memory for host stack and application space

#### Target applications

- · Smart Home IoT

- Smart Home environmental, occupancy, and security sensors

- Home Gateways and Bridges

- Smart Lighting

#### **EdgeLock Secure Enclave**

- · Secure boot and debug

- Trusted resource domain controller (TRDC) providing programmable control mechanisms for independent processing domains including embedded memory and peripherals

- Privilege/user

- Data only

- Execute only

- Read-only access

- Secure/Non-secure

- · Advanced flash access protection

- Write/Erase protection, Execute only, Data only access control

- Optional encryption and on-the-fly decryption using a PRINCE XEX block cipher mode

- · Hardware encryption and decryption

Table continues on the next page...

NXP reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

- Smart Plugs

- Access Control

- HVACs and Thermostats

- Window Shades

- · Industrial/IoT

- Positioning/Localization

- Building Control and Monitoring

- Building HVAC Control

- Fire and Security

- Smart Lighting

- Access Control

#### Narrow Band Radio Unit

- · Dedicated CM3 core running at up to 64 MHz

- 256 kB Flash supporting upgradable software radio

- · 88 KB SRAM optimized for link layer support

- IEEE 802.15.4 Radio

- IEEE 802.15.4-2015 compliant radio

- -103 dBm 250 kbps Receive Sensitivity

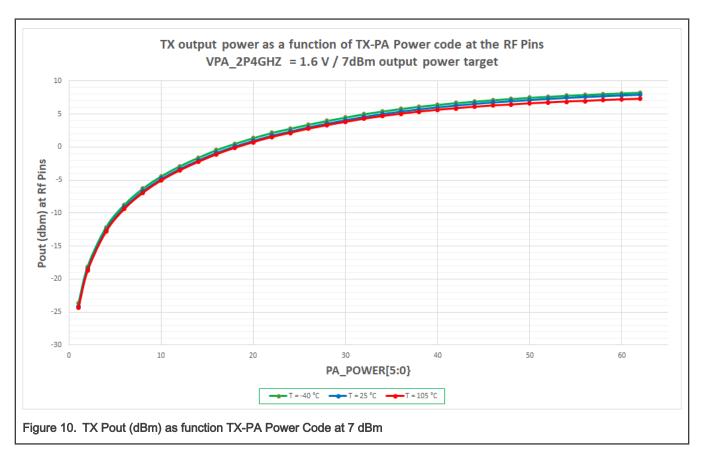

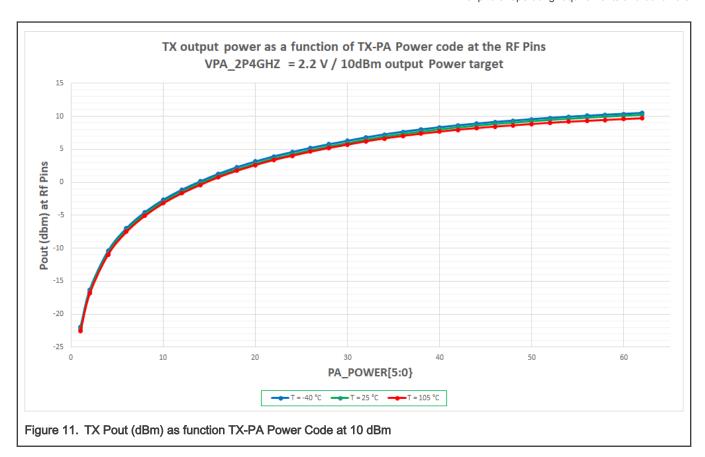

- Programmable Transmit Output Power up to +10 dBm

- Improved Enhanced ACK timing support in the 802.15.4 hardware which enables synchronized broadcasts to a larger number of sleepy end devices – for example, synchronous window blinds actuation

- Supports Dual PAN which allows a single radio to participate in two 802.15.4 Personal Area Networks

- Modulation Types: 2 Level FSK, GFSK, MSK, GMSK

- Single ended bidirectional RF port

- Low external component counts for low cost, small form-factor designs

- · Bluetooth Low Energy radio core

- Up to 24 simultaneous connections

- -106 dBm 125 kbps Long Range Receive Sensitivity

- –102 dBm 500 kbps Long Range Receive Sensitivity

- Symmetric Key Encryption

- AES-128/192/256

- ECB, CBC, CFB, OFB, CTR, GCM, CMAC, and CCM Modes

- · ChaCha20

- Asymmetric Key Encryption

- · RSA-2048/3072/4096

- FCC NIST P-192/224/256/384/521

- Curve25519

- Key Exchange Algorithms

- ECDH(E)

- SPAKE2+

- JPAKE

- Digital Signature Algorithms

- · ECDSA

- · Ed25519

- Hash Algorithms

- SHA2-224/256/384/512

- Poly1305

- · Secure key generation, storage, and management

- Pseudo (PRNG) and True Random Number Generator (TRNG) with 512-bits entropy supporting NIST SP 800-90A and SP 800-90B

- Support for secure over-the-air (OTA) firmware updates

- Four digital tamper pins with optional interrupt and seconds timestamp upon trigger

- Universally Unique ID (UUID) programmed by NXP during factory programming

- 24-bit unique IEEE media access control (MAC) subaddress

- · Factory Root of Trust programming

#### Low-power consumption (DCDC 3.6 V, 25 °C)

- Typical active core current: < 5.3 mA at 96 MHz (< 55 μA/MHz)</li>

- Transceiver current (DC-DC buck mode, 3.3 V supply)

- Typical RX: 4.7 mA

- Typical TX at 0 dBm: 4.6 mA

- –97.5 dBm 1 Mbps Receive Sensitivity

- –95 dBm 2 Mbps Receiver Sensitivity

- Programmable Transmit Output Power up to +10 dBm

- Data Rates: 125 kbps, 500 kbps, 1 Mbps, and 2 Mbps

- Modulation Types: 2 Level FSK, GFSK, MSK, GMSK

- Integrated memories in radio containing Bluetooth LE Controller Stack and radio drivers

- On-chip balun with single ended bidirectional RF port

- Low external component counts for low cost, small form-factor designs

#### Safety

- Memory Protection Unit (MPU)

- · Register write protection

- · Illegal memory access

- · Flash area protection

- SRAM Error Correction Code (ECC) and SRAM parity error check

- Clock Frequency Accuracy Measurement Circuit (CAC) using Signal Frequency Analyzer (SFA) module

- · Cyclic Redundancy Check (CRC) calculator

- Two internal, independent, and one external watchdog timers

- · Clock loss detection

- Main oscillator stop detection (Loss of lock detection)

- · Low voltage / high voltage detection

#### System peripherals

- DC/DC converter supporting buck and bypass operating modes

- Asynchronous DMA controller with per channel access permissions (secure/non-secure)

- Two internal and one external watchdog monitors

- · Nested vectored interrupt controller

- Wakeup unit for power down modes

#### Analog modules

- Typical TX at 10 dBm: 18.7 mA

- Less than 3 µA in Power-down mode with real-time clock (RTC) active and 32 KB SRAM retention

- Less than 1.5 μA in Deep Power-down mode with RTC active

- Multiple power-down modes supporting currents as low as 300 nA

- Ultra-low leakage Smart Power Switch with less than 100 nA sleep current with exit from internal timer or GPIO.

#### Clocks

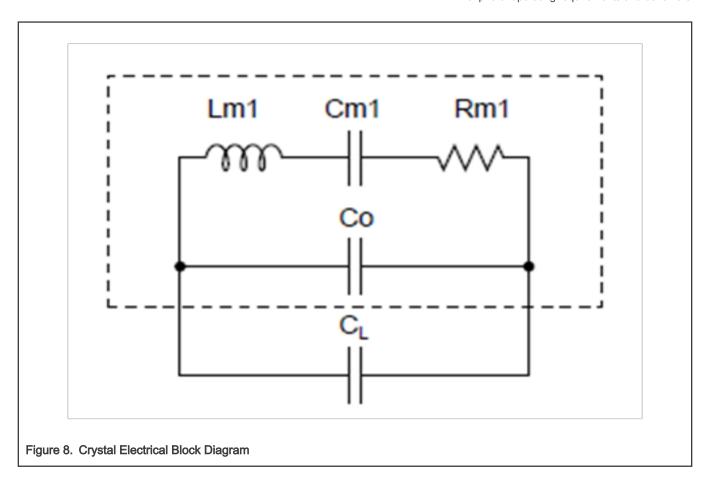

- · 32 MHz RF crystal oscillator

- · 32.768 kHz crystal oscillator

- Internal 192 MHz high frequency free running oscillator providing 48/64/96 MHz clock

- Internal low frequency free running oscillator providing 6 MHz clock

- Internal low-power free running oscillator providing 32 kHz clock

#### Communication interfaces

- · Two Low Power UART (LPUART) modules

- · Two Low Power SPI modules and one MIPI-I3C module

- Two Low Power I2C (LPI2C) modules supporting the System Management Bus (SMBus) Specification, version

- One programmable FlexIO module supporting emulation of UART, I2C, I2S, SPI, Camera IF, LCD RGB, PWM/ Waveform generation

#### **Timers**

- · One 2-channel 32-bit timers (LPTPM)

- Two 6-channel 32-bit timers (LPTPM) with PWM capability and DMA support

- Two 32-bit low-power timers (LPTMR) or pulse counters with compare features

- 4-channel 32-bit low-power periodic interrupt timer (LPIT) with DMA support

- One 56-bit timestamp timer

- 32-bit seconds real time counter (RTC) with 32-bit alarm and independent power supply

- Signal frequency analyzer (SFA) provides facilities for measurement of clock period/frequency as well as time between triggers

3/90

- 16-bit single ended SAR Analog-to-digital converter (ADC) up to 2 Msps

- Two 6-bit High-speed analog comparators (CMP) with 8-bit digital-to-analog converter (DAC)

- 1.0 V to 2.1 V Voltage Reference (Vref)

#### Operating characteristics

- Temperature range (ambient): -40 °C to 105 °C

- Temperature range (junction): -40 °C to 125 °C

- DC/DC voltage range: 1.71 V to 3.6 V

- Bypass voltage range: 1.71 V to 3.6 V

#### Input supply voltage options:

- Integrated DCDC regulator 1.71 V–3.6 V providing power to Core\_LDO regulator, SYS\_LDO regulators, and Radio

- Integrated Core\_LDO regulator 1.2 V–3.6 V powering the core digital domain

- Integrated SYS\_LDO regulator 1.71 V to 3.6 V powering the SYS domain

- DCDC and Core\_LDO regulators can support bypass modes

- Radio Analog: 1.2 V-3.6 V

- Radio PA: 0.9 V–2.4 V

#### **Human Machine Interface modules**

General-purpose input/output (GPIO)

Table 1. Ordering Information

| Part Number       | Packaging<br>Type | Protocol                  | Memory<br>(Flash/<br>RAM) | Packages         | Qualification                                   |

|-------------------|-------------------|---------------------------|---------------------------|------------------|-------------------------------------------------|

| K32W1480VFT<br>BT | Tray              | Bluetooth LE 5.3, Thread, | 1 MB/128<br>KB            | 7x7 48-pin HVQFN | Industrial –40 °C to + 105 °C (T <sub>A</sub> ) |

| K32W1480VFT<br>BR | Tray and<br>Reel  | Zigbee,<br>Matter         |                           |                  |                                                 |

#### Table 2. Device Revision Number

| Device Mask Set Number | SIM_SDID[REVID] |

|------------------------|-----------------|

| P43C                   | 0b10            |

#### Table 3. Related Resources

| Туре                | Description                                                                                                      | Resource                |

|---------------------|------------------------------------------------------------------------------------------------------------------|-------------------------|

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device. | K32W1480RM              |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                       | This document           |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.         | KW45_K32W1_2P43C        |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                             | • 48 HVQFN:SOT619-17(D) |

# Contents

| 1       | Ratings8                                        | 3.2.5       | Free-running oscillator FRO-32K specificati           | ons  |

|---------|-------------------------------------------------|-------------|-------------------------------------------------------|------|

| 1.1     | Thermal handling ratings8                       |             |                                                       | . 36 |

| 1.2     | Moisture handling ratings8                      | 3.2.6       | Free-running oscillator FRO-16K specificati           | ons  |

| 1.3     | ESD and Latch-Up Ratings8                       |             |                                                       | . 36 |

| 1.4     | Voltage and current maximum ratings8            | 3.3         | Memories and memory interfaces                        | 37   |

| 1.5     | Required Power-On-Reset (POR) Sequencing        | 3.3.1       | Flash electrical specifications                       | . 37 |

|         | 9                                               | 3.3.1.1     | Flash Read wait state control specifications          | 37   |

| 1.6     | Power Sequence10                                | 3.3.1.2     | Flash timing specifications                           | . 37 |

| 2       | General10                                       | 3.3.1.3     | Flash high voltage current behavior                   | 38   |

| 2.1     | AC electrical characteristics10                 | 3.3.1.4     | Flash reliability specifications                      |      |

| 2.2     | Nonswitching electrical specifications10        | 3.4         | Radio modules                                         | . 39 |

| 2.2.1   | Voltage and current operating requirements.10   | 3.4.1       | 2.4 GHz radio transceiver electrical                  |      |

| 2.2.2   | HVD, LVD, and POR operating requirements        |             | specification                                         | . 39 |

|         | 12                                              | 3.4.2       | Receiver Feature Summary                              |      |

| 2.2.3   | Voltage and current operating behaviors 13      | 3.4.3       | Transmit and PLL Feature Summary                      |      |

| 2.2.4   | On-chip regulator electrical specifications 15  | 3.5         | Analog                                                |      |

| 2.2.4.1 | DCDC converter specifications15                 | 3.5.1       | ADC electrical specifications                         |      |

| 2.2.4.2 | LDO_SYS electrical specifications17             | 3.5.1.1     | 16-bit ADC operating conditions                       |      |

| 2.2.4.3 | LDO_CORE electrical specifications18            | 3.5.1.2     | 16-bit ADC electrical characteristics                 |      |

| 2.2.5   | Smart power switch19                            | 3.5.2       | CMP and 8-bit DAC electrical specifications           |      |

| 2.2.6   | Power mode transition operating behaviors20     | 3.5.3       | Voltage reference electrical specifications           |      |

| 2.2.7   | Power consumption operating behaviors20         | 3.6         | Timers                                                |      |

| 2.2.7.1 | Power Consumption Operating Behaviors 20        | 3.7         | Communication interfaces                              |      |

| 2.2.7.2 | SoC Power Consumption25                         | 3.7.1       | LPUART                                                |      |

| 2.2.7.3 | Typical power-down mode RAM current adders      | 3.7.2       | LPSPI switching specifications                        |      |

|         | 25                                              | 3.7.3       | Inter-Integrated Circuit Interface (I <sup>2</sup> C) |      |

| 2.2.7.4 | Low power mode peripheral power                 |             | specifications                                        | . 64 |

|         | consumption adders26                            | 3.7.4       | Improved Inter-Integrated Circuit Interface           |      |

| 2.2.8   | EMC radiated emissions operating behaviors      |             | (MIPI-I3C) specifications                             | 66   |

|         | 28                                              | 3.8         | Human Machine Interface (HMI) modules                 |      |

| 2.2.9   | Designing with radiated emissions in mind 29    | 3.8.1       | General Purpose Input/Output (GPIO)                   |      |

| 2.2.10  | Capacitance attributes                          | 3.8.2       | Flexible IO controller (FlexIO)                       |      |

| 2.3     | Switching specifications29                      | 4           | Package dimensions                                    |      |

| 2.3.1   | Device clock specifications29                   | 4.1         | Obtaining package dimensions                          |      |

| 2.3.2   | General switching specifications29              | 5           | Pinout                                                |      |

| 2.4     | Thermal specifications                          | 5.1         | Pinout Table                                          |      |

| 2.4.1   | Thermal operating requirements31                | 5.2         | Recommended connection for unused anal                |      |

| 2.4.2   | Thermal attributes                              | <b>0.</b> _ | and digital pins                                      | -    |

| 3       | Peripheral operating requirements and behaviors | 5.3         | Pinouts diagram                                       |      |

|         |                                                 | 6           | Ordering parts                                        |      |

| 3.1     | Core modules31                                  | 6.1         | Determining valid orderable parts                     |      |

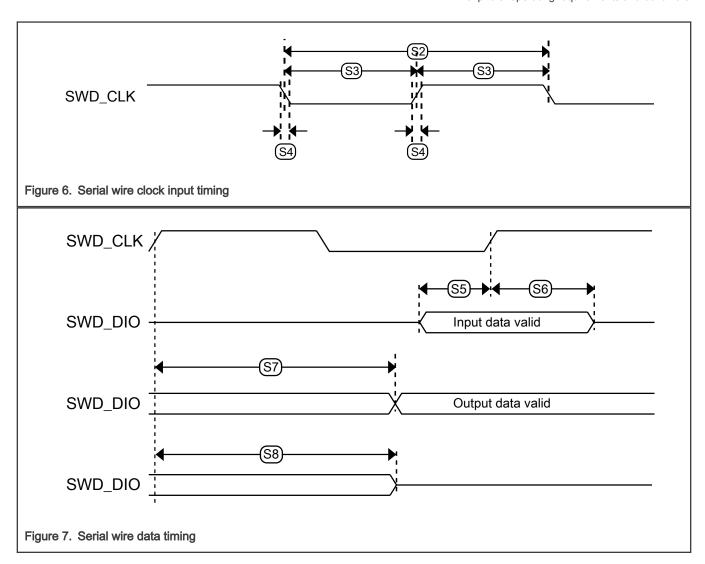

| 3.1.1   | SWD electricals31                               | 7           | Part identification                                   |      |

| 3.2     | Clock modules32                                 | 7.1         | Part number format                                    |      |

| 3.2.1   | Reference oscillator specification              | 7.2         | Example                                               |      |

| 3.2.2   | 32 kHz oscillator electrical specifications34   | 7.3         | Package marking                                       |      |

| 3.2.3   | Free-running oscillator FRO-192M                | 7.3.1       | Package marking information                           |      |

| 5.2.0   | specifications35                                | 8           | Terminology and guidelines                            |      |

| 3.2.4   | Free-running oscillator FRO-6M specifications   | 8.1         | Definitions                                           |      |

| Ų.∠. T  | 36                                              | 8.2         | Examples                                              |      |

|         |                                                 | 8.3         | Typical-value conditions                              |      |

|         |                                                 | 0.0         | . , piodi valdo contallono                            |      |

| 8.4 | Relationship between ratings and operating | 9          | Abbreviations and Acronyms | .81  |

|-----|--------------------------------------------|------------|----------------------------|------|

|     | requirements81                             | 10         | Revision history           | . 83 |

| 8.5 | Guidelines for ratings and operating       | Legal info | rmation                    | . 87 |

|     | requirements81                             |            |                            |      |

# 1 Ratings

## 1.1 Thermal handling ratings

Table 4. Thermal handling ratings

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>-</b> 55 | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _           | 260  | °C   | 2     |

- 1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

- 2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 1.2 Moisture handling ratings

Table 5. Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

<sup>1.</sup> Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 1.3 ESD and Latch-Up Ratings

Table 6. ESD and Latch-Up Ratings

| Description                                                                                  | Rating           | Notes |

|----------------------------------------------------------------------------------------------|------------------|-------|

| Electrostatic discharge voltage, human body model                                            | ±2000 V          | 1     |

| Electrostatic discharge voltage, charged-device model (corner pins and antenna pin excluded) | ±500 V           | 2     |

| Electrostatic discharge voltage, charged-device model (corner pins)                          | ±750 V           |       |

| Electrostatic discharge voltage, charged-device model (antenna pin)                          | ±250 V           |       |

| Latch-up immunity level (Class II at 125 °C junction temperature)                            | Immunity Level A | 3     |

- 1. Determined according to JEDEC Standard JS-001-2017, For Electrostatic Discharge (ESD) Sensitivity Testing, Human Body Model (HBM) - Component Level.

- 2. Determined according to JEDEC Standard JS-002-2018, For Electrostatic Discharge (ESD) Sensitivity Testing, Charged-Device Model (CDM) - Device Level .

- 3. Determined according to JEDEC Standard JESD78F, IC Latch-Up Test.

# 1.4 Voltage and current maximum ratings

Table 7. Voltage and current maximum ratings

| Symbol   | Description                                   | Min. | Max.              | Unit |

|----------|-----------------------------------------------|------|-------------------|------|

| VDD_CORE | Supply voltage for most digital domains       | -0.3 | 1.26              | V    |

| VDD_SYS  | Supply voltage for PMC, EFUSE, SRTC, and FROs | -0.3 | 1.98 <sup>1</sup> | V    |

Table 7. Voltage and current maximum ratings (continued)

| Symbol           | Description                                                 | Min. | Max.              | Unit |

|------------------|-------------------------------------------------------------|------|-------------------|------|

| VDD_DCDC         | Supply voltage for DCDC regulator                           | -0.3 | 3.63              | V    |

| VDD_IO_D         | Supply voltage for LDO_SYS regulator, and PortD             | -0.3 | 3.63              | V    |

| VDD_LDO_C<br>ORE | Supply voltage for LDO_CORE regulator                       | -0.3 | 3.63              | V    |

| VDD_RF           | Supply voltage for OSC and radio analog                     | -0.3 | 3.6               | V    |

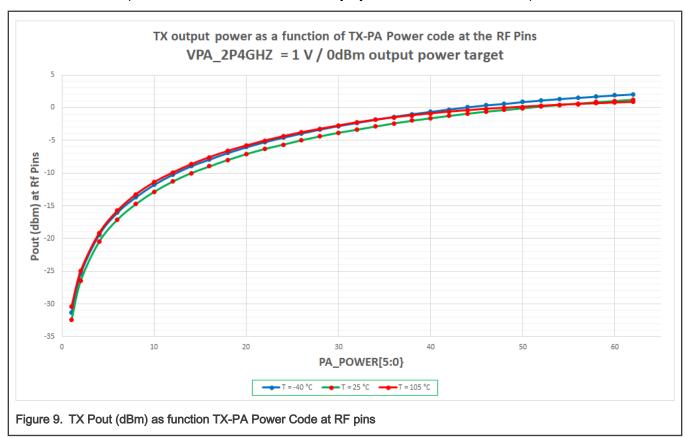

| VPA_2P4GH<br>Z   | Supply voltage for 2.4 GHz radio power amplifier            | -0.3 | 2.8               | V    |

| VDD_IO_ABC       | Supply voltage for Port A, Port B, Port C, Flash and CMP0/1 | -0.3 | 3.63              | V    |

| VDD_ANA          | Supply voltage for ADC, DAC, and VREF                       | -0.3 | 3.63              | V    |

| V <sub>IN</sub>  | Port input voltage                                          | -0.3 | 3.63 <sup>2</sup> | V    |

| I <sub>D</sub>   | Maximum current single pin limit (digital output pins)      | -25  | 25                | mA   |

<sup>1.</sup> The part supports 2.75 V for up to 20 s over lifetime to allow fuse programming

## 1.5 Required Power-On-Reset (POR) Sequencing

When VDD\_CORE is supplied by one of the internal regulators, VDD supply inputs can be powered up in any order. VDD supply inputs on power-up must not exceed VDD voltage maximums.

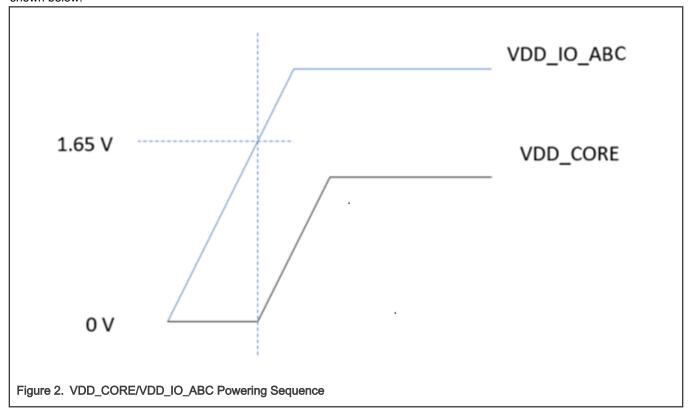

When powering VDD\_CORE with an external supply, VDD\_CORE must not be enabled until VDD\_IO\_ABC ≥ 1.65 V, as shown below.

<sup>2.</sup> The Max. of the  $V_{IN}$  cannot be greater than the voltage applied to the  $VDD_{L}IO_{L}x$ .

## 1.6 Power Sequence

Table 8. Power Sequence

| Symbol                | Description                             | Order in sequence | Notes |

|-----------------------|-----------------------------------------|-------------------|-------|

| VDD_SWITCH            | Smart Power Switch input                | 1                 | 1     |

| VDD_DCDC/<br>VDD_IO_D | DCDC / PORT D / LDO_SYS regulator input | 2                 | 1     |

| VDD_IO_ABC            | Ports A, B, and C power rail input      | 2                 | 1     |

| VDD_ANA               | Analog source input                     | 2                 | 1     |

| VDD_LDO_COR<br>E      | Core power rail input                   | 2                 | 1     |

| VDD_RF                | RF power rail input                     | 3                 | 1     |

| VPA_2P4GHz            | RF PA voltage input                     | 4                 | 1     |

<sup>1.</sup> All domains can be powered at the same time. If external sources are used, make sure they start at the same time or they follow the order in the sequence.

## 2 General

## 2.1 AC electrical characteristics

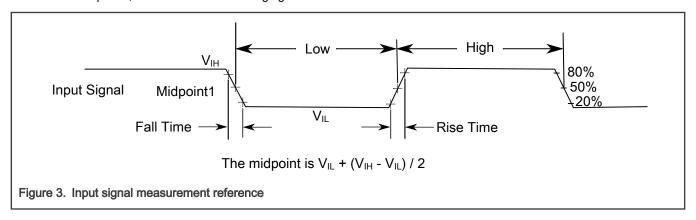

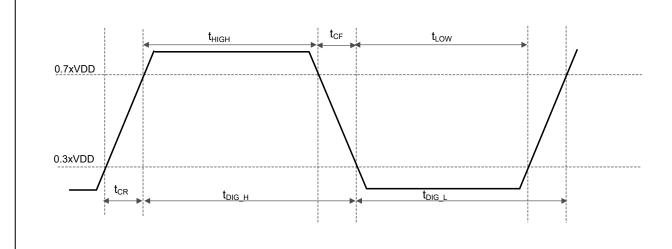

Unless specified, propagation delays are measured from the 50 % to the 50 % point, and rise and fall times are measured at the 20 % and 80 % points, as shown in the following figure.

## 2.2 Nonswitching electrical specifications

## 2.2.1 Voltage and current operating requirements

Table 9. Voltage and current operating requirements

| Symbol   | Description                   | Min. | Max. | Unit | Notes |

|----------|-------------------------------|------|------|------|-------|

| VDD_CORE | VDD_CORE input supply voltage |      |      | V    |       |

|          | Mid Drive (1.0 V) Operation   | 1.0  | 1.1  |      |       |

Table 9. Voltage and current operating requirements (continued)

| Symbol            | Description                                                                                                                                            | Min.                       | Max.                 | Unit | Notes |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|------|-------|

|                   | Normal Drive (1.1 V) Operation                                                                                                                         | 1.04                       | 1.21                 |      |       |

|                   | Safe-Mode Voltage (1.15 V) Operation                                                                                                                   | 1.04                       | 1.21                 |      |       |

| VDD_SYS           | Supply voltage for System Voltage Domain  Normal mode                                                                                                  | 1.8                        | 1.98                 | V    |       |

|                   | Fuse Programming                                                                                                                                       | 2.25                       | 2.75                 |      |       |

| VDD_DCDC          | Supply voltage DCDC regulator                                                                                                                          | 1.8                        | 3.6                  | V    | 1     |

| VDD_IO_D          | Supply voltage for LDO_SYS regulator, PortD                                                                                                            | 1.86                       | 3.6                  | V    | 2     |

| VDD_LDO_<br>CORE  | Supply voltage for LDO_CORE regulator                                                                                                                  | 1.25                       | 3.6                  | V    |       |

| VDD_RF            | Supply voltage for OSC and radio analog                                                                                                                | 1.175                      | 3.6                  | V    |       |

| VPA_2P4GH<br>z    | Supply voltage for 2.4 GHz radio power amplifier                                                                                                       | 0.9                        | 2.4                  | V    |       |

| VDD_IO_AB<br>C    | Supply voltage for PortA, PortB, Port C, and CMPs                                                                                                      | 1.71                       | 3.6                  | V    | 3     |

| VDD_ANA           | Supply voltage for ADC, DAC, and VREF                                                                                                                  | 1.71                       | 3.6                  | V    |       |

| VSS -<br>VSS_ANA  | VSS-to-VSS_ANA differential voltage                                                                                                                    | -0.1                       | 0.1                  | V    |       |

| V <sub>IH</sub>   | Input high voltage                                                                                                                                     |                            |                      |      | 4     |

|                   | • 1.71 V ≤ VDD_IO_ABC ≤ 3.6 V                                                                                                                          | 0.7 × VDD_I<br>O_ABC       | _                    | V    |       |

|                   | • 1.86 V ≤ VDD_IO_D ≤ 3.6 V                                                                                                                            | 0.7 × VDD_I<br>O_D         | _                    |      |       |

| V <sub>IL</sub>   | Input low voltage  • 1.71 V ≤ VDD_IO_ABC ≤ 3.6 V                                                                                                       | _                          | 0.3 × VDD_I<br>O_ABC | V    | 4     |

|                   | • 1.86 V ≤ VDD_IO_D ≤ 3.6 V                                                                                                                            | _                          | 0.3 × VDD_I<br>O_D   |      |       |

| V <sub>HYS</sub>  | Input hysteresis                                                                                                                                       | 0.1 × VDD_I<br>O_ <i>X</i> | _                    | V    |       |

| l <sub>ICIO</sub> | IO pin DC injection current — single pin                                                                                                               | 0                          | _                    | mA   | 5, 6  |

|                   | <ul> <li>V<sub>IN</sub> &lt; VSS – 0.3 V (negative current injection)</li> <li>V<sub>IN</sub> &gt; VDD + 0.3 V (positive current injection)</li> </ul> | _                          | 0                    |      |       |

| V <sub>ODPU</sub> | Open drain pullup voltage level                                                                                                                        | VDD_IO_X                   | VDD_IO_X             | V    | 7     |

- 1. If DCDC is unused, then input supply should be tied to GND through a 10  $k\Omega$  resistor.

- 2. When LDO\_SYS is bypassed, the input supply voltage is 1.8 V to 1.98 V and VDD\_IO\_D must be externally connected to VDD\_SYS

- 3. If none of the PortA, PortB, and PortC pins are being used, then the VDD\_IO\_ABC can be left floating.

- 4. VIH and VIL for PTD0 are based of VDD\_SYS instead of VDD\_IO\_D

- 5. All I/O pins are internally clamped to VSS and VDD\_IO\_x through an ESD protection diode. If V<sub>IN</sub> is greater than VDD\_IO\_x\_MIN(= VSS 0.3 V) or is less than VDD\_IO\_x\_MAX(= VDD + 0.3 V), then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed, then a current limiting resistor is required.

- 6. This device does not allow pin injection current. User must ensure that VIN is kept within the Voltage Maximum Ratings.

- 7. Open drain outputs must be pulled to whichever supply voltage corresponds to that IO, VDD\_IO\_X as appropriate.

## 2.2.2 HVD, LVD, and POR operating requirements

The device includes low-voltage detection (LVD) and high-voltage detection (HVD) power supervisor circuits for following power supplies:

- VDD\_IO\_ABC

- VDD\_CORE

- VDD\_SYS

For VDD\_SYS, it has Power-on-reset (POR) power supervisor circuits.

Table 10. VDD\_IO\_ABC supply HVD, LVD, and POR Operating Ratings

| Symbol                           | Description                                                          | Min.  | Тур.  | Max.  | Unit | Notes |

|----------------------------------|----------------------------------------------------------------------|-------|-------|-------|------|-------|

| V <sub>HVDH_IO_</sub> A<br>BC    | VDD_IO_ABC Rising high-voltage detect threshold                      | 3.730 | 3.810 | 3.890 | V    |       |

| V <sub>HVDH_HYS</sub>            | VDD_IO_ABC High-voltage inhibit reset/recover hysteresis             | _     | 38    | _     | mV   |       |

| V <sub>LVDH_IO_</sub> A<br>BC    | VDD_IO_ABC Falling low-voltage detect threshold - high range         | 2.567 | 2.619 | 2.673 | V    |       |

| V <sub>LVDH_HYS</sub><br>_IO_ABC | VDD_IO_ABC Low-voltage inhibit reset/recover hysteresis - high range | _     | 27    | _     | mV   |       |

| V <sub>LVDL_IO_</sub> A          | VDD_IO_ABC Falling low-voltage detect threshold - low range          | 1.618 | 1.651 | 1.684 | V    |       |

| V <sub>LVDV_HYS</sub>            | VDD_IO_ABC Low-voltage inhibit reset/recover hysteresis - low range  | _     | 20    | _     | mV   |       |

Table 11. VDD\_CORE supply HVD and LVD Operating Ratings

| Symbol                    | Description                                                   | Min.  | Тур.  | Max.  | Unit | Notes |

|---------------------------|---------------------------------------------------------------|-------|-------|-------|------|-------|

| V <sub>HVD_CORE</sub>     | VDD_CORE Rising high-voltage detect threshold (HVD assertion) |       |       |       | V    | 1     |

|                           | Target VDD_CORE = 1.05 V                                      |       |       |       |      |       |

|                           | Target VDD_CORE = 1.1 V                                       | 1.230 | 1.257 | 1.285 |      |       |

|                           | Target VDD_CORE = 1.15 V (safe mode LVD)                      |       |       |       |      |       |

| V <sub>HVD_HYS_CORE</sub> | VDD_CORE High-voltage inhibit reset/recover hysteresis        |       |       |       | mV   | 1     |

|                           | Target VDD_CORE = 1.05 V                                      | _     | 14    | 14 —  |      |       |

|                           | Target VDD_CORE = 1.1 V                                       |       |       |       |      |       |

|                           | Target VDD_CORE = 1.15 V (safe mode LVD)                      |       |       |       |      |       |

Table 11. VDD\_CORE supply HVD and LVD Operating Ratings (continued)

| Symbol                    | Description                                                                                                                                                | Min.                    | Тур.                    | Max.                    | Unit | Notes |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|------|-------|

| V <sub>LVD_</sub> CORE    | VDD_CORE Falling low-voltage detect threshold (LVD assertion)  Target VDD_CORE = 1.05 V  Target VDD_CORE = 1.1 V  Target VDD_CORE = 1.15 V (safe mode LVD) | 0.944<br>0.989<br>1.043 | 0.963<br>1.009<br>1.064 | 0.983<br>1.029<br>1.086 | V    |       |

| V <sub>LVD_HYS_CORE</sub> | VDD_CORE Low-voltage inhibit reset/ recover hysteresis  Target VDD_CORE = 1.05 V  Target VDD_CORE = 1.1 V  Target VDD_CORE = 1.15 V (safe mode LVD)        | _<br>_<br>_             | 14<br>14<br>17          | _<br>_<br>_             | mV   |       |

<sup>1.</sup> Same value applies to all conditions.

Table 12. VDD\_SYS supply HVD and LVD Operating Ratings

| Symbol                   | Description                                                  | Min.  | Тур.  | Max.  | Unit | Notes |

|--------------------------|--------------------------------------------------------------|-------|-------|-------|------|-------|

| V <sub>HVD_SYS</sub>     | VDD_SYS Rising high-voltage detect threshold (HVD assertion) |       |       |       | V    | 1     |

|                          | Target VDD_SYS = 1.8 V                                       | 2.035 | 2.077 | 2.120 |      |       |

|                          | Target VDD_SYS = 1.9 V (safe mode LVD)                       | 2.035 | 2.077 | 2.120 |      |       |

| V <sub>HVD_HYS_SYS</sub> | VDD_SYS High-voltage inhibit reset/recover hysteresis        | _     | 22    | _     | mV   |       |

| V <sub>POR_SYS</sub>     | Falling VDD_SYS POR detect voltage (POR assertion)           | 0.8   | 1.0   | 1.5   | V    |       |

| V <sub>LVD_SYS</sub>     | VDD_SYS Falling low-voltage detect threshold (LVD assertion) |       |       |       | V    |       |

|                          | Target VDD_SYS = 1.8 V                                       | 1.616 | 1.649 | 1.683 |      |       |

|                          | Target VDD_SYS = 1.9 V (safe mode LVD)                       | 1.700 | 1.735 | 1.770 |      |       |

| V <sub>LVD_HYS_SYS</sub> | VDD_SYS Low-voltage inhibit reset/recover hysteresis         | _     | 19    | _     | mV   |       |

| $V_{BG}$                 | Bandgap voltage reference voltage                            | _     | 1.0   | _     | V    |       |

<sup>1.</sup> When fuses are being programmed VDD\_SYS is raised to 2.5 V nominal. This is outside the HVD bounds, so HVD detection for VDD\_SYS must be disabled when programming fuses

## 2.2.3 Voltage and current operating behaviors

Table 13. Voltage and current operating behaviors

| Symbol          | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------------------------------|------|------|------|------|-------|

| V <sub>OH</sub> | Output high voltage — Normal drive strength |      |      |      |      | 1     |

Table 13. Voltage and current operating behaviors (continued)

| Symbol                | Description                                                                                                                                                                                                     | Min.                      | Тур. | Max.  | Unit | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-------|------|-------|

|                       | <ul> <li>2.7 V ≤ VDD_IO_X ≤ 3.6 V, I<sub>OH</sub> = 4 mA</li> <li>1.71 V ≤ VDD_IO_ABC &lt; 2.7 V, I<sub>OH</sub> = 2.5 mA</li> <li>1.86 V ≤ VDD_IO_D &lt; 2.7 V, I<sub>OH</sub> = 2.5 mA</li> </ul>             | VDD_IO_ <i>X</i><br>- 0.5 | _    | _     | V    |       |

| V <sub>OH</sub>       | Output high voltage — High drive strength  • 2.7 V ≤ VDD_IO_X ≤ 3.6 V, I <sub>OH</sub> = 6 mA  • 1.71 V ≤ VDD_IO_ABC < 2.7 V, I <sub>OH</sub> = 3.75 mA  • 1.86 V ≤ VDD_IO_D < 2.7 V, I <sub>OH</sub> = 3.75 mA | VDD_IO_X<br>- 0.5         | _    | _     | V    | 1,2   |

| I <sub>OHT</sub>      | Output high current total for all ports                                                                                                                                                                         | _                         | _    | 100   | mA   |       |

| V <sub>OL</sub>       | Output low voltage — Normal drive strength  • 2.7 V ≤ VDD_IO_X ≤ 3.6 V, I <sub>OL</sub> = 4 mA  • 1.71 V ≤ VDD_IO_ABC < 2.7 V, I <sub>OL</sub> = 2.5 mA  • 1.86 V ≤ VDD_IO_D < 2.7 V, I <sub>OH</sub> = 2.5 mA  | _                         | _    | 0.5   | V    | 1,3   |

| V <sub>OL</sub>       | Output low voltage — High drive strength  • 2.7 V ≤ VDD_IO_X ≤ 3.6 V, I <sub>OL</sub> = 6 mA  • 1.71 V ≤ VDD_IO_ABC < 2.7 V, I <sub>OL</sub> = 3.75 mA  • 1.86 V ≤ VDD_IO_D < 2.7 V, I <sub>OL</sub> = 3.75 mA  | _                         | _    | 0.5   | V    | 1,3,2 |

| I <sub>OLT</sub>      | Output low current total for all ports                                                                                                                                                                          | _                         | _    | 100   | mA   |       |

| I <sub>IN</sub>       | Input leakage current (per pin) for full temperature range                                                                                                                                                      | _                         | _    | 1     | μA   | 4     |

| I <sub>IN</sub>       | Input leakage current (per pin) at 25 °C                                                                                                                                                                        | _                         | _    | 0.025 | μA   | 4     |

| I <sub>IN</sub>       | Input leakage current (total all pins) for full temperature range                                                                                                                                               | _                         | _    | 41    | μА   | 4     |

| I <sub>OZ</sub>       | Hi-Z (off-state) leakage current (per pin)                                                                                                                                                                      | _                         | _    | 1     | μΑ   |       |

| R <sub>PU</sub>       | Internal pullup resistors                                                                                                                                                                                       | 33                        | 50   | 75    | kΩ   |       |

| R <sub>PU</sub> (I3C) | Internal pullup resistors                                                                                                                                                                                       | 1.1                       | 2    | 2.833 | kΩ   | 5     |

| R <sub>PD</sub>       | Internal pulldown resistors                                                                                                                                                                                     | 33                        | 50   | 75    | kΩ   |       |

| R <sub>HPU</sub>      | High-resistance pullup option (PORTx_PCRy[PV] = 1)                                                                                                                                                              | 0.67                      | _    | 1.5   | ΜΩ   | 6     |

| R <sub>HPD</sub>      | High-resistance pulldown option (PORTx_PCRy[PV] = 1)                                                                                                                                                            | 0.67                      | _    | 1.5   | ΜΩ   | 6     |

- 1. When setting DSE1=1, the same VOH / VOL is met with IOH / IOL doubled.

- 2. RTC signals are always configured in high drive mode

- 3. Open drain outputs must be pulled to VDD\_IO\_X.

- 4. Measured at  $VDD_IO_X = 3.6 \text{ V}$ .

- 5. Only I3C pins support this option

- 6. Only Port D pins support this option.

## 2.2.4 On-chip regulator electrical specifications

#### 2.2.4.1 DCDC converter specifications

Table 14. DCDC Converter Specifications

| Symbol                 | Description                                                          | Min. | Тур.    | Max.   | Unit    | Notes |

|------------------------|----------------------------------------------------------------------|------|---------|--------|---------|-------|

| V <sub>DD_DCDC</sub>   | DCDC input voltage                                                   | 1.71 | _       | 3.6    | V       |       |

| V <sub>OUT_DCDC</sub>  | DCDC output voltage                                                  | 1.25 | _       | 2.5    | V       | 1, 2  |

| I <sub>LOAD</sub>      | DCDC load current                                                    |      |         |        |         | 1, 3  |

|                        | Normal drive strength                                                | _    | _       | 105    | mA      |       |

|                        | Low drive strength                                                   | _    | _       | 15     | mA      |       |

|                        | SPC_DCD_CFG[FREQ_CNTRL_ON]=1                                         | _    | _       | 45     | mA      |       |

| LX                     | DCDC inductor value                                                  | 0.47 | 1       | 2.2    | μH      | 4     |

| ESR                    | External inductor equivalent series resistance                       | _    | 110     | _      | mΩ      | 5     |

| C <sub>OUT</sub>       | DCDC capacitance value                                               | 6    | 22      | 30     | μF      | 6     |

| V <sub>RIPPLE</sub>    | DCDC voltage ripple  In normal drive strength  In low drive strength |      | 1<br>25 | _<br>_ | %<br>mV |       |

| f <sub>burst</sub>     | DCDC burst frequency                                                 | 3    | 5       | 8      | MHz     | 7     |

| f <sub>burst_acc</sub> | DCDC burst frequency accuracy                                        | _    | 10      | _      | %       | 7     |

- The system DCDC converter generates 1.8 V at DCDC\_LX by default. The DCDC can be used to power VDD\_RF, VDD\_LDO\_CORE, and external components as long as the max I<sub>LOAD</sub> is not exceeded.

- 2. The VDD\_DCDC input supply to DCDC must be at least 500 mV higher than the desired output at DCDC\_LX.

- 3. The maximum load current during boot up shall not exceed 60 mA.

- 4. Recommended inductor value is 1 μH to 1.5 μH. If the inductor is < 1 μH, the DCDC efficiency is not guaranteed

- 5. The maximum recommended ESR is 250 m $\Omega$  (not a hard limit).

- 6. The variation in capacitance of the capacitor at DCDC\_LX due to aging, temperature, and voltage degradation must not exceed the Min./Max. values.

- 7. FREQ\_CNTRL\_ON = 1.

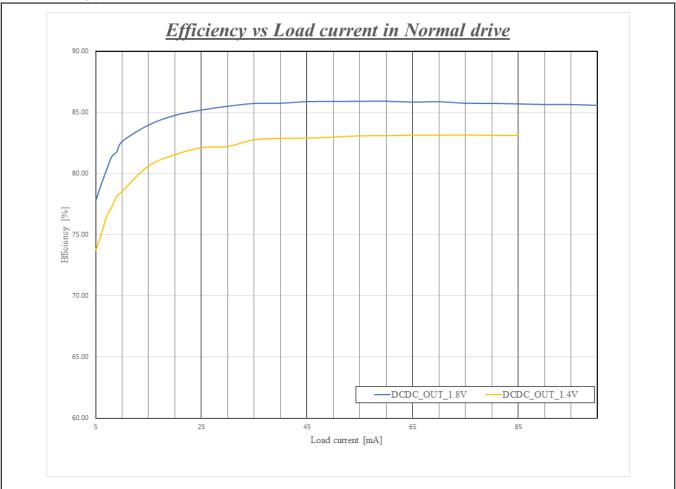

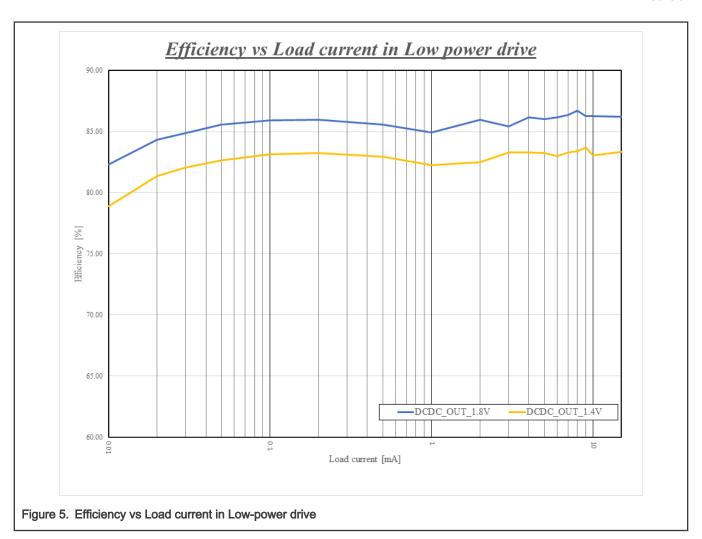

# DCDC Efficiency plots

Figure 4. Efficiency vs Load current in Normal drive

## 2.2.4.2 LDO\_SYS electrical specifications

Table 15. LDO\_SYS electrical specifications

| Symbol            | Description                                       | Min. | Тур. | Max. | Unit | Notes   |

|-------------------|---------------------------------------------------|------|------|------|------|---------|

| VDD_IO_D          | LDO_SYS input supply voltage                      |      |      |      | V    | 1       |

|                   | LDO_SYS input supply voltage<br>(Regulation mode) | 1.86 | _    | 3.6  |      |         |

|                   | LDO_SYS input supply voltage (Bypass mode)        | 1.8  | _    | 1.98 |      |         |

|                   | Fuse programming mode                             | 2.75 | _    | 3.6  |      |         |

| VOUT_SYS          | LDO_SYS regulator output voltage                  |      |      |      | V    | 2,3,4,5 |

|                   | Normal drive mode                                 | 1.71 | 1.8  | 1.98 |      |         |

|                   | Fuse Programming mode                             | 2.25 | 2.5  | 2.75 |      |         |

| I <sub>LOAD</sub> | LDO_SYS maximum load current                      |      |      |      |      |         |

Table 15. LDO\_SYS electrical specifications (continued)

| Symbol              | Description                                            | Min. | Тур. | Max. | Unit | Notes |

|---------------------|--------------------------------------------------------|------|------|------|------|-------|

|                     | Normal drive mode                                      | _    | _    | 50   | mA   |       |

|                     | Low drive mode                                         | _    | _    | 2    | mA   |       |

|                     | Fuse programming mode                                  | _    | _    | 40   | mA   |       |

| I <sub>DD</sub>     | LDO_SYS power consumption                              |      |      |      |      | 6     |

|                     | Normal drive mode                                      | _    | 100  | _    | μA   |       |

|                     | Low drive mode                                         | _    | 70   | _    | nA   |       |

| C <sub>OUT</sub>    | External output capacitor                              | _    | 1.5  | 10   | μF   |       |

| C <sub>DEC</sub>    | External output decoupling capacitor                   | _    | 0.1  | _    | μF   |       |

| ESR                 | External output capacitor equivalent series resistance | _    | 30   | _    | mΩ   |       |

| I <sub>INRUSH</sub> | LDO_SYS inrush current                                 | _    | _    | 120  | mA   | 7     |

- 1. Regulator will automatically switch to passthrough (means the regulator driver is fully ON) with the supply is below 1.95 V.

- 2. The LDO\_SYS converter generates 1.8 V by default at VOUT\_SYS. VOUT\_SYS can be used to power VDD\_SYS, VDD\_RF, VDD\_IO\_X, VDD\_ANA, and external components as long as the max I<sub>LOAD</sub> is not exceeded.

- 3. VOUT\_SYS and VDD\_SYS are connected together.

- 4. VDD\_IO\_D must be at least 150 mV higher than the desired VOUT\_SYS.

- 5. LDO SYS can be used to program efuse and in this configuration the output voltage can range between 2.25 V and 2.75 V

- 6. In normal drive strength, LDO\_SYS draws ~100 μA for every 20 mA of load current.

- 7. This is for 1.5 µF external output capacitor. If the capacitor has 10 µF value, this value should be 300 mA instead.

## 2.2.4.3 LDO\_CORE electrical specifications

Table 16. LDO\_CORE electrical specifications

| Symbol            | Description                                                | Min. | Тур. | Max. | Unit | Notes |

|-------------------|------------------------------------------------------------|------|------|------|------|-------|

| VDD_LDO_CO<br>RE  | LDO_CORE input supply voltage                              | 1.25 | _    | 3.6  | V    | 1, 2  |

| VOUT_CORE         | LDO_CORE regulator output voltage  • Normal drive strength | 1.0  | _    | 1.15 | V    |       |

|                   | Low drive strength                                         | 1.0  | _    | 1.15 |      |       |

| I <sub>LOAD</sub> | LDO_CORE max load current                                  |      |      |      |      |       |

|                   | Normal mode - VDD_LDO_CORE ≥     1.5 V                     | _    | _    | 60   | mA   |       |

|                   | Normal mode - VDD_LDO_CORE <     1.5 V                     | _    | _    | 30   |      |       |

|                   | • Low-power mode - VDD_LDO_CORE ≥ 1.5 V                    | _    | _    | 5    |      |       |

|                   | Low-power mode - VDD_LDO_CORE <     1.5 V                  | _    | _    | 5    |      |       |

Table 16. LDO\_CORE electrical specifications (continued)

| Symbol              | Description                                      | Min. | Тур. | Max.                  | Unit | Notes |

|---------------------|--------------------------------------------------|------|------|-----------------------|------|-------|

| I <sub>DD</sub>     | LDO_CORE current consumption                     |      |      |                       | μA   | 3     |

|                     | Normal drive strength -     VDD_LDO_CORE ≥ 1.5 V | _    | _    | 150                   | F    |       |

|                     | Normal drive strength -     VDD_LDO_CORE < 1.5 V | _    | _    | 75                    |      |       |

|                     | • Low drive strength - VDD_LDO_CORE ≥ 1.5 V      | _    | _    | 0.05                  |      |       |

|                     | Low drive strength - VDD_LDO_CORE <     1.5 V    | _    | _    | 0.05                  |      |       |

| I <sub>INRUSH</sub> | LDO_CORE inrush current                          | _    | _    | 5 x I <sub>LOAD</sub> | mA   |       |

- 1. To bypass LDO\_CORE, tie VDD\_LDO\_CORE to VDD\_CORE

- 2. The VDD\_LDO\_CORE input supply must also be at least 250 mV higher than the desired output at VOUT\_CORE.

- 3. In normal drive strength, LDO\_CORE draws ~40  $\mu$ A for every 20 mA of load current. In low drive strength, LDO\_CORE draws ~50 nA for every 100  $\mu$ A of load current.

Table 17. LDO\_CORE external device electrical specifications

| Symbol           | Description                                            | Min. | Тур. | Max. | Unit | Notes |

|------------------|--------------------------------------------------------|------|------|------|------|-------|

| C <sub>OUT</sub> | DUT External output capacitor                          |      | 4.7  | 10   | μF   |       |

| C <sub>DEC</sub> | External output decoupling capacitor                   | _    | 0.1  | _    | μF   |       |

| ESR              | External output capacitor equivalent series resistance | _    | 10   | _    | mΩ   |       |

## 2.2.5 Smart power switch

NOTE

SWITCH\_WAKEUP\_B pad is internally pulled up to the switch input through a resistor, it can be pulled down to

wake up the smart power switch. To generate a valid internal wake-up signal successfully, maximum value of SWITCH\_WAKEUP\_B pulldown voltage is 0.7 V, duration time should be larger than 1 μs.

Table 18. Smart power switch

| Symbol                | Description                                         | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------------|------|------|------|------|-------|

| V <sub>supply</sub>   | Input voltage (VDD_SWITCH)                          | 1.9  | _    | 3.6  | V    |       |

| R <sub>ON</sub>       | Switch resistor at 'on' state                       | _    | _    | 3    | Ω    |       |

| I <sub>load</sub>     | Load current                                        | _    | _    | 40   | mA   |       |

| I <sub>leakage1</sub> | Typical leakage current when Vsupply = 2.7 V, 25 °C |      | 4    | _    | nA   |       |

| I <sub>leakage2</sub> | Maximum leakage current when Vsupply = 3.3 V        | _    | _    | 1    | μΑ   |       |

#### NOTE

If battery (with peak current limitation) is used to power VDD\_SWITCH which power rest of chip supplies, it is not recommended to go to deep-power-down mode constantly. Because DCDC startup will introduce big peak current when wakeup.

## 2.2.6 Power mode transition operating behaviors

All specifications in the following table assume that the default clock configuration will be 96 MHz CPU\_CLK/BUS\_CLK and 24 MHz slow clock.

Table 19. Power mode transition operating behaviors

| Symbol              | Description              | Min.   | Тур.   | Max.   | Unit | Notes |

|---------------------|--------------------------|--------|--------|--------|------|-------|

| t <sub>SLEEP</sub>  | SLEEP → ACTIVE           | _      | 8.95   | 9.4    | μs   |       |

| t <sub>DSLEEP</sub> | DEEP SLEEP → ACTIVE      | _      | 9.6    | 10.1   | μs   |       |

| t <sub>PWDN</sub>   | POWER DOWN → ACTIVE      | 233.86 | 234.33 | 234.59 | μs   |       |

| t <sub>DPWDN</sub>  | Deep Power DOWN → ACTIVE | 747.59 | 816.12 | 835.00 | μs   |       |

## 2.2.7 Power consumption operating behaviors

The K32W device has multiple power supplies that can be connected in different configurations, where the total current consumption of the device is the accumulative result of each individual power supply's current consumption. All current consumption specifications are measured with a bench power supply that provides externally the different voltage levels required by each power domain in the corresponding KW45 power mode configuration.

When calculating the total MCU current consumption, the following considerations should be made:

- · Specifications below only include power for the MCU itself

- · On top of the device's IDD current consumption, external loads applied to pins of the device need to be considered

- · Efficiency of regulators (on-chip or off-chip) used to generate supply voltages should be considered

The maximum values stated in the following sections represent characterized results equivalent to the mean plus three times the standard deviation (mean + 6 sigma).

#### 2.2.7.1 Power Consumption Operating Behaviors

Table 20. Power Consumption Operating Behaviors

|                                                                                                                    | DCDC Power Configuration |                                 |       |     |     |      |       |  |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------|-------|-----|-----|------|-------|--|--|

| Mode#                                                                                                              | Symbol                   | Description                     | Temp  | Тур | Max | Unit | Notes |  |  |

| IDD_ACT IDD_ACT1                                                                                                   |                          | –40 °C                          | 4.9   | _   | mA  | 1,2  |       |  |  |

| 8                                                                                                                  |                          | current - DCDC in low strength, | 25 °C | 5.1 | _   |      |       |  |  |

|                                                                                                                    | Core voltage = 1.0       | 85 °C                           | 5.4   | _   |     |      |       |  |  |

| V, all peripherals<br>disabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 48 MHz<br>and NBU at 32 MHz | 105 °C                   | 5.8                             | -     |     |     |      |       |  |  |

Table 20. Power Consumption Operating Behaviors (continued)

| IDD_ACT<br>15 | IDD_ACT2 | Active 2 mode<br>current - DCDC<br>in normal strength,<br>Core voltage = 1.1<br>V, all peripherals<br>enabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 48 MHz<br>and NBU at 32 MHz  | 25 °C  | 5.5 | _ |    | 2,3 |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---|----|-----|

| IDD_ACT<br>16 | IDD_ACT3 | Active 3 mode<br>current - DCDC<br>in normal strength,<br>Core voltage = 1.1<br>V, all peripherals<br>enabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 48 MHz<br>and NBU at 32 MHz  | 25 °C  | 8.8 | _ |    | 2,3 |

| IDD_ACT<br>17 | IDD_ACT4 | Active 4 mode<br>current - DCDC<br>in normal strength,<br>Core voltage = 1.1<br>V, all peripherals<br>disabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 96 MHz<br>and NBU at 32 MHz | 25 °C  | 5.4 | _ |    | 2,3 |

| IDD_CM        | IDD_CM1  | CoreMark 1 mode                                                                                                                                                                                    | –40 °C | 6.0 | _ | mA | 2,3 |

| 1             |          | current - DCDC in normal strength,                                                                                                                                                                 | 25 °C  | 6.2 | _ |    |     |

|               |          | Core voltage = 1.1                                                                                                                                                                                 | 85 °C  | 6.4 | _ |    |     |

|               |          | V, all peripherals disabled, executing CoreMark® code from FLASH in CM33 at 96MHz, NBU in sleep mode.                                                                                              | 105 °C | 7.7 | _ |    |     |

| IDD_CM<br>22  | IDD_CM2  | CoreMark 2 mode current - DCDC in low strength, Core voltage = 1.0 V, all peripherals disabled, executing CoreMark® code from FLASH in                                                             | 25 °C  | 4.6 | - |    | 1,2 |

Table 20. Power Consumption Operating Behaviors (continued)

|                              |                                                                                                    | CM33 at 48MHz,<br>NBU in sleep mode.                                                                                                           |        |      |     |      |       |

|------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----|------|-------|

| IDD_DS1                      | IDD_DS1                                                                                            | Deep Sleep 1                                                                                                                                   | –40 °C | 3.0  |     | μA   | 4     |

|                              |                                                                                                    | mode current - All regulators in                                                                                                               | 25 °C  | 2.8  | _   |      |       |

|                              |                                                                                                    | low-power mode,                                                                                                                                | 85 °C  | 12.5 | _   |      |       |

|                              |                                                                                                    | all RAM retained,<br>all peripherals,<br>NBU, and<br>EdgeLock disabled,<br>OSC32K enabled                                                      | 105 °C | 26.2 | -   |      |       |

| IDD_DS2                      | IDD_DS2                                                                                            | 1 ' '                                                                                                                                          | –40 °C | 2.9  | _   | μΑ   | 4     |

|                              |                                                                                                    | mode current - All regulators in low                                                                                                           | 25 °C  | 2.5  | -   |      |       |

|                              |                                                                                                    | power, 16 KB of                                                                                                                                | 85 °C  | 9.2  | -   |      |       |

| radi<br>all p<br>NBL<br>Locl | RAM retained, all radio RAM retained, all peripherals, NBU, and Edge Lock disabled, OSC32K enabled | 105 °C                                                                                                                                         | 18.4   | -    |     |      |       |

| IDD_PD2 IDD_P                | IDD_PD1                                                                                            | Power Down 1                                                                                                                                   | –40 °C | 3.8  | _   | μA   | 4     |

|                              |                                                                                                    | mode current - All regulators in low power, 16 KB of                                                                                           | 25 °C  | 3.4  | -   |      |       |

|                              |                                                                                                    |                                                                                                                                                | 85 °C  | 9.8  | _   |      |       |

|                              |                                                                                                    | RAM retained, all<br>radio RAM retained,<br>all peripherals,<br>NBU, and Edge<br>Lock disabled,<br>FRO32K enabled                              | 105 °C | 18.3 | -   |      |       |

| IDD_DP                       | IDD_DPD1                                                                                           | Deep Power Down                                                                                                                                | –40 °C | 1.70 | _   | μA   | 4     |

| D2                           |                                                                                                    | 1 mode current - LDO_CORE                                                                                                                      | 25 °C  | 1.2  | _   |      |       |

|                              |                                                                                                    | and DCDC off,                                                                                                                                  | 85 °C  | 3.7  | -   |      |       |

|                              |                                                                                                    | LDO_SYS in low<br>power, no RAM<br>retained, no radio<br>RAM retained,<br>all peripherals,<br>NBU, and<br>EdgeLock disabled,<br>FRO32K enabled | 105 °C | 7.2  | -   |      |       |

|                              | PMIC Power                                                                                         | Configuration                                                                                                                                  |        |      |     |      |       |

| Mode                         | Symbol                                                                                             | Description                                                                                                                                    | Temp   | Тур  | Max | Unit | Notes |

| IDD_ACT                      | IDD_ACT5                                                                                           | Active 5 mode                                                                                                                                  | –40 °C | 6.9  | -   | mA   | 2,5   |

| 14                           |                                                                                                    | Current - Core                                                                                                                                 | 25 °C  | 7.0  | _   |      |       |

Table 20. Power Consumption Operating Behaviors (continued)

|               |          | voltage = 1.0                                                                                                                                                          | 85 °C  | 7.7  | _ |    |      |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---|----|------|

|               |          | V, all peripherals<br>disabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 48 MHz<br>and NBU at 32 MHz                                                     | 105 °C | 8.4  | - |    |      |

| IDD_ACT<br>18 | IDD_ACT6 | Active 6 mode<br>current - Core<br>voltage = 1.1 V, all<br>peripherals enabled,<br>executing while(1)<br>from FLASH in both<br>CM33 at 48 MHz<br>and NBU at 32 MHz     | 25 °C  | 10   | - | mA | 2, 6 |

| IDD_ACT<br>19 | IDD_ACT7 | Active 7 mode<br>current - Core<br>voltage = 1.1 V, all<br>peripherals enabled,<br>executing while(1)<br>from FLASH in both<br>CM33 at 96 MHz<br>and NBU at 32 MHz     | 25 °C  | 17   | - | mA | 2,6  |

| IDD_ACT<br>20 | IDD_ACT8 | Active 8 mode<br>current - Core<br>voltage = 1.1<br>V, all peripherals<br>disabled, executing<br>while(1) from<br>FLASH in both<br>CM33 at 96 MHz<br>and NBU at 32 MHz | 25 °C  | 9.9  | _ | mA | 2,6  |

| IDD_CM        | IDD_CM3  | CoreMark 3 mode                                                                                                                                                        | –40 °C | 10.7 | _ | mA | 2,6  |

| 13            |          | current - Core<br>voltage = 1.1                                                                                                                                        | 25 °C  | 10.8 | _ |    |      |

|               |          | V, all peripherals                                                                                                                                                     | 85 °C  | 11.9 | _ |    |      |

|               |          | disabled, executing CoreMark® code from FLASH in CM33 at 96 MHz, NBU in sleep mode.                                                                                    | 105 °C | 12.7 | - |    |      |

| IDD_CM<br>23  | IDD_CM4  | CoreMark 4 mode<br>current - Core<br>voltage = 1.0<br>V, all peripherals<br>disabled, executing<br>CoreMark® code<br>from FLASH in                                     | 25 °C  | 6.9  | _ | mA | 2,5  |

Table 20. Power Consumption Operating Behaviors (continued)

|         |               | CM33 at 48MHz,<br>NBU in sleep mode.                                                                            |        |      |     |      |       |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------|--------|------|-----|------|-------|

| IDD_DS5 | IDD_DS3       | DeepSleep 3 mode                                                                                                | –40 °C | 7.1  | -   | μΑ   | 5     |

|         |               | current - all<br>RAM retained,                                                                                  | 25 °C  | 5.4  | _   |      |       |

|         |               | all peripherals,                                                                                                | 85 °C  | 24.9 | _   |      |       |

|         |               | NBU, and<br>EdgeLock disabled,<br>OSC32K enabled                                                                | 105 °C | 53.2 | -   |      |       |

| DD_DS6  | IDD_DS4       | DeepSleep 4 mode                                                                                                | –40 °C | 5.4  | -   | μΑ   | 5     |

|         |               | current - 16 KB of<br>RAM retained, all                                                                         | 25 °C  | 4.5  | _   |      |       |

|         |               | radio RAM retained,                                                                                             | 85 °C  | 17.3 | _   |      |       |

|         |               | all peripherals, NBU, and Edge Lock disabled, OSC32K enabled                                                    |        | 34.9 | -   |      |       |

| IDD_PD6 | IDD_PD2       | PowerDown 2 mode                                                                                                | –40 °C | 12.0 | _   | μΑ   | 5     |

|         |               | current - 16 KB of RAM retained, all                                                                            | 25 °C  | 6.5  | _   |      |       |

|         |               |                                                                                                                 | 85 °C  | 18.9 | _   |      |       |

|         |               |                                                                                                                 | 105 °C | 34.8 | -   |      |       |

| IDD_DP  | IDD_DPD2      | DeepPowerDown 2                                                                                                 | –40 °C | 9.7  | _   | μA   | 5     |

| D4      |               | mode current - no<br>RAM retained, no                                                                           | 25 °C  | 2.9  | _   |      |       |

|         |               | radio RAM retained,                                                                                             | 85 °C  | 5.8  | _   |      |       |

|         |               | all peripherals, NBU, and EdgeLock disabled, FRO32K enabled                                                     | 105 °C | 9.5  | -   |      |       |

|         | Smart Power S | Switch                                                                                                          |        |      |     |      |       |

| Mode    | Symbol        | Description                                                                                                     | Temp   | Тур  | Max | Unit | Notes |

| DD_SW   | IDD_SW_DP     | Smart Power Switch                                                                                              | –40 °C | 0.3  | _   | μA   | 7,8   |

| _DPD2   | D1            | Deep Power Down 2 mode current - All                                                                            | 25 °C  | 0.4  | _   |      |       |

|         |               | regulators off, 8 KB                                                                                            | 85 °C  | 2.2  | _   |      |       |

|         |               | RAM retained, no<br>radio RAM retained,<br>all peripherals,<br>NBU, and<br>EdgeLock disabled,<br>FRO16K enabled | 105 °C | 3.3  | -   |      |       |

<sup>1.</sup> All regulators enabled, 3.3 V supply upstream from the DCDC. DCDC output is 1.8 V, VDD\_CORE =1.0. SYS\_LDO input=3.3, output = 1.8 V.

<sup>2.</sup> FRO-192M as clock source

- 3. All regulators enabled, 3.3 V supply upstream from the DCDC. DCDC output is 1.35V, VDD\_CORE =1.1. SYS\_LDO input=3.3, output = 1.8 V.

- 4. All regulators enabled, 3.3 V supply upstream from the DCDC. DCDC output is 1.25V, VDD\_CORE =1.0. SYS\_LDO input=3.3, output = 1.8V.

- All regulators are disabled. Voltages are come from external supplies. External 3.3V supply for VDD\_SWITCH, VDD\_ANA, VDD\_IO\_ABC and VDD\_IO\_D/DCDC\_IN. External 1.8V supply for VDD\_SYS and VDD\_RF. External 1.0V supply for VDD\_CORE.

- All regulators are disabled. Voltages are come from external supplies. External 3.3V supply for VDD\_SWITCH, VDD\_ANA, VDD\_IO\_ABC and VDD\_IO\_D/DCDC\_IN. External 1.8V supply for VDD\_SYS and VDD\_RF. External 1.1V supply for VDD\_CORE.

- 7. 8 KB of retained RAM correspond to the last RAM block and is powered by the standby LDO in smart power switch domain

- 8. External 3.3 V supply to Smart Power Switch. Power switch output connected to DCDC\_IN, LDO\_SYS, VDD\_ANA, VDD\_IO\_D and VDD\_IO\_ABC; DCDC output connected to LDO\_CORE, VDD\_RF

#### 2.2.7.2 SoC Power Consumption

SoC Power Consumption table is as follows:

Table 21. SoC POwer Consumption

| CM33         | Radio state  | DCDC state             | Typical Average IC current | Unit |

|--------------|--------------|------------------------|----------------------------|------|

| Deep Sleep 2 | Rx           | Buck (Vdcdc_in =3.3 V) | 6.6                        | mA   |

| Deep Sleep 2 | Rx (scan)    | Buck (Vdcdc_in =3.3 V) | 4.1                        | mA   |

| Deep Sleep 2 | Tx (+0 dBm)  | Buck (Vdcdc_in =3.3 V) | 5.2                        | mA   |

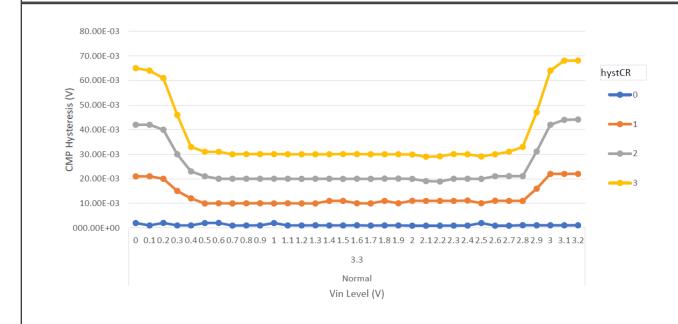

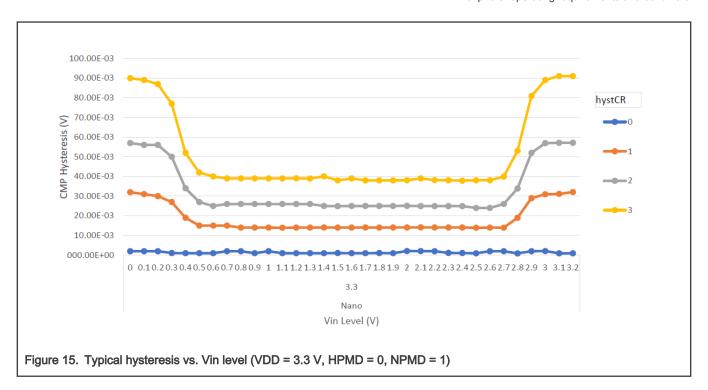

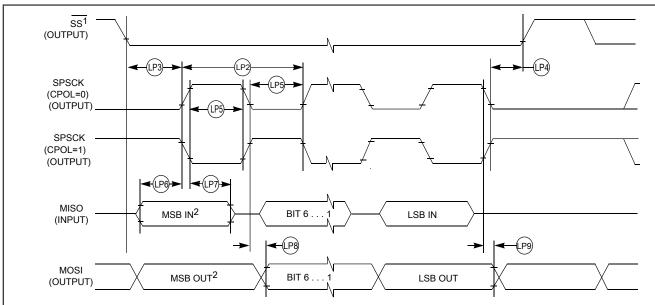

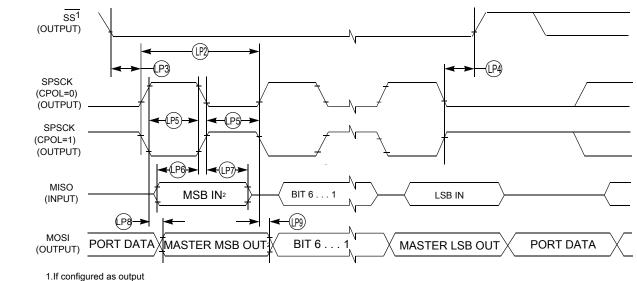

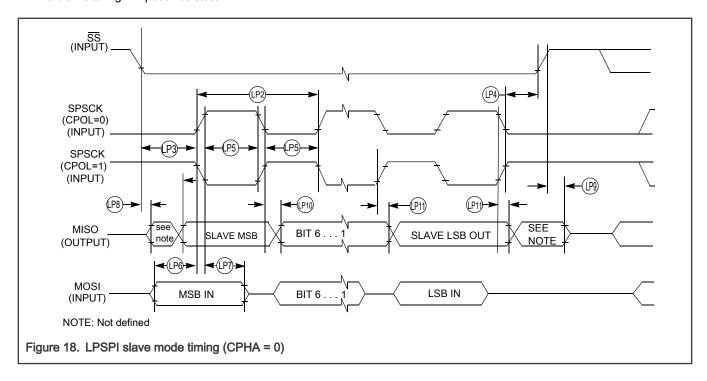

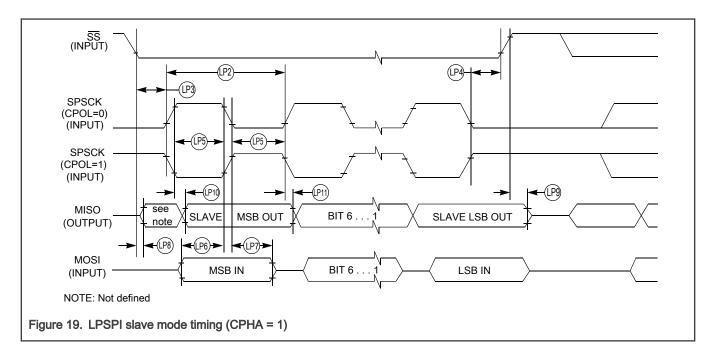

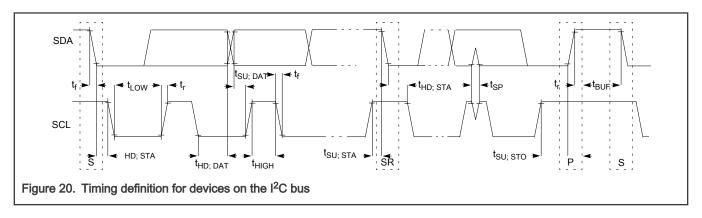

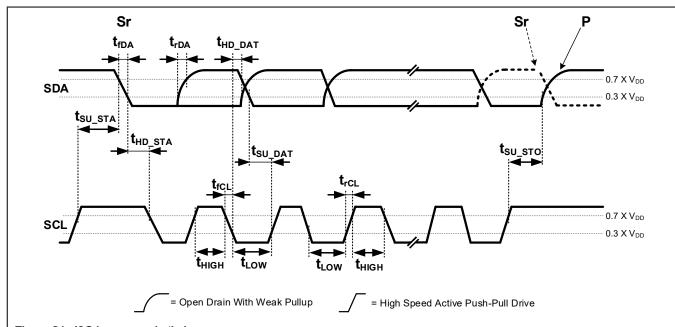

| Deep Sleep 2 | Tx (+4 dBm)  | Buck (Vdcdc_in =3.3 V) | 8.7                        | mA   |