# High Voltage Step-Down Controller With 40µA Quiescent Current

#### **FEATURES**

- Wide Input Range: 4V to 60V

- Current Mode Constant Frequency PWM

- Very Low Dropout Operation: 100% Duty Cycle

- Programmable Switching Frequency: 200kHz to 600kHz

- Selectable High Efficient Burst Mode® Operation: 40µA Quiescent Current

- Easy Synchronization

- 8V, 2A Gate Drive (V<sub>CC</sub> > 10V) for Industrial High Voltage P-Channel MOSFET

- Programmable Soft-Start

- Programmable Current Limit

- Available in a Small 10-Pin Thermally Enhanced MSE Package

## **APPLICATIONS**

- Industrial and Automotive Power Supplies

- Telecom Power Supplies

- Distributed Power Systems

#### DESCRIPTION

The LTC®3824 is a step-down DC/DC controller designed to drive an external P-channel MOSFET. With a wide input range of 4V to 60V and a high voltage gate driver, the LTC3824 is suitable for many industrial and automotive high power applications. Constant frequency current mode operation provides excellent performance.

The LTC3824 can be configured for Burst Mode operation. Burst Mode operation enhances low current efficiency (only  $40\mu A$  quiescent current) and extends battery run time. The switching frequency can be programmed up to 600kHz and is easily synchronizable.

Other features include current limit, soft-start, micropower shutdown, and Burst Mode disable.

The LTC3824 is available in a 10-lead MSE power package.

LT, LT, LTC, LTM and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5731964.

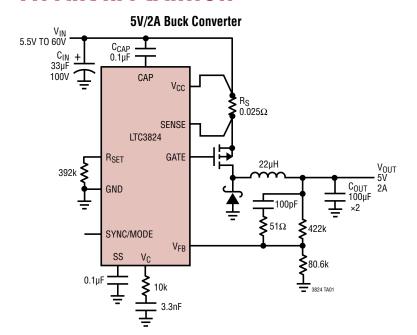

## TYPICAL APPLICATION

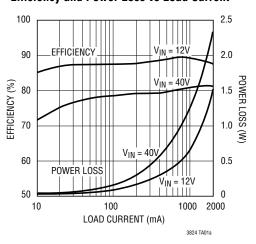

#### **Efficiency and Power Loss vs Load Current**

# **ABSOLUTE MAXIMUM RATINGS**

# (Note 1)

| (NOTE 1)                               |          |

|----------------------------------------|----------|

| V <sub>CC</sub>                        | 65V      |

| SS, R <sub>SFT</sub> , V <sub>FB</sub> | 4V       |

| V <sub>C</sub>                         | 3V       |

| SYNC/MODE                              | 6V       |

| V <sub>CC</sub> – V <sub>SFNSF</sub>   | 1V       |

| Operating Junction Temperature Range   |          |

| (Note 2)55°C                           | to 150°C |

| Storage Temperature Range65°           | to 150°C |

| Lead Temperature (Soldering, 10 sec)   | 300°C    |

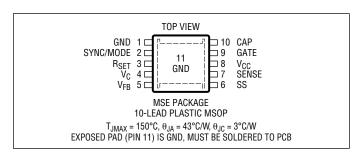

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|-------------------|--------------------|---------------|----------------------|-------------------|

| LTC3824EMSE#PBF   | LTC3824EMSE#TRPBF  | LTBRZ         | 10-Lead Plastic MSOP | -40°C to 125°C    |

| LTC3824IMSE#PBF   | LTC3824IMSE#TRPBF  | LTCGZ         | 10-Lead Plastic MSOP | -40°C to 125°C    |

| LTC3824HMSE#PBF   | LTC3824HMSE#TRPBF  | LTCGZ         | 10-Lead Plastic MSOP | -40°C to 150°C    |

| LTC3824MPMSE#PBF  | LTC3824MPMSE#TRPBF | LTCGZ         | 10-Lead Plastic MSOP | -55°C to 150°C    |

| LEAD BASED FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

| LTC3824EMSE       | LTC3824EMSE#TR     | LTBRZ         | 10-Lead Plastic MSOP | -40°C to 125°C    |

| LTC3824IMSE       | LTC3824IMSE#TR     | LTCGZ         | 10-Lead Plastic MSOP | -40°C to 125°C    |

| LTC3824HMSE       | LTC3824HMSE#TR     | LTCGZ         | 10-Lead Plastic MSOP | -40°C to 150°C    |

| LTC3824MPMSE      | LTC3824MPMSE#TR    | LTCGZ         | 10-Lead Plastic MSOP | -55°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{CC} = 12V$ ,  $R_{SET} = 392k$ ,  $C_{CAP} = 0.1 \mu F$ . No load on any outputs, unless otherwise specified.

| PARAMETER                                                      | CONDITIONS                                                                                         |   | MIN                     | TYP        | MAX                     | UNITS      |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---|-------------------------|------------|-------------------------|------------|

| Supply Voltage (V <sub>CC</sub> )                              |                                                                                                    | • | 4                       |            | 60                      | V          |

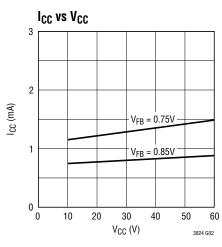

| Supply Current (I <sub>VCC</sub> )                             | $V_C \le 0.4V$ (Switching Off), $V_{CC} \le 60V$<br>$V_{SYNC} = 0V$ (Burst Mode Operation Disable) |   |                         | 0.8        | 1.3                     | mA         |

| Supply Current (I <sub>VCC</sub> ) Burst Mode Operation        | $V_{CC} \le 60V$ , SYNC/MODE Open, $V_C = 0.6V$                                                    |   |                         | 40         | 65                      | μА         |

| Supply Current in Shutdown                                     | $V_C \le 25 \text{mV}, V_{CC} \le 60 \text{V}$                                                     | • |                         | 9          | 20<br>30                | μA<br>μA   |

|                                                                | $V_C \le 25$ mV, $V_{CC} = 12$ V                                                                   | • |                         | 5          | 10<br>15                | μA<br>μA   |

| Voltage Amplifier gm                                           |                                                                                                    |   |                         |            |                         |            |

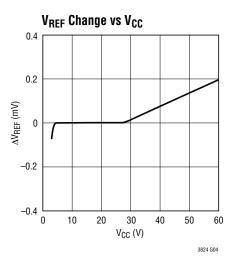

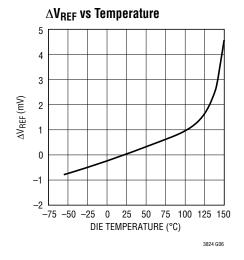

| Reference Voltage (V <sub>REF</sub> )                          | LTC3824E/LTC3824I<br>LTC3824MP/LTC3824H                                                            | • | 0.792<br>0.788<br>0.788 | 0.8        | 0.808<br>0.812<br>0.816 | V<br>V     |

| Transconductance                                               | $V_C = 0.8V$ , $\Delta I_{VC} = \pm 2\mu A$                                                        |   | 220                     | 260        | 370                     | μmho       |

| FB Input Current                                               | V <sub>FB</sub> = V <sub>REF</sub> (Note 3): LTC3824E/LTC3824I<br>LTC3824MP/LTC3824H               | • |                         | 10<br>10   | 30<br>60                | nA<br>nA   |

| V <sub>C</sub> High                                            | I <sub>VC</sub> = 0                                                                                |   |                         | 1.6        |                         | V          |

| V <sub>C</sub> Low                                             | I <sub>VC</sub> = 0                                                                                |   |                         | 0.35       | 0.5                     | V          |

| V <sub>C</sub> Source Current                                  | $V_{VC} = 0.5V \text{ to } 1.3V, V_{FB} = V_{REF} - 100 \text{mV} (V_{SYNC} = 0V)$                 |   |                         | 15         |                         | μA         |

| V <sub>C</sub> Sink Current                                    | $V_{VC} = 0.7V \text{ to } 1.3V, V_{FB} = V_{REF} + 100 \text{mV} (V_{SYNC} = 0V)$                 |   |                         | 15         |                         | μA         |

| V <sub>C</sub> Threshold for Switching Off                     | V <sub>SYNC/MODE</sub> = 0V (Note 4)                                                               | • |                         |            | 0.4                     | V          |

| Soft-Start Current I <sub>SS</sub>                             | V <sub>SS</sub> = 0.1V to 1.5V                                                                     | • | 3<br>2.5                | 5          | 7.5<br>8                | μA<br>μA   |

| V <sub>C</sub> Burst Mode Threshold                            | $V_{CC} \le 60V$ , $V_C$ Rising, SYNC/MODE Open                                                    |   |                         | 0.84       |                         | V          |

| V <sub>C</sub> Burst Mode Threshold Hysteresis                 | V <sub>CC</sub> ≤ 60V                                                                              |   |                         | 0.04       |                         | V          |

| SENSE Voltage at Burst Mode Operation                          | (V <sub>CC</sub> –V <sub>SENSE</sub> ) at 30% Duty Cycle<br>70% Duty Cycle                         |   |                         | 30<br>20   |                         | mV<br>mV   |

| Current Limit Threshold (V <sub>CC</sub> -V <sub>SENSE</sub> ) | $V_{CC} \le 60V$ : LTC3824E/LTC3824I LTC3824MP/LTC3824H                                            | • | 80<br>75                | 100<br>100 | 120<br>120              | mV<br>mV   |

| FB Overvoltage Threshold                                       | V <sub>C</sub> = 1.6V                                                                              |   |                         | 8          |                         | %          |

| Sense Input Current                                            | $V_{SENSE} = V_{CC}$                                                                               |   |                         | 0.1        | 2                       | μA         |

| Oscillator                                                     |                                                                                                    |   |                         |            |                         |            |

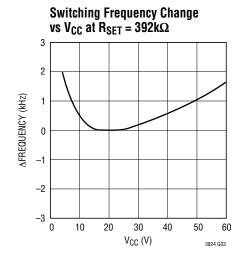

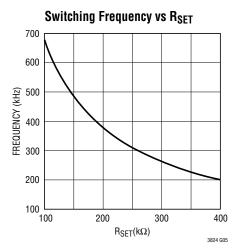

| Switching Frequency                                            | R <sub>SET</sub> = 392k: LTC3824E/LTC3824I<br>LTC3824MP/LTC3824H                                   | • | 170<br>170              | 200<br>200 | 230<br>240              | kHz<br>kHz |

|                                                                | R <sub>SET</sub> = 200k                                                                            | • | 320                     | 400        | 460                     | kHz        |

| Synchronization Pulse Threshold on SYNC Pin                    | Rising Edge V <sub>SYNC</sub>                                                                      |   |                         |            | 1.3                     | V          |

| Synchronization Frequency Range                                | R <sub>SET</sub> = 392k<br>R <sub>SET</sub> = 200k                                                 | • | 230<br>460              |            | 300<br>600              | kHz<br>kHz |

| V <sub>RSET</sub>                                              | R <sub>SET</sub> = 392k                                                                            |   |                         | 1.2        |                         | V          |

| Minimum On-Time (Measured at GATE Pin)                         | CCM Operation (Note 5)                                                                             |   |                         | 350        |                         | ns         |

| Switching Frequency Foldback                                   | V <sub>FB</sub> = 0.3V                                                                             | • | 35                      | 50         | 75                      | kHz        |

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25$ °C (Note 2). $V_{CC} = 12V$ , $R_{SET} = 392k$ , $C_{CAP} = 0.1 \mu F$ . No load on any outputs, unless otherwise specified.

| PARAMETER                                               | CONDITIONS                                                                               |   | MIN        | TYP         | MAX        | UNITS |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------|---|------------|-------------|------------|-------|--|

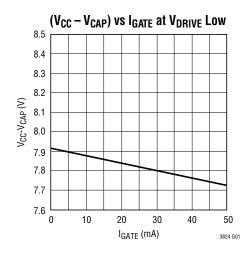

| Gate Driver                                             |                                                                                          |   |            |             |            |       |  |

| GATE Bias Voltage (V <sub>CC</sub> -V <sub>CAP</sub> )  | $9V \le V_{CC} \le 60V$ , $I_{GATE} = 10mA$ : LTC3824E/LTC3824I LTC3824MP/LTC3824H       | • | 7.0<br>6.8 | 7.9<br>7.9  | 8.8<br>8.9 | V     |  |

|                                                         | V <sub>CC</sub> = 12V, I <sub>GATE</sub> = 15mA                                          | • | 6.8        |             |            | V     |  |

| GATE Bias Voltage (V <sub>CAP</sub> -GND)               | $4V \le V_{CC} \le 8V$ , $I_{GATE} = 10mA$<br>$6V \le V_{CC} \le 8V$ , $I_{GATE} = 15mA$ | • | 0.2        | 0.85        | 1.5<br>2.8 | V     |  |

| GATE High Voltage (V <sub>CC</sub> -V <sub>GATE</sub> ) | 4V ≤ V <sub>CC</sub> ≤ 60V, I <sub>GATE</sub> = −15mA                                    |   |            | 0.5         | 0.8        | V     |  |

| GATE Peak Source Current                                | C <sub>GATE</sub> = 10nF                                                                 |   |            | 2.5         |            | А     |  |

| GATE Low Voltage (V <sub>GATE</sub> -V <sub>CAP</sub> ) | $8V \le V_{CC} \le 60V$ , $I_{GATE} = 15mA$<br>$4V \le V_{CC} < 8V$ , $I_{GATE} = 10mA$  |   |            | 0.1<br>0.05 | 0.5        | V     |  |

| GATE Peak Sink Current                                  | C <sub>GATE</sub> = 10nF                                                                 |   |            | 2.5         |            | А     |  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3824 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3824E is guaranteed to meet performance specifications from 0°C to 85°C operating junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design characterization and correlation with statistical process controls. The LTC3824I is guaranteed over the -40°C to 125°C operating junction temperature range. The LTC3824H is guaranteed over the -40°C to 150°C operating junction temperature range. The LTC3824MP is guaranteed and tested over the full -55°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board

layout, the rated package thermal impedance and other environmental factors. The junction temperature ( $T_J$ , in °C) is calculated from the ambient temperature ( $T_A$ , in °C) and power dissipation ( $P_D$ , in Watts) according to the formula:

$$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D} \bullet \theta_\mathsf{JA})$$

where  $\theta_{\text{JA}}$  (in °C/W) is the package junction to ambient thermal impedance.

**Note 3:** This parameter is tested in a feedback loop that servos  $V_{FB}$  to the reference voltage with the  $V_{C}$  pin forced to 1V.

**Note 4:** This specification represents the maximum voltage on  $V_C$  where switching (GATE pin) is guaranteed to be off. The nominal value of  $V_C$  where switching turns off is 0.7V.

**Note 5:** The LTC3824 typically enters Burst Mode operation when the load is less than one third the current limit. If minimum on-time is violated, cycle skipping may occur at higher current levels.

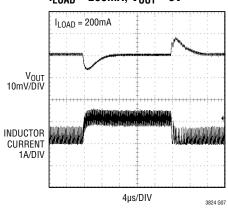

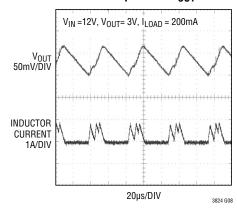

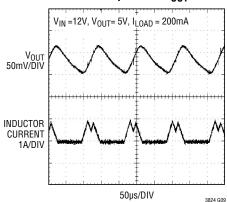

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C unless otherwise noted.

Burst Mode Disabled at  $I_{LOAD} = 200$ mA,  $V_{OUT} = 5V$

#### Burst Mode Operation $V_{OUT} = 3V$

## Burst Mode Operation $V_{OUT} = 5V$

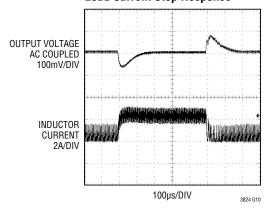

#### **Load Current Step Response**

## PIN FUNCTIONS

**GND (Pin 1, Exposed Pad Pin 11):** Ground. Exposed pad must be soldered to PCB with expanded metal trace for rated thermal performance.

**SYNC/MODE (Pin 2):** Synchronization Input and Burst Mode Operation Enable/Disable. If this pin is left open or pulled higher than 2V, Burst Mode operation will be enabled at light load and the typical threshold of entering Burst Mode operation is one third of current limit. If this pin is grounded or the synchronization pulse is present with a frequency greater than 20kHz then Burst Mode operation is disabled and the LTC3824 goes into pulse skipping at light loads. To synchronize the LTC3824, the duty cycle of the synchronizing pulse can range from 10% to 70% and the synchronizing frequency has to be higher than the programmed frequency.

$R_{SET}$  (Pin 3): A resistor from  $R_{SET}$  to ground sets the LTC3824 switching frequency.

$V_C$  (Pin 4): The Output of the voltage error amplifier gm and the control signal of the current mode PWM control loop. Switching starts at 0.7V, and higher  $V_C$  corresponds to higher inductor current. When  $V_C$  is pulled below 25mV, the LTC3824 goes into micropower shutdown.

$V_{FB}$  (Pin 5): Error Amplifier Inverting Input. A resistor divider to this pin sets the output voltage. When  $V_{FB}$  is less than 0.5V, the switching frequency will fold back to 50kHz to reduce the minimum on-cycle.

**SS** (Pin 6): Soft-Start Pin. A capacitor on this pin sets the output ramp-up rate. The typical time for SS to reach the programmed level is  $(C \cdot 0.8V)/5\mu A$ . Connect a  $1M\Omega$  to  $10M\Omega$  resistor from SS to ground to reset the soft-start capacitor if shutdown mode is used.

**SENSE (Pin 7):** Current Sense Input Pin. A sense resistor,  $R_S$ , from  $V_{IN}$  to SENSE sets the current limit to  $100mV/R_S$ .

**V<sub>CC</sub> (Pin 8):** Chip Power Supply. Power supply bypassing is required.

**GATE (Pin 9):** Gate Drive for The External P-channel MOSFET. Typical peak drive current is 2.5A and the drive voltage is clamped to 8V when  $V_{CC}$  is higher than 9V.

**CAP (Pin 10):** A Low ESR Capacitor of at Least  $0.1\mu F$  is required from this pin to  $V_{CC}$  to bypass the internal regulator for biasing the gate driver circuitry.

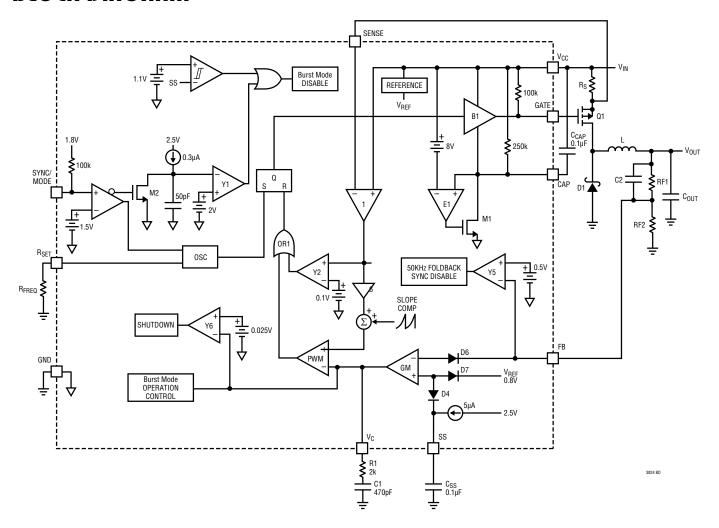

## **BLOCK DIAGRAM**

# **APPLICATIONS INFORMATION**

#### Operation

The LTC3824 is a constant frequency current mode buck controller with programmable switching frequency up to 600kHz.

Referring to the Block Diagram, the LTC3824's basic functions include a transconductance amplifier gm to regulate the output voltage and control the current mode PWM current loop, the necessary logic to control the PWM switching cycles, a high speed gate driver to drive an external high power P-channel MOSFET and a voltage regulator to bias the gate driver circuit.

In normal operation each switching cycle starts with switch turn-on and the inductor current is sampled through the current sense resistor. This current is amplified and then compared to the error amplifier output  $V_{C}$  to turn the switch off. Voltage loop regulates the output voltage to the programmed level through the output resistor divider and the error amplifier. Amplifier E1 regulates the gate drive low to approximately 8V below  $V_{CC}$  for  $V_{CC}$  higher than 9V, and  $C_{CAP}$  stabilizes the voltage. Note that when  $V_{CC}$  is lower than 9V, gate drive high will be within 0.5V of  $V_{CC}$  and gate drive low within 1V of ground.

Important features include shutdown, current limit, softstart, synchronization and low quiescent current.

#### **Burst Mode Operation**

The LTC3824 can be configured for Burst Mode operation to enhance light load efficiency (only 40µA quiescent current) and extend battery run time by leaving the SYNC/MODE pin open or pulling it higher than 2V. In this mode, when output load drops the loop control voltage  $V_{\rm C}$  also drops and when  $V_{\rm C}$  reaches approximately 0.9V at low duty cycle the LTC3824 goes into sleep mode with the switch turned off. During sleep mode the output voltage drops and  $V_{\rm C}$  rises up. When  $V_{\rm C}$  goes up to around 70mV the LTC3824 will turn on the switch and the burst cycle repeats. If the SYNC/MODE pin is grounded the Burst Mode operation will be disabled and the LTC3824 skips cycles at light load.

#### Oscillation Frequency Setting and Synchronization

The switching frequency of the LTC3824 can be set up to 600kHz by a resistor, R<sub>FRFO</sub>, from the R<sub>SFT</sub> pin to ground.

For 200kHz,  $R_{FREQ}$  = 392k. See the Switching Frequency vs  $R_{FREQ}$  graph in the Typical Performance Characteristics section. With a 100ns one-shot timer on-chip, the LTC3824 provides flexibility on the sync pulse width. The sync pulse threshold voltage level is about 1.2V.

#### **Short-Circuit Protection**

In normal operation when the output voltage is in regulation,  $V_{FB}$  is regulated to 0.8V. If the output is shorted to ground and  $V_{FB}$  drops below 0.5V the switching frequency will be reduced to 50kHz to allow the inductor current to discharge and prevent current runaway. Note that synchronization is enabled only when  $V_{FB}$  is above 0.5V.

#### **Soft-Start**

During soft-start, the voltage on the SS pin ( $V_{SS}$ ) is the reference voltage that controls the output voltage and the output ramps up following  $V_{SS}$ . The effective range of  $V_{SS}$  is from 0V to 0.8V. The typical time for the output to reach the programmed level is:

$$t_{SS} = \frac{C_{SS} \cdot 0.8V}{5uA}$$

where  $C_{SS}$  is the capacitor connected from the SS pin to GND.

If shutdown mode will be invoked after startup, it is recommended to connect a  $1M\Omega$  to  $10M\Omega$  resistor from SS to ground to reset the SS capacitor during shutdown. This ensures proper soft-start operation when exiting shutdown mode.

#### Overvoltage Protection

To achieve good output regulation in Burst Mode operation, an overvoltage comparator, OVP, with a threshold adaptive to the  $V_{\text{C}}$  voltage is used to monitor the FB voltage. In Burst Mode operation with low  $V_{\text{C}}$  voltage, the OVP threshold is approximately 2% above  $V_{\text{REF}}$  and the  $V_{\text{REF}}$  is also shifted lower by 2% to contain the output ripple and to keep output regulation constant. As output load increases, OVP threshold increases with  $V_{\text{C}}$  voltage to up to 8% above  $V_{\text{REF}}$ .

#### Shutdown Mode Quiescent Current

When the  $V_{C}$  pin is pulled down below 25mV the LTC3824 goes into micropower shutdown mode and only draws  $7\mu A$ .

For proper operation, shutdown mode should not be engaged again too soon after exiting shutdown mode. This minimum time is a function of  $C_{SS}$  and is calculated by  $t_{MIN} = 5.5e5 \cdot C_{SS}$ . For example, if  $C_{SS} = 0.1 \mu F$ , then a minimum of 55ms must elapse after exiting shutdown before engaging it again.

## **Output Voltage Programming**

With a 0.8V feedback reference voltage,  $V_{REF}$ , the output voltage,  $V_{OUT}$ , is programmed by a resistor divider as shown in the Block Diagram.

$$V_{OUT} = 0.8V (1 + R_{F1}/R_{F2})$$

## Current Sense Resistor $\ensuremath{R_{\text{S}}}$ and Current Limit

The maximum current the LTC3824 can deliver is determined by:

$$I_{OUT(MAX)} = 100 \text{mV/R}_S - I_{RIPPLE}/2$$

where 100mV is the internal 100mV threshold across  $V_{CC}$  and  $V_{SENSE}$ , and  $I_{RIPPLE}$  is the inductor peak-to-peak ripple current.  $R_S$  should be placed very close to the power switch with very short traces. Good kelvin sensing is required for accurate current limit.

3824fl

#### Inductor Selection

The maximum inductor current is determined by :

$$\begin{split} I_{L(MAX)} &= I_{OUT(MAX)} + \frac{I_{RIPPLE}}{2} \\ \text{where } I_{RIPPLE} &= \frac{(V_{IN} - V_{OUT}) \bullet D}{f \bullet L} \\ \text{and Duty Cycle D} &= \frac{V_{OUT} + V_{D}}{V_{IN} + V_{D}} \end{split}$$

$V_{\text{D}}$  is the catch diode D1 forward voltage and f is the switching frequency.

A small inductance will result in larger ripple current, output ripple voltage and also larger inductor core loss. An empirical starting point for the inductor ripple current is about 40% of maximum DC current.

$$L = \frac{(V_{IN} - V_{OUT}) \cdot D}{f \cdot 0.4 \cdot I_{OUT(MAX)}}$$

The saturation current level of the inductor should be sufficiently larger than  $I_{L(MAX)}$ .

#### **Power MOSFET Selection**

Important parameters for the power MOSFET include the drain-to-source breakdown voltage (BV<sub>DSS</sub>), the threshold voltage (V<sub>GS(TH)</sub>), the on-resistance (R<sub>DS(ON)</sub>) versus gate-to-source voltage, the gate-to-source and gate-to-drain charges (Q<sub>GS</sub> and Q<sub>GD</sub>, respectively), the maximum drain current (I<sub>D(MAX)</sub>) and the MOSFET's thermal resistance (R<sub>TH(JC)</sub>) and R<sub>TH(JA)</sub>.

The gate drive voltage is set by the 8V internal regulator. Consequently, at least 10V  $V_{GS}$  rated MOSFETs are required in high voltage applications.

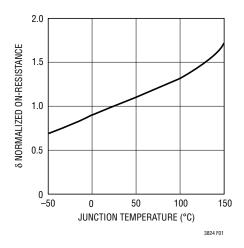

In order to calculate the junction temperature of the power MOSFET, the power dissipated by the device must be known. This power dissipation is a function of the duty cycle, the load current and the junction temperature itself (due to the positive temperature coefficient of  $R_{DS(ON)}$ ). The power dissipation calculation should be based on the worst-cast specifications for  $V_{SENSE(MAX)}$ , the required load current at maximum duty cycle, the voltage and temperature ranges, and the  $R_{DS(ON)}$  of the MOSFET listed in the data sheet.

The power dissipated by the MOSFET when the LTC3824 is in continuous mode is given by :

$$\begin{split} P_{\text{MOSFET}} &= \frac{V_{\text{OUT}+} V_{\text{D}}}{V_{\text{IN}} + V_{\text{D}}} (I_{\text{OUT}})^2 (1 + \delta) R_{\text{DS(ON)}} \\ &+ K(V_{\text{IN}})^2 (I_{\text{OUT}}) (C_{\text{RSS}}) (f) \end{split}$$

The first term in the equation represents the  $I^2R$  losses in the device and the second term is the switching losses. K (estimated as 1.7) is an empirical factor inversely related to the gate drive current and has the unit of 1/Amps. The  $\delta$  term accounts for the temperature coefficient of the  $R_{DS(ON)}$  of the MOSFET, which is typically 0.4%/°C.  $C_{RSS}$  is the MOSFET reverse transfer capacitance. Figure 1 illustrates the variation of normalized  $R_{DS(ON)}$  over temperature for a typical power MOSFET.

Figure 1. Normalized R<sub>DS(ON)</sub> vs Temperature

From a known power dissipated in the power MOSFET, its junction temperature can be obtained using the following formula:

$$T_J = T_A + P_{MOSFET} \cdot R_{TH(JA)}$$

The  $R_{TH(JA)}$  to be used in this equation normally includes the  $R_{TH(JC)}$  for the device plus the thermal resistance from the case to the ambient temperature ( $R_{TH(CA)}$ ). This value of  $T_J$  can then be compared to the original assumed value used in the calculation.

#### **Output Diode Selection**

The catch diode carries load current during the switch off-time. The average diode current is therefore dependent

3824ft

on the P-channel switch duty cycle. At high input voltages the diode conducts most of the time. As  $V_{\text{IN}}$  approaches  $V_{\text{OUT}}$  the diode conducts only a small fraction of the time. The worst condition for the diode is when the output is shorted to ground. Under this condition the diode must safely handle the maximum current at close to 100% of the time. Therefore, the diode must be carefully chosen to meet the worst case voltage and current requirements.

Under normal conditions, the average current conducted by the diode is:

$$I_D = I_{OLIT} \cdot (1 - D)$$

A fast switching Schottky diode must be used to optimize efficiency.

#### CIN and COLIT Selection

A low ESR input capacitor,  $C_{IN}$ , sized for the maximum RMS P-channel switch current is required to prevent large input voltage transients. The maximum RMS capacitor current is given by:

$$I_{RMS} = I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design.

The selection of  $C_{OUT}$  is determined by the effective series resistance (ESR) that is required to minimize voltage ripple and load step transients as well as the amount of bulk capacitance that is necessary to ensure that the control loop is stable.

The output ripple,  $\Delta V_{OUT}$ , is determined by:

$$\Delta V_{OUT} \le \Delta I_{L} \left( ESR + \frac{1}{8fC_{OUT}} \right)$$

The output ripple is highest at maximum input voltage since  $\Delta I_1$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR but have lower capacitance density than other types. Tantalum capacitors have the highest capacitance density but it is important to only use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR, but can be used in cost-sensitive applications provided that consideration is given to ripple current ratings and long-term reliability. Ceramic capacitors have excellent low ESR characteristics but can have a high voltage coefficient and audible noise.

#### **Efficiency Considerations**

The efficiency of a switching regulator is equal to the output power divided by the input power. Percentage efficiency can be expressed as:

where L1, L2, L3...are the individual loss components as a percentage of the input power. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Although all dissipative elements in the circuit produce losses, the following are the main sources:

1. The supply current into  $V_{CC}$ . The  $V_{CC}$  current is the sum of the DC supply current and the MOSFET driver and control currents. The DC supply current into the  $V_{CC}$  pin is typically about 1mA. The driver current results from switching the gate capacitance of the power MOSFET; this current is typically much larger than the DC current. Each time the MOSFET is switched on and off, a packet of gate charge  $Q_G$  is transferred from the CAP pin to  $V_{CC}$  throughout the external bypass capacitor,  $C_{CAP}$ . The resulting dQ/dt is a current that must be supplied to the capacitor by the internal regulator.

$$I_Q = 1mA + f \cdot Q_G$$

$P_{IC} = V_{IN} \cdot I_O$

2. Power MOSFET switching and conduction losses:

$$P_{MOSFET} = \frac{V_{OUT} + V_{D}}{V_{IN} + V_{D}} (I_{OUT})^{2} (1 + \delta) R_{DS(ON)}$$

$$+ K(V_{IN})^{2} (I_{OUT}) (C_{RSS}) (f)$$

3. The I<sup>2</sup>R losses of the current sense resistor:

$$P_{(SENSE R)} = (I_{OUT})^2 \cdot R \cdot D$$

where D is the duty cycle

4. The inductor loss due to winding resistance:

$$P_{(WINDING)} = (I_{OUT})^2 \cdot R_W$$

5. Loss of the catch diode:

$$P_{(DIODE)} = I_{OUT} \cdot V_D \cdot (1-D)$$

6. Other losses, including  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  ESR dissipation and inductor core losses, generally account for less than 2% of total losses.

#### **PCB Layout Considerations**

To achieve best performance from a LTC3824 circuit, the PC board layout must be carefully designed. For lower power applications, a 2-layer PC board is sufficient. However, at higher power levels, a multiple layer PC board is recommended. Using a solid ground plane under the circuit is the easiest way to ensure that switching noise does not affect the operation.

In order to help dissipate the power from the MOSFET and diode, keep the ground plane on the layers closest to the layers where power components are mounted. Use power planes for the MOSFET and diode in order to improve the spreading of heat from these components into the PCB.

For best electrical performance the LTC3824 circuit should be laid out as following:

Place all power components in a tight area. This will minimize the size of high current loops. Orient the input and output capacitors and current sense resistor in a way that minimizes the distance between the pads connected to ground plane.

Place the LTC3824 and associated components tightly together and next to the section with power components.

Use a local via to ground plane for all pads that connect to ground. Use multiple vias for power components.

Connect the current sense input directly to the current sense resistor pad.  $V_{CC}$  and SENSE are the inputs of the internal current sense amplifier and should be connected as close to the sense resistor pads as possible. A 100pF capacitor is required across the  $V_{CC}$  and sense pins for noise filtering and should be placed as close to the pins as possible.

#### **Design Example**

As an example, the LTC3824 is designed for an automotive 5V power supply with the following specifications:

Maximum  $I_{OUT} = 2A$ , typical  $V_{IN} = 6V$  to 18V and can reach 60V briefly during load dump condition, and operating switching frequency = 400kHz.

For f = 400kHz,  $R_{SFT}$  is chosen to be 180k.

Allow inductor ripple current to be 0.8A (40% of the maximum output current) at  $V_{IN} = 18V$ ,

$$L = \frac{(18V - 5V)5V}{(400kHz \cdot 0.8A)18V} = 12\mu H$$

$C_{OUT}$  will be selected based on the ESR that is required to satisfy the output voltage ripple requirement and the bulk capacitance needed for loop stability. For this design a 220µF tantalum capacitor is used.

For worse-case conditions  $C_{IN}$  should be rated for at least 1A ripple current (half of the maximum output current). A 47 $\mu$ F tantalum capacitor is adequate.

A current limit of 3.3A is selected and  $R_{\text{SENSE}}$  can be calculated by :

$$R_{SENSE} = \frac{100mV}{3.3A} = 0.03\Omega$$

and a  $25m\Omega$  resistor can be used.

LINEAR TECHNOLOGY

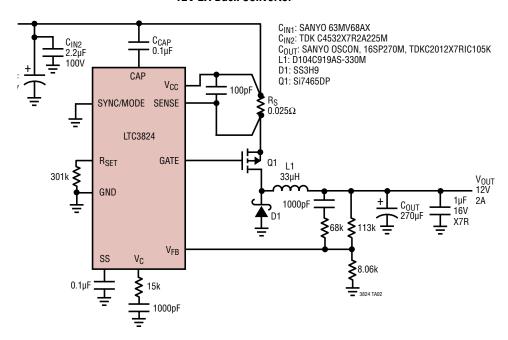

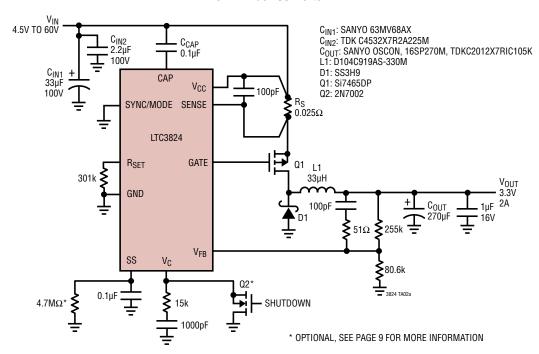

# TYPICAL APPLICATION

#### **12V 2A Buck Converter**

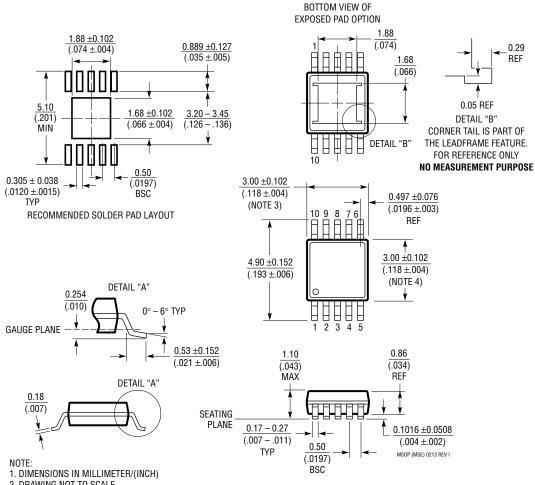

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LTC3824#packaging for the most recent package drawings.

#### **MSE Package** 10-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1664 Rev I)

- 2. DRAWING NOT TO SCALE

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

- 6. EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

# **REVISION HISTORY** (Revision history begins at Rev F)

| REV | DATE  | DESCRIPTION                                                  | PAGE NUMBER |

|-----|-------|--------------------------------------------------------------|-------------|

| F   | 12/10 | E-grade Ordering Information updated to 125°C                | 2           |

|     |       | EC header corrected to Operation <i>Junction</i> Temperature | 2           |

|     |       | Updated/corrected Note 2                                     | 3           |

|     |       | Updated Block Diagram                                        | 7           |

|     |       | Shutdown section updated                                     | 8           |

|     |       | Package updated                                              | 12          |

|     |       | Related Parts updated per Marketing request                  | 14          |

| G   | 3/11  | Updated Temperature Range for MP-grade part                  | 2           |

|     |       | Added LTC3824MP to Electrical Characteristics tables         | 2, 3        |

|     |       | Updated Note 2                                               | 3           |

|     |       | Updated Typical Application                                  | 14          |

| Н   | 01/16 | Updated soft-start and ground pin descriptions               | 6           |

|     |       | Block Diagram updated                                        | 7           |

|     |       | Added additional shutdown mode application information       | 9           |

|     |       | Revised schematic                                            | 16          |

# TYPICAL APPLICATION

#### **3V 2A Buck Converter**

# **RELATED PARTS**

| PART NUMBER                               | DESCRIPTION                                                                                                    | COMMENTS                                                                                                                                                              |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3864                                   | 60V Low I <sub>Q</sub> Step-Down DC/DC Controller with 100% Duty Cycle Capability                              | $3.5V \le V_{IN} \le 60V,~0.8V \le V_{OUT} \le V_{IN},~I_Q = 40\mu A,~Selectable~Fixed~Frequency~50kHz~to~850kHz,~3mm~×~4mm~DFN-12,~MSOP-12E$                         |

| LTC3891                                   | 60V, Low IQ, Synchronous Step-Down DC/DC Controller                                                            | $4V \le V_{IN} \le 60V$ , $0.8V \le V_{OUT} \le 24V$ , $I_Q = 50\mu A$ , Phase-Lockable Fixed Frequency 50kHz to 900kHz, $3x4$ QFN-20                                 |

| LTC3892/LTC3892-1                         | 60V, Low I <sub>Q</sub> , Dual 2-Phase Synchronous Step-Down<br>DC/DC Controller with Adj Gate Drive Voltage   | $ \begin{array}{l} 4.5V \leq V_{IN} \leq 60V, \ 0.8V \leq V_{OUT} \leq 0.99 V_{IN}, \ I_Q = 29 \mu A, \\ PLL \ Fixed \ Frequency \ 50kHz \ to \ 900kHz, \end{array} $ |

| LTC3890/LTC3890-1/<br>LTC3890-2/LTC3890-3 | 60V, Low I <sub>Q</sub> , Dual 2-Phase Synchronous<br>Step-Down DC/DC Controller with Fixed Gate Drive Voltage | $4V \le V_{IN} \le 60V$ , $0.8V \le V_{OUT} \le 24V$ , $I_Q = 50\mu A$ , PLL Fixed Frequency 50kHz to 900kHz                                                          |

| LT3845A                                   | 60V, Low I <sub>Q</sub> , Single Output Synchronous<br>Step-Down DC/DC Controller                              | $4V \le V_{IN} \le 60V$ , 1.23V $\le V_{OUT} \le 36V$ , $I_Q = 120\mu A$ , Synchronizable Fixed Frequency 100kHz to 600kHz, TSSOP-16                                  |

| LT3840                                    | 60V Wide Input Range Synchronous Regulator Controller Integrated Buck-Boost Supply for 7.5V MOSFET Gate Drive  | $2.5V \le V_{IN} \le 60V$ , $1.23V \le V_{OUT} \le 60V$ , $I_Q = 120\mu A$ , Synchronizable Fixed Frequency 50kHz to 1MHz, TSSOP-28, 4x6 QFN-38                       |

| LTC7860                                   | High Efficiency Switching Surge Stopper                                                                        | High Efficiency V <sub>OUT</sub> Clamp Stops High Voltage Input Surges, MSOP-12E                                                                                      |

| LTC3886                                   | 60V Dual Output Step-Down Controller with Digital Power System Management                                      | $4.5V \le V_{IN} \le 60V$ , $0.5V \le V_{OUT0,1}$ (±0.5%) $\le 13.8V$ , 70mS Start-Up, $I^2C$ /PMBus Interface, Input Current Sense                                   |

| LTC3810                                   | 100V Synchronous Step-Down DC/DC Controller                                                                    | Constant On-time Valley Current Mode $4V \le V_{IN} \le 60V$ , $0.8V \le V_{OUT} \le 0.93V_{IN}$ , SSOP-28                                                            |

| LTC3638                                   | High Efficiency, 140V 250mA Step-Down Regulator with Adjustable 20mA to 250mA Maximum Output Current           | $4V \le V_{IN} \le 140V, \ 0.8V \le V_{OUT} \le V_{IN}, \ I_Q = 12\mu A,$ No Compensation Required, MSOP-16E (12)                                                     |

| LTC7138                                   | High Efficiency, 140V 400mA Step-Down Regulator with Adjustable 100mA to 400mA Maximum Output Current          | $4V \le V_{IN} \le 140V$ , $0.8V \le V_{OUT} \le V_{IN}$ , $I_Q = 12\mu A$ , MSOP-16(12)<br>No Compensation Required, MSOP-16E (12)                                   |

LT 0116 REV H • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2006